Marktgröße und -anteil für Feld programmierbar Tor Array (FPGA)

Feld programmierbar Tor Array (FPGA) Marktanalyse von Mordor Intelligenz

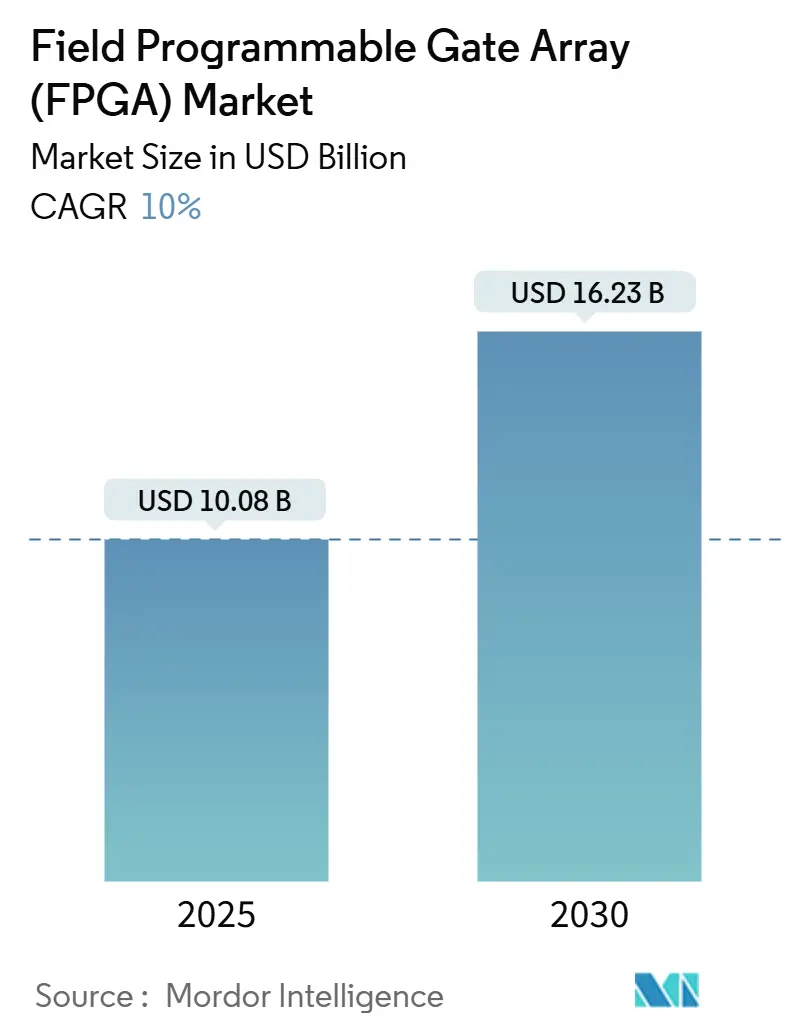

Die Marktgröße für Feld programmierbar Tor Array erreichte USD 10,08 Milliarden im Jahr 2025 und wird voraussichtlich auf USD 16,23 Milliarden bis 2030 bei einer CAGR von 10,00% expandieren. Die schnelle Einführung von Rand-KI-Inferenz In Hyperscale Rechenzentren, die Migration zu 5 g Open Radio-Architekturen und der steigende Bedarf an Post-Deployment-Rekonfigurierbarkeit In der Automobil- und Luft- und Raumfahrtelektronik verliehen dem Markt deutliche Dynamik.[1]AMD, "From Invention Zu KI Acceleration," amd.com hoch-End-Geräte bildeten weiterhin das Fundament der Einnahmen, doch Mid-Bereich- und niedrig-End-Produkte stiegen schnell an, da Designteams FPGA-Technologie In kostensensitive Industrie-, IoT- und Verbrauchersysteme einführten. Asien-Pazifik entwickelte sich sowohl zur größten Fertigungsbasis als auch zum am schnellsten wachsenden Nachfragezentrum und profitierte von Elektrofahrzeug-Antriebssträngen und neu-Raum-Konstellationen. Die Wettbewerbsintensität erhöhte sich, nachdem Intel zustimmte, Altera auszugliedern, was die Lieferantendynamik umgestaltete, während Exportkontrollen parallele inländische Entwicklung In China anspornten. Engere 300-mm-Foundry-Kapazitäten und der kostspielige Übergang zu ≤16 nm Knoten zwangen Anbieter auch dazu, hochmargige Anwendungen und langfristige Waffel-Reservierungen bei TSMC und Samsung zu priorisieren.

Wichtige Erkenntnisse des Berichts

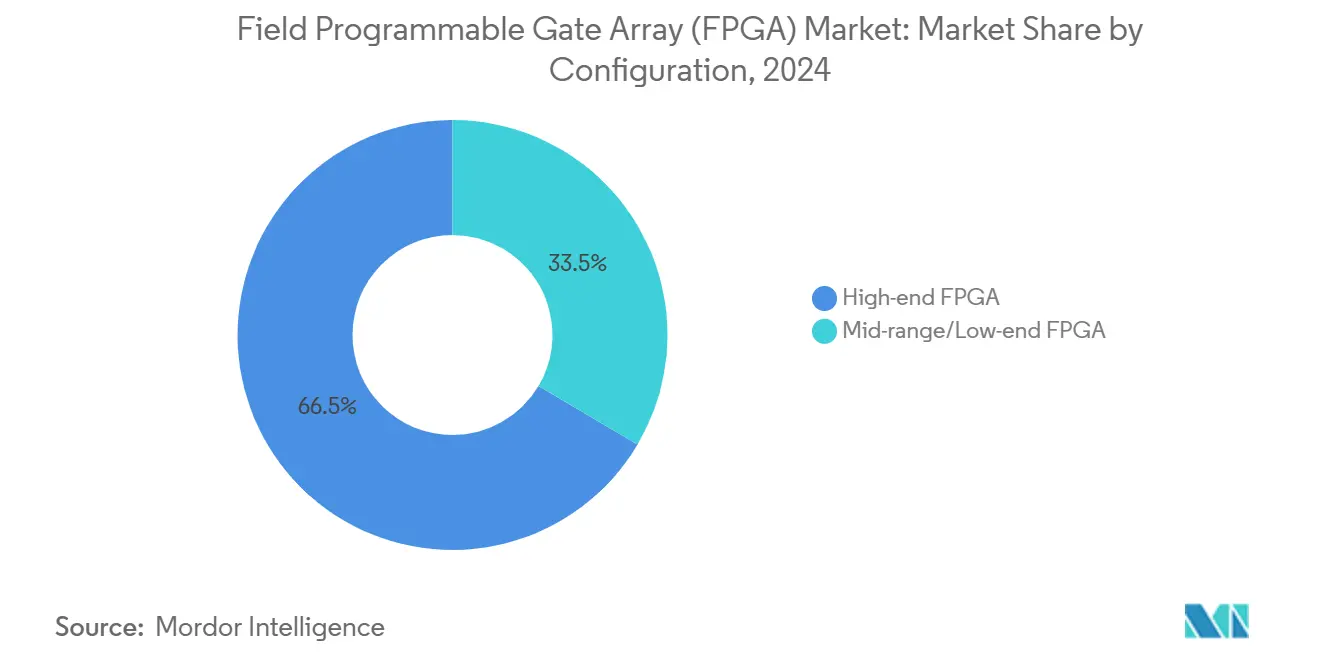

- Nach Konfiguration führten hoch-End-Geräte mit 66,5% des Feld programmierbar Tor Array Marktanteils im Jahr 2024, während Mid-Bereich- und niedrig-End-Geräte voraussichtlich mit 11,2% CAGR bis 2030 wachsen werden.

- Nach Architektur hielten SRAM-basierte Geräte 55,4% Umsatzanteil im Jahr 2024; Blitz-basierte Angebote werden voraussichtlich das schnellste Wachstum aufgrund niedrigerer statischer Leistungsbudgets verzeichnen.

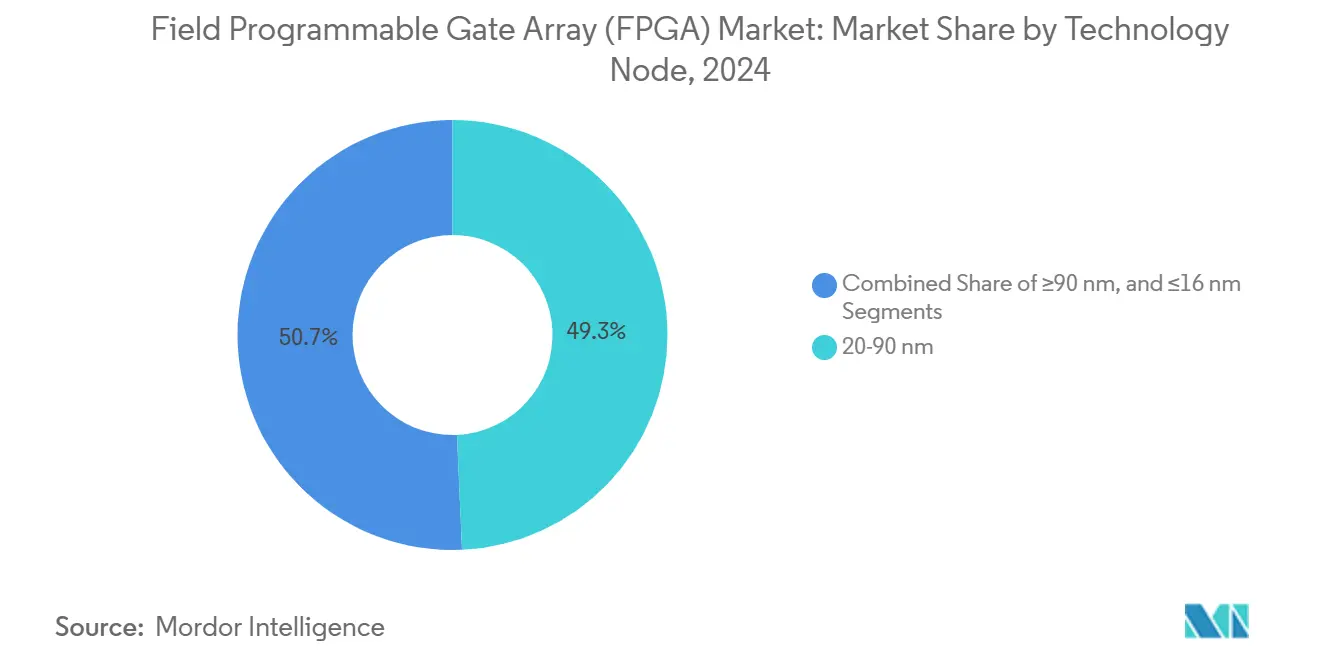

- Nach Technologieknoten beherrschte das 20-90 nm Segment 49,3% der Feld programmierbar Tor Array Marktgröße im Jahr 2024, während das ≤16 nm Segment voraussichtlich mit 15,1% CAGR zwischen 2025-2030 voranschreiten wird.

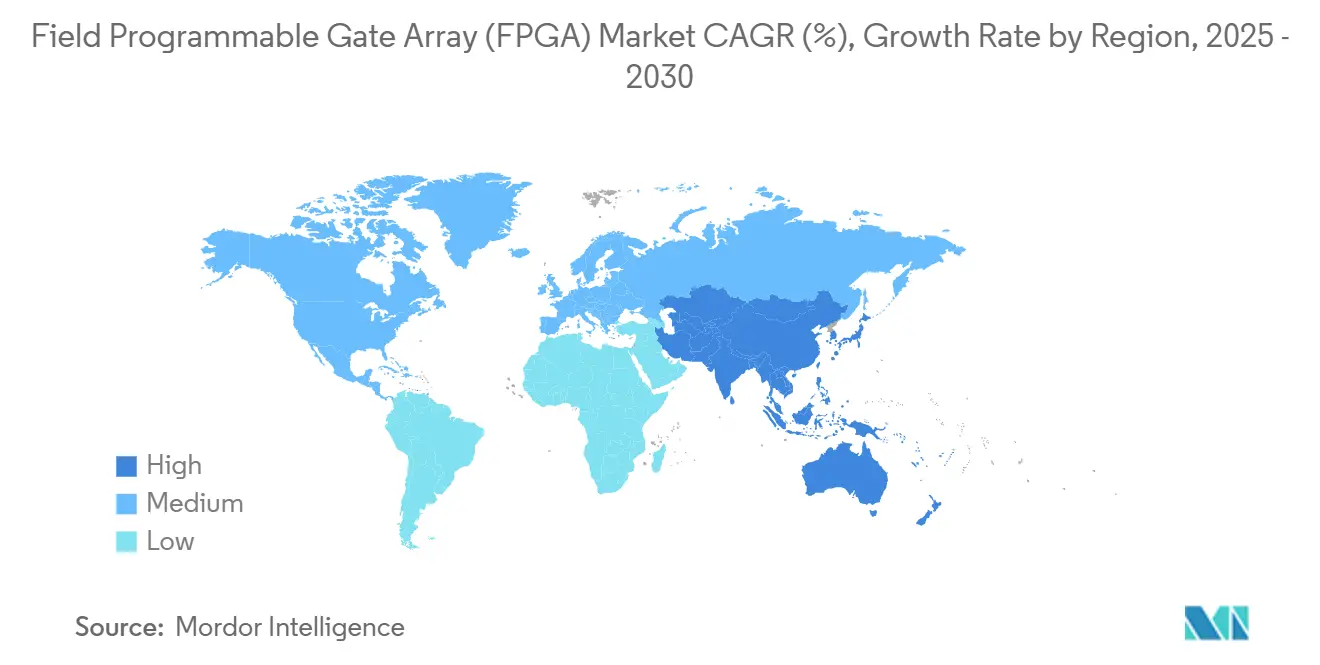

- Nach Geografie entfielen auf Asien-Pazifik 39,3% der Einnahmen im Jahr 2024 und es wird eine Expansion mit 17,1% CAGR bis 2030 erwartet.

- Nach Endmarkt eroberten Rechenzentrum- und Wolke-Anwendungen 29,2% der Feld programmierbar Tor Array Marktgröße im Jahr 2024; Automobil ADAS und Elektrifizierung soll mit 13,4% CAGR bis 2030 expandieren.

Globale Feld programmierbar Tor Array (FPGA) Markttrends und Einblicke

Treiber-Impact-Analyse

| Treiber | (~) % Impact auf CAGR-Prognose | Geografische Relevanz | Impact-Zeitrahmen |

|---|---|---|---|

| Rand-KI-Inferenz-Nachfrage In Hyperscale Rechenzentren | +2.8% | Global, konzentriert In Nordamerika und APAC | Mittelfristig (2-4 Jahre) |

| 5 g ORAN-Wechsel erfordert umprogrammierbare Logik In Radios | +2.1% | Global, angeführt von Nordamerika, Europa, APAC | Mittelfristig (2-4 Jahre) |

| Schnell Prototyping-Bedarf für ASIC/SoC-Schrumpfungszyklen (≤7 nm) | +1.7% | Global, konzentriert In Nordamerika und APAC | Kurzfristig (≤ 2 Jahre) |

| Funktionale Sicherheitscompliance im Automobilbereich (ISO 26262) | +1.4% | Global, angeführt von Europa, Nordamerika, China | Langfristig (≥ 4 Jahre) |

| Strahlungstolerante Designs für neu-Raum-Konstellationen | +0.9% | Global, angeführt von Nordamerika, Europa | Langfristig (≥ 4 Jahre) |

| Chinesische ev-Antriebsstrang-OEMs übernehmen eFPGAs für Motorsteuerung | +0.6% | APAC, hauptsächlich China | Mittelfristig (2-4 Jahre) |

| Quelle: Mordor Intelligence | |||

Edge-AI-Inferenz-Nachfrage in hyperscale Rechenzentren

Hyperscale-Betreiber setzten FPGAs ein, um KI-Inferenz zu beschleunigen, sobald Latenz- und Leistungsbudgets die reinen Durchsatzanforderungen übertrafen. AMDs Versal KI Rand Gen 2 Geräte lieferten bis zu 3× höhere TOPS pro Watt als erste Generation Teile und ermöglichten Echtzeit-Vision-Analytik bei gleichzeitiger Eindämmung der Betriebskosten. Achronix berichtete über 200% Kosten- und Leistungsvorteile gegenüber GPU-Alternativen beim Betrieb Großer Sprachmodelle, was die FPGA-Effizienz In speicherbegrenzten Arbeitslasten unterstrich. Diese Verschiebung erschloss ein verteiltes Berechnung-Modell, bei dem die Inferenz-Verarbeitung näher an Datenquellen rückte, was Bandbreitenbeschränkungen und Datensouveränitätsrisiken verringerte. Die Integration von An-Package HBM und gehärteten KI-Motoren innerhalb führender FPGA-Familien stärkte ihre Position In Wolke-Rand-Topologien. Folglich fand der Feld programmierbar Tor Array Markt eine dauerhafte Wachstumssäule In Hyperscale Investitionsplänen.

5G ORAN-Wechsel erfordert umprogrammierbare Logik in Radios

Open Radio Zugang Netzwerk-Initiativen drängten Netzbetreiber dazu, herstellerunabhängige Funkeinheiten zu übernehmen, die sich mit Software-Updates weiterentwickeln konnten anstatt mit Gabelstapler-Ersetzungen. Intels Agilex-Portfolio nutzte 10 nm SuperFin-Technologie, um softwaredefinierte Radios zu liefern, die sich an neue 5 g-Releases bei niedrigeren Gesamtbetriebskosten anpassen. Lattice Halbleiter ergänzte diese Hardware mit einem Referenz-Stack, der Null-Trust-Sicherheit und Echtzeit-Verschlüsselung für disaggregierte Netzwerke bereitstellt. AMDs Zynq RFSoC DFE verdoppelte die Leistung pro Watt gegenüber früheren Geräten und ermöglichte es Betreibern, mehrere-Band-Betrieb In kompakten, leistungsbeschränkten Funkköpfen zu unterstützen. Flexibel Logik verkürzte Rollout-Zyklen, ein kritischer Faktor, da Betreiber Privat 5 g-, Fest-Drahtlos-Zugang- und mmWave-Dienstleistungen mischten. Diese Flexibilität sicherte eine neue Volumen-Gelegenheit für den Feld programmierbar Tor Array Markt In der Telekom-Infrastruktur.

Rapid Prototyping-Bedarf für ASIC/SoC-Schrumpfungszyklen (≤7 nm)

Die Zeit zwischen neuen Prozesseinführungen fiel unter 24 Monate, was die Strafe für Design-Fehltritte erhöhte. Vor der Bestellung von Masken, die mehr als USD 10 Millionen bei 3 nm kosten, nutzten Chip-Teams Große FPGAs zur Validierung von Timing-, Leistungs- und Schnittstellenverhalten. Achronix lieferte Speedster7t-Geräte auf TSMC 7 nm, die mehrere-Terabit-Bandbreite für realistische Emulation der nächsten Generation von SoCs bereitstellen. TSMCs kommender A16 Tor-alle-Around-Knoten versprach weitere 10% Leistungssteigerung und 20% niedrigere Leistung, erhöhte jedoch auch die Verifizierungskomplexität und zementierte FPGA-Plattformen als Risikoreduzierungstools während des Tape-outs. Die Praxis verbreitete sich über Server-Klasse-Beschleuniger hinaus In gemischt-Signal-Automobil- und Industrie-ASICs und erweiterte den Feld programmierbar Tor Array Markt-Fußabdruck innerhalb von Halbleiter-Design-Flows.

Funktionale Sicherheitscompliance im Automobilbereich (ISO 26262)

Erweiterte Fahrerassistenz- und Elektrofahrzeug-Antriebsstränge erforderten Echtzeit-, deterministische Kontrolle, die das ASIL D Integritätsziel erfüllte. AMD stellte TÜV SÜD-zertifizierte Design-Flows und IP bereit, die die Entwicklungszeit reduzierten und gleichzeitig ISO 26262- und IEC 61508-Mandate erfüllten. Microchips Libero SoC Suite trug analoge TÜV Rheinland-Zertifikate über PolarFire- und SmartFusion 2-Familien und gab Tier-Ones eine zweite Quelle für sicherheitskritische Logik. Subaru wählte Versal KI Rand Gen 2 für die nächste Generation EyeSight Vision aus und verstärkte das OEM-Vertrauen In Adaptiv Computer für missionskritische Wahrnehmung. Lange Produktlebenszyklen In der Automobilindustrie multiplizieren die Lebenszeit-Einnahmen pro Design-Gewinn und unterstützen die langfristige Expansion des Feld programmierbar Tor Array Marktes.

Beschränkungen-Impact-Analyse

| Beschränkung | (~) % Impact auf CAGR-Prognose | Geografische Relevanz | Impact-Zeitrahmen |

|---|---|---|---|

| uns-EU-Exportkontrollen für Hochleistungs-FPGAs nach China | -1.8% | Global, konzentrierte Auswirkung auf China-uns-Handel | Kurzfristig (≤ 2 Jahre) |

| Volatilität In 300 mm Foundry-Kapazitätszuteilung | -1.2% | Global, konzentriert In APAC-Foundry-Hubs | Mittelfristig (2-4 Jahre) |

| Höherer statischer Stromverbrauch vs. dedizierte ASIC | -0.7% | Global, über alle Endmärkte | Langfristig (≥ 4 Jahre) |

| Quelle: Mordor Intelligence | |||

US-EU-Exportkontrollen für Hochleistungs-FPGAs nach China

Neue Bureau von Branche Und Sicherheit-Regeln entfernten zivile Ausnahmen für erweiterte FPGA-Lieferungen nach China Ende 2023 und beschränkten Geräte, die für KI- oder militärische Verwendung geeignet sind.[2]Federal Register, "Additional Export Bedienelemente," federalregister.gov Die Verschiebung zwang AMD-Xilinx und Intel-Altera dazu, viele Bestellungen zu stoppen oder Lizenz-zu-screenen, was kurzfristige Stückzahlen reduzierte. Chinesische Anbieter wie GOWIN und Pango suchten die Lücke zu schließen, doch Hürden bei Design-Werkzeuge, IP und erweiterten Prozesszugang begrenzten sofortige Substitution. Multinationale Kunden verlagerten sensible Produktion weg von China oder redesignten Systeme zur Qualifizierung nicht-uns-amerikanischer Geräte, was zuvor globale Lieferketten fragmentierte. Die resultierende Unsicherheit belastete den Feld programmierbar Tor Array Markt bis neue Handelsnormen sich stabilisierten.

Volatilität in 300 mm Foundry-Kapazitätszuteilung

Erweiterte FPGA-Fertigung ist bei TSMC und Samsung konzentriert, deren Kapazitätsentscheidungen oft hochvolumige Smartphone-APs oder GPU-Beschleuniger bevorzugten. Als KI-Chip-Nachfrage anstieg, verengten sich Waffel-Slots für mittelvolumige FPGA-Produkte und Vorlaufzeiten verlängerten sich. Anbieter platzierten mehrjährige Einlagen oder suchten Sekundärquellen, was Betriebskapitalbedarf erhöhte. Terminrisiken komplizierten Produkteinführungs-Roadmaps für Automobil- und Industriekunden, die langfristige Verfügbarkeit benötigen. Obwohl beide Foundries aggressive Expansion ankündigten, hielten Yield-Lernen bei neuen Knoten und geopolitische Standortwahl die Versorgung fragil und schufen eine persistente Beschränkung für den Feld programmierbar Tor Array Markt.

Segment-Analyse

Nach Konfiguration: High-End-Dominanz steht unter Kostendruck

hoch-End-Geräte hielten 66,5% des Feld programmierbar Tor Array Marktanteils im Jahr 2024 und spiegelten ihre zentrale Rolle In Rechenzentrum-Beschleunigung und 5 g-Infrastruktur wider. Diese Plattformen, oft über 1 Million Logikzellen hinausgehend, trugen Prämie-ASPs, lieferten jedoch deterministische Latenz, die In GPUs nicht verfügbar ist, und bewahrten ihre Attraktivität für sicherheitskritische Luft- und Raumfahrt- und Fintech-Arbeitslasten. Mid-Bereich- und niedrig-End-Geräte zeigten eine 11,2% CAGR bis 2030, da Hersteller wie Lattice kostenoptimierte Teile mit gehärteten KI-Motoren lieferten, die Rand-Compute-Budgets erfüllten. Design-Werkzeuge sind intuitiver geworden und ermöglichen es eingebetteten Ingenieuren, konfigurierbare Logik ohne Hardware-Hintergründe zu übernehmen.

Das Wertversprechen entwickelte sich, als AMD Spartan UltraScale+ mit 30% niedrigerer Leistung und unvergleichlicher I/O-Anzahl einführte und den Mid-Bereich von oben angriff. Gleichzeitig lieferten Modul-Anbieter vorvalidierte Boards, die Pin-Planung und Leiterplatte-Layout abstrahierten und Design-Zyklen verkürzten. Diese Verschiebungen werden voraussichtlich die Preis-Lücke zwischen Tiers komprimieren, obwohl hoch-End-Geräte immer noch eine Mehrheit der Feld programmierbar Tor Array Marktgröße beherrschen, wenn neue KI- oder Netzwerkstandards entstehen, die nur Spitze-Knoten-Silizium erfüllen kann.

Nach Architektur: SRAM-Suprematie durch Energieeffizienz herausgefordert

SRAM-basierte Lösungen besaßen 55,4% Umsatz im Jahr 2024 und verzeichneten einen 11,8% CAGR-Ausblick dank unbegrenzter Umprogrammierungszyklen und einem tiefen Software-Ökosystem. Doch Blitz-basierte Varianten gewannen Mindshare In Wearables und Automobil-Telematik, wo sofort-An-Verhalten lebenswichtig ist. Microchips RT PolarFire erreichte MIL-Standard-883 Klasse B und bot 50% niedrigere Leistung als äquivalente SRAM-Teile bei gleichzeitiger Tolerierung von 100 krad Strahlung. Anti-Fuse-Plattformen erhielten eine Nische In Verteidigungs-Avionik, wo einmalige Programmierbarkeit Manipulationsrisiko eliminiert.

Software-Portabilität schrumpft historische Barrieren, sodass Designer jetzt basierend auf Leistung und Sicherheit wählen können anstatt auf Tool-Vertrautheit. Aufkommende heterogene Architekturen integrieren SRAM-Fabric mit An-Die-nicht-Flüchtig-Domains und bieten die besten beider Optionen. Während SRAM-Geräte weiterhin die Feld programmierbar Tor Array Markt-Einnahmen anführen werden, sollten Blitz- und Anti-Fuse-Angebote größere Anteile In niedrig-Strom- und rauen Umgebungsbereitstellungen erobern.

Nach Technologieknoten: Erweiterte Knoten treiben Innovation voran

Die 20-90 nm Klasse hielt 49,3% Feld programmierbar Tor Array Marktanteil im Jahr 2024 und balancierte Yield-Reife und Kosten. Jedoch ist die ≤16 nm Kategorie auf Kurs für 15,1% CAGR, da KI-Inferenz, kohärente Interconnects und 112G SerDes Logikdichte erfordern, die nur erweiterte Knoten bieten können. AMD migrierte ausgewählte Spartan- und Versal-Linien zu 16 nm, um Kosteneffizienz mit modernen Transceivern zu mischen. TSMCs A16 Tor-alle-Around-Roadmap verspricht eine weitere Kerbe In Leistung pro Watt, die Anbieter für PCIe 6.0- und CXL 3.1-fähige Produkte zu nutzen planen.

Bei ≥90 nm bevorzugen Legacy-Industriesteuerungen und militärische Nachrüstungen stabile Lieferketten gegenüber roher Geschwindigkeit und halten diesen Knoten am Leben, obwohl er schrumpft. Der Übergang unter 10 nm fügt Masken- und EDA-Kostenlasten hinzu, die nur die größten Anbieter schultern können, was Wettbewerbsschwellen erhöht. Diese Dynamik könnte den Feld programmierbar Tor Array Markt um Spieler mit der Größe konsolidieren, um teure Waffel zu sichern und wiederverwendbare Software-Stacks zu entwickeln.

Nach Endmarkt: Automobil-Elektrifizierung beschleunigt Adoption

Rechenzentrum- und Wolke-Betreiber eroberten 29,2% der Feld programmierbar Tor Array Marktgröße im Jahr 2024 durch Nutzung rekonfigurierbarer Beschleuniger für KI-Inferenz und Netzwerkvirtualisierung. Automobil Anwendungen, einschließlich ADAS-Vision und Wechselrichtersteuerung, werden voraussichtlich mit 13,4% CAGR bis 2030 steigen, da OEMs konfigurierbare Logik einbetten, um sich schnell entwickelnde Sicherheits- und Motorsteueralgorithmen zu erfüllen. Achronix' eingebettete FPGA-IP ermöglicht es Autoherstellern, späte Funktionen zu benutzerdefinierten SoCs hinzuzufügen, eine Flexibilität, die innerhalb langer Fahrzeugplattformen hoch geschätzt wird.

Telekommunikation blieb lebhaft wegen Open RAN-Radios, die mehrere-Band-Agilität suchten. Industrielle Automatisierung und Robotik verließen sich auf deterministische Motorsteuerungsschleifen, wo FPGAs Legacy-DSPs ersetzten. Luft- und Raumfahrt- und Verteidigungswachstum konzentrierte sich auf strahlungstolerante Logik für niedrig-Erde-Orbit-Satelliten. Wearables, Testinstrumentierung und medizinische Bildgebung repräsentierten jüngere Vertikale, die von niedrig-Strom-personalisierten Computern profitieren. Die Breite der Verwendungen unterstreicht, dass der Feld programmierbar Tor Array Markt weiterhin über zyklische makroökonomische Umgebungen hinweg expandiert.

Geografie-Analyse

Asien-Pazifik dominierte den Feld programmierbar Tor Array Markt mit 39,3% Umsatz im Jahr 2024 und zeigte einen 17,1% CAGR-Ausblick bis 2030. Chinas Drang nach Halbleiter-Selbstständigkeit, hervorgehoben durch inländische Innovatoren In Elektrofahrzeug-Antrieben und Satelliten-Nutzlasten, zog erhebliche FPGA-Volumen an. Taiwan und Südkorea lieferten erweiterte Fertigung, während Japan sich auf Automobil-Modul und Fabrikautomatisierungs-Subsysteme spezialisierte. Indiens Design-Dienstleistung-Sektor entwickelte sich nach Lattices Eröffnung eines F&e-Zentrums In Pune weiter und erweiterte Ingenieurtalent-Pools.[3]Lattice Halbleiter, "Full Year 2024 Results," latticesemi.com

Nordamerika behielt die Führung In Rechenzentrum-Infrastruktur, hochzuverlässiger Luft- und Raumfahrt und EDA-Software. Hyperscaler lenkten Große Kapitalbudgets auf Adaptiv Beschleuniger, um KI-Dienstleistung-Kosten zu verwalten und sicherten den starken Kaufanteil der Region. Exportlizenz-Reviews formten Lieferungsmuster, aber spornten auch inländische Investitionen In erweiterte Verpackung und OSAT-Kapazität an, die den Feld programmierbar Tor Array Markt unterstützt.

Europa lehnte sich an Deutschlands Automobil-Lieferkette und nordische Telekom-Ausrüstungsanbieter. ISO 26262-Einhaltung spornte Fahrzeug-interne Nutzung an, während Energiewende-Projekte Nachfrage nach verlustarmen Leistungswandlern schufen. EU digital Decade-Richtlinien ermutigten souveräne Rand-Berechnung-Plattformen, die Rekonfigurierbarkeit bevorzugen. Obwohl Südamerika und der Nahe Osten und Afrika heute kleinere Anteile halten, sollte Wachstumspotential In 5 g-Infrastruktur und industrieller Modernisierung ihren Beitrag über den Prognosezeitraum steigern.

Wettbewerbslandschaft

Der Feld programmierbar Tor Array Markt blieb konzentriert, mit AMD-Xilinx und Intel-Altera, die immer noch die Mehrheit der Einnahmen im Jahr 2024 generierten. Intels Entscheidung im April 2025, 51% von Altera für USD 8,75 Milliarden an Silver Lake zu verkaufen, zielte darauf ab, eigenständige Investitionen zu beschleunigen und den Fokus auf hoch-End-Beschleunigungssegmente zu schärfen. AMD feierte 40 Jahre FPGA-Lieferungen und hob mehr als 3 Milliarden kumulative Einheiten hervor, wobei seine Versal- und Spartan-Familien genutzt wurden, um sowohl Rand-KI- als auch sicherheitskritische Bettürfnisse zu erfüllen.

Lattice Halbleiter gewann Traktion mit niedrig-Strom-Nexus- und Avant-Plattformen und sicherte sich Rekord-Design-Gewinne In generativer KI und Robotik. Achronix eroberte Anteil In eingebetteter FPGA-IP und mehrere-Terabit-Netzwerken, während Microchip seine Präsenz durch die Übernahme von Neuronix KI Labs stärkte, um sparsity-bewusst neuronale Netzwerke auf PolarFire-Geräten zu optimieren.[4]Microchip Technologie, "Acquires Neuronix KI Labs," microchip.com Schnell Silizium und andere Start-Ups führten Open-Source-Toolchains ein und setzten Legacy-Design-Suites unter Preisdruck.

Strategische Allianzen wurden wichtiger als Transistorzahlen allein. Lattice kollaborierte mit NVIDIA bei Referenz-Stacks für KI-Inferenz am Rand, und AMD hielt mit Vitis vereinheitlichten Programmierungsflows Schritt. Anbieter investierten auch In Chiplet-bereite Verpackung und UCIe-Interconnect-Standards, um Kunden zu ermöglichen, heterogene Systeme auf gemeinsamen Substraten zu montieren. Solche Ökosystem-Bewegungen werden voraussichtlich zukünftigen Erfolg im Feld programmierbar Tor Array Markt ebenso definieren wie rohe Logikdichte.

Feld programmierbar Tor Array (FPGA) Industrieführer

-

Fortgeschritten Mikro Geräte, Inc.

-

Lattice Halbleiter Corporation

-

QuickLogic Corporation

-

Intel Corporation

-

Achronix Halbleiter Corporation

- *Haftungsausschluss: Hauptakteure in keiner bestimmten Reihenfolge sortiert

Aktuelle Industrieentwicklungen

- Juni 2025: AMD feierte 40 Jahre FPGA-Innovation und verwies auf mehr als 3 Milliarden kumulative Lieferungen über Automobil- und Luft- und Raumfahrt-Rand-KI-Plattformen AMD.

- Mai 2025: Lattice Halbleiter berichtete Q1 2025 Umsatz von USD 120,1 Millionen mit Rekord-Design-Gewinnen In generativer KI, Robotik, Automobil-ADAS und Rand-KI.

- April 2025: Intel stimmte zu, 51% von Altera für USD 8,75 Milliarden an Silver Lake zu verkaufen und schuf den größten eigenständigen FPGA-Anbieter.

- März 2025: AMD führte die Spartan UltraScale+ Familie für kostensensitive Rand-Nutzung ein und verwies auf 30% niedrigere Leistung und klassenführende I/O.

Globaler Feld programmierbar Tor Array (FPGA) Marktbericht Umfang

FPGAs sind vorgefertigte Silizium-Instrumente, die elektrisch im Feld programmiert werden können, um fast jeden Typ digitaler Schaltung oder Systeme zu werden. Sie sind ein Array konfigurierbarer Logikblöcke (CLBs), die durch programmierbare Interconnects verbunden sind. Nach der Herstellung können sie umprogrammiert werden, um die Anforderungen der gewünschten Anwendung oder Funktionalität zu erfüllen.

Der Feld programmierbar Tor Array (FPGA) Markt ist segmentiert nach Konfiguration (hoch-End-FPGA, Mid-Bereich-FPGA/niedrig-End-FPGA), nach Architektur (SRAM-basierte FPGA, Anti-Fuse-basierte FPGA, Blitz-basierte FPGA), nach Endbenutzer-Industrie (Es und Telekommunikation, Verbraucherelektronik, Automobilbereich, Industrie, Militär und Luft- und Raumfahrt, andere Endbenutzer-Industrien), nach Geografie (Nordamerika [Vereinigte Staaten, Kanada], Europa [Deutschland, Vereinigtes Königreich, Frankreich, Rest Europas], Asien-Pazifik [China, Japan, Indien, Südkorea, Rest des Asien-Pazifiks], Lateinamerika [Brasilien, Argentinien, Mexiko, Rest Lateinamerikas], Naher Osten und Afrika [Vereinigte Arabische Emirate, Saudi-Arabien-Arabien, Südafrika, Rest des Nahen Ostens und Afrikas]). Die Marktgrößen und -prognosen werden In Bezug auf den Wert In USD für alle oben genannten Segmente bereitgestellt.

| High-End-FPGA |

| Mid-Range/Low-End-FPGA |

| SRAM-basierte FPGA |

| Flash-basierte FPGA |

| Anti-Fuse-FPGA |

| ≥90 nm |

| 20-90 nm |

| ≤16 nm |

| Rechenzentrum und Cloud Computing |

| Telekommunikation und 5G-Infrastruktur |

| Automobilbereich (ADAS, Elektrifizierung) |

| Industrielle Automatisierung und Robotik |

| Luft- und Raumfahrt und Verteidigung (Avionik, SATCOM) |

| Verbraucherelektronik und Wearables |

| Test-, Mess- und Medizingeräte |

| Nordamerika | Vereinigte Staaten | |

| Kanada | ||

| Europa | Deutschland | |

| Vereinigtes Königreich | ||

| Frankreich | ||

| Italien | ||

| Nordische Länder (Schweden, Norwegen, Finnland, Dänemark) | ||

| Rest Europas | ||

| Asien-Pazifik | China | |

| Taiwan | ||

| Japan | ||

| Südkorea | ||

| Indien | ||

| ASEAN | ||

| Rest des Asien-Pazifiks | ||

| Südamerika | Mexiko | |

| Brasilien | ||

| Argentinien | ||

| Rest Südamerikas | ||

| Naher Osten und Afrika | Naher Osten | Saudi-Arabien |

| Vereinigte Arabische Emirate | ||

| Türkei | ||

| Rest des Nahen Ostens | ||

| Afrika | Südafrika | |

| Rest Afrikas | ||

| Nach Konfiguration | High-End-FPGA | ||

| Mid-Range/Low-End-FPGA | |||

| Nach Architektur | SRAM-basierte FPGA | ||

| Flash-basierte FPGA | |||

| Anti-Fuse-FPGA | |||

| Nach Technologieknoten | ≥90 nm | ||

| 20-90 nm | |||

| ≤16 nm | |||

| Nach Endmarkt | Rechenzentrum und Cloud Computing | ||

| Telekommunikation und 5G-Infrastruktur | |||

| Automobilbereich (ADAS, Elektrifizierung) | |||

| Industrielle Automatisierung und Robotik | |||

| Luft- und Raumfahrt und Verteidigung (Avionik, SATCOM) | |||

| Verbraucherelektronik und Wearables | |||

| Test-, Mess- und Medizingeräte | |||

| Nach Geografie | Nordamerika | Vereinigte Staaten | |

| Kanada | |||

| Europa | Deutschland | ||

| Vereinigtes Königreich | |||

| Frankreich | |||

| Italien | |||

| Nordische Länder (Schweden, Norwegen, Finnland, Dänemark) | |||

| Rest Europas | |||

| Asien-Pazifik | China | ||

| Taiwan | |||

| Japan | |||

| Südkorea | |||

| Indien | |||

| ASEAN | |||

| Rest des Asien-Pazifiks | |||

| Südamerika | Mexiko | ||

| Brasilien | |||

| Argentinien | |||

| Rest Südamerikas | |||

| Naher Osten und Afrika | Naher Osten | Saudi-Arabien | |

| Vereinigte Arabische Emirate | |||

| Türkei | |||

| Rest des Nahen Ostens | |||

| Afrika | Südafrika | ||

| Rest Afrikas | |||

Wichtige im Bericht beantwortete Fragen

Wie hoch ist der aktuelle Wert des Feld programmierbar Tor Array Marktes?

Der Markt wurde auf USD 10,08 Milliarden im Jahr 2025 bewertet und wird voraussichtlich USD 16,23 Milliarden bis 2030 erreichen.

Welche Region wächst am schnellsten?

Asien-Pazifik wird voraussichtlich mit 17,1% CAGR bis 2030 expandieren aufgrund von Elektrofahrzeug-Antriebsstrang- und neu-Raum-Satelliten-Nachfrage.

Warum werden FPGAs für Rand-KI-Inferenz bevorzugt?

Sie liefern höhere Leistung pro Watt und deterministische Latenz gegenüber GPUs, was die Gesamtbetriebskosten für Hyperscale Betreiber verbessert.

Wie werden Exportkontrollen den Markt beeinflussen?

uns-EU-Beschränkungen für Hochleistungsgeräte nach China könnten kurzfristige Lieferungen reduzieren und chinesische Unternehmen dazu veranlassen, inländische Alternativen zu beschleunigen.

Welches Konfigurationssegment schreitet am schnellsten voran?

Mid-Bereich- und niedrig-End-Geräte sind auf 11,2% CAGR eingestellt, da kostenoptimierte Plattformen Industrie- und IoT-Anwendungen erreichen.

Was ist die Bedeutung von ≤16 nm Prozessknoten für FPGAs?

Sie ermöglichen höhere Logikdichte und erweiterte Schnittstellen wie PCIe 6.0, die für KI-Inferenz und 5 g-Baseband-Verarbeitung kritisch sind.

Seite zuletzt aktualisiert am:

-Market-logo.webp)