Neural Processor Market Size and Share

Neural Processor Market Analysis by Mordor Intelligence

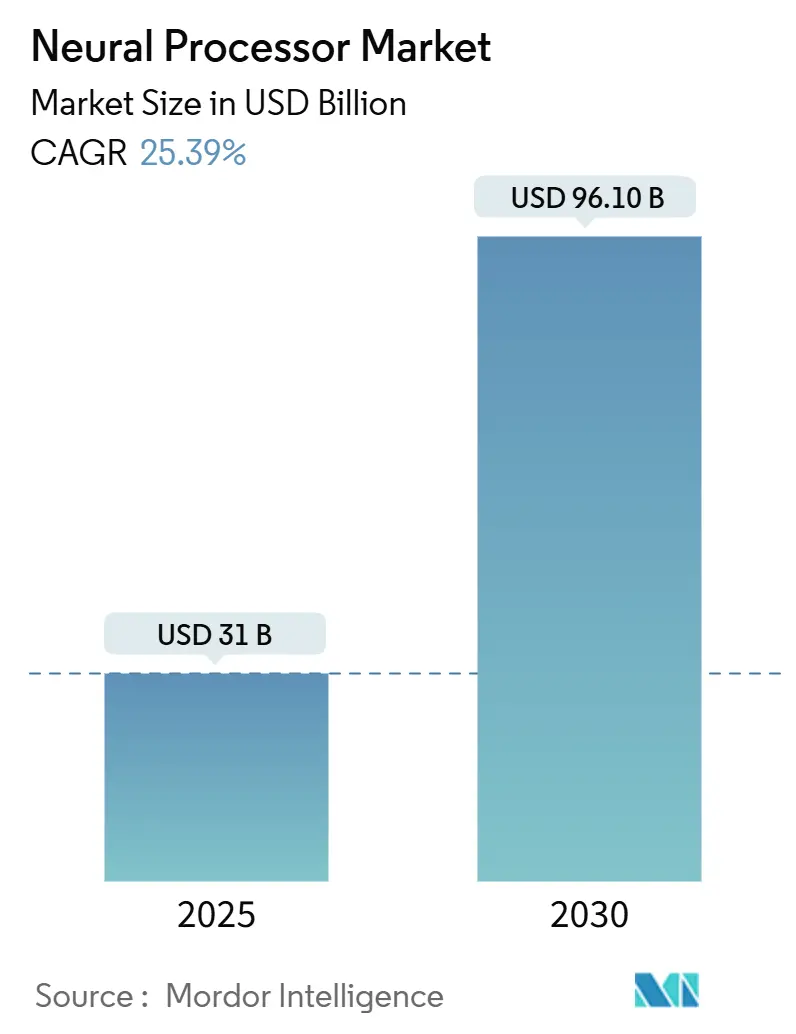

The global neural processor market is projected to grow significantly, with its valuation anticipated to increase from USD 31 billion in 2025 to USD 96.1 billion by 2030. This growth corresponds to a compound annual growth rate (CAGR) of 25.39%, reflecting the rising importance of specialized AI hardware in computing. A major factor driving this growth is the increasing demand from hyperscale data centers, which utilize high-performance neural processors to efficiently manage AI inference workloads, particularly for large datasets and real-time applications. In addition, national governments and regional alliances are implementing sovereign chip initiatives aimed at reducing reliance on foreign semiconductor supply chains and fostering domestic innovation. These initiatives are encouraging investments in neural processor design and fabrication, particularly in regions focused on achieving strategic autonomy in AI and digital infrastructure.

Key Report Takeaways

- By product type, edge NPUs captured 29.4% of the neural processor market size in incremental growth terms and are advancing at the fastest 29.4% CAGR to 2030, while data center NPUs maintained 51.6% neural processor market share in 2024.

- By architecture, GPUs are expected to sustain a 41.7% revenue dominance of the neural processor market in 2024; however, ASIC-based neural processors are anticipated to outpace them with a 26.7% CAGR through 2030.

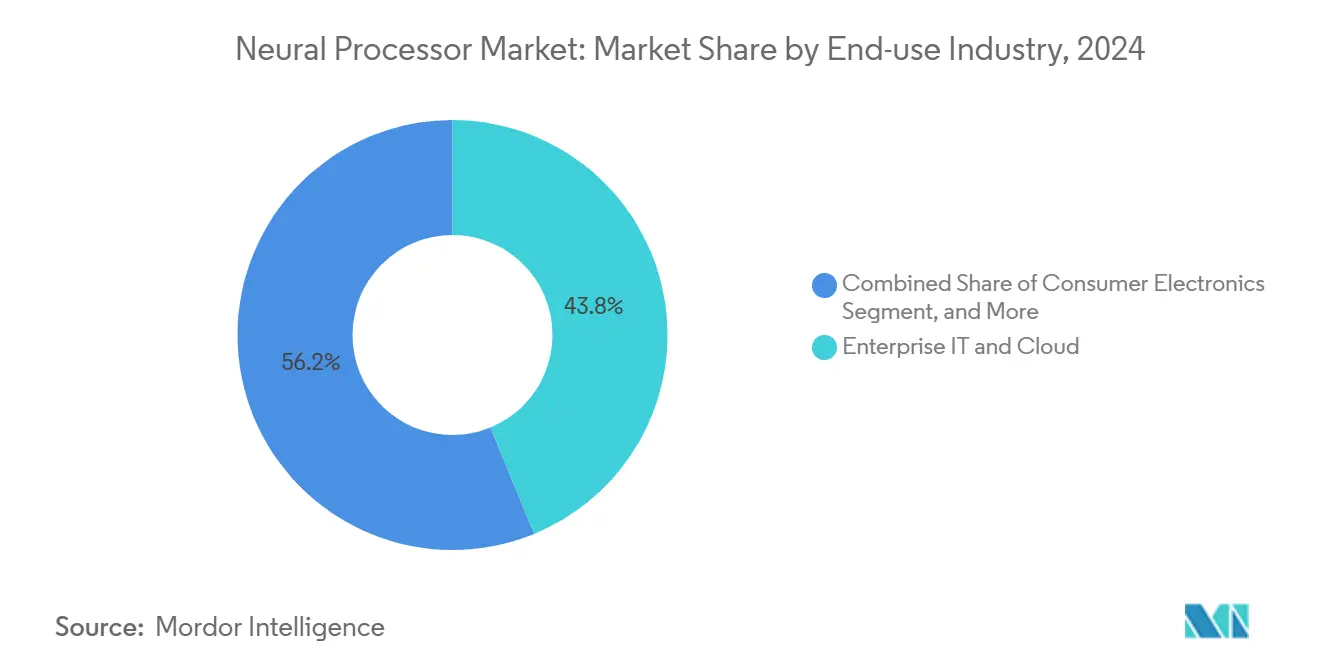

- By end-use industry, enterprise IT and cloud accounted for 43.8% of the neural processor market's revenue in 2024 and are expected to expand at a 28.1% CAGR, driven by investments from hyperscalers.

- By deployment mode, the cloud segment commanded a 58.7% share of the neural processor market in 2024, whereas edge and on-premise deployments are projected to rise at a 27.8% CAGR through 2030.

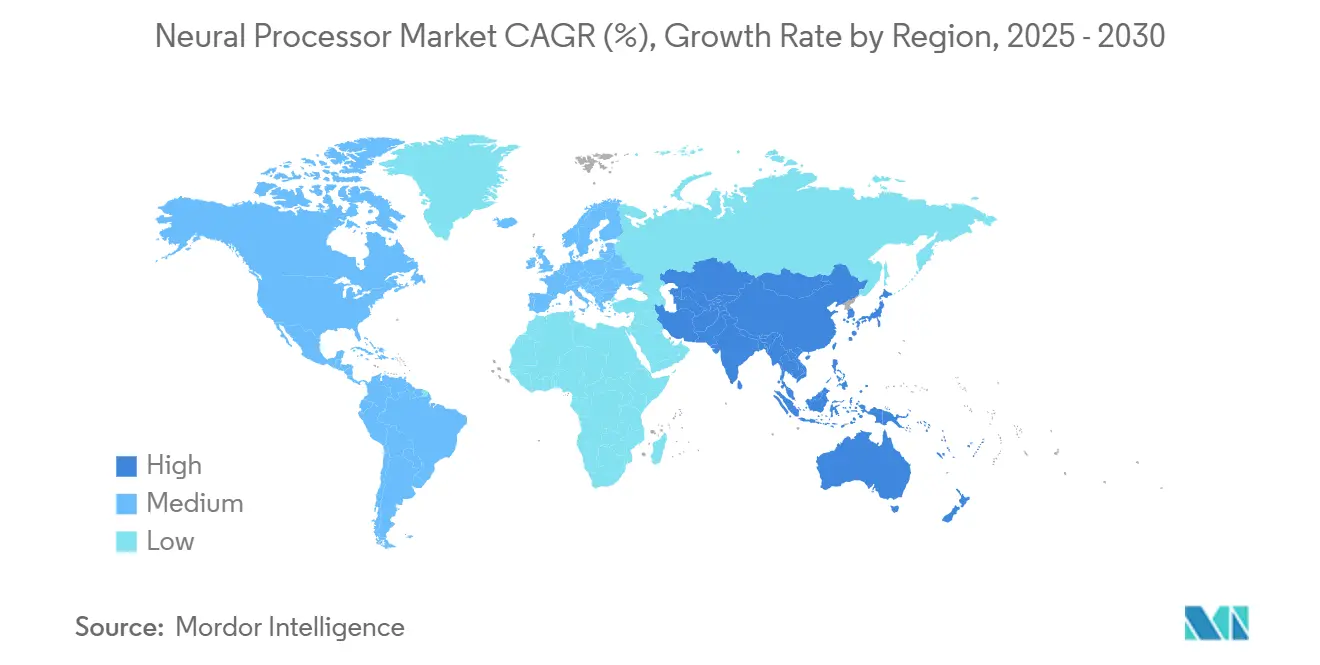

- By geography, the Asia-Pacific region is forecast to lead growth at a 30.07% CAGR due to state-backed semiconductor initiatives, despite North America’s 36.7% revenue of the neural processor market in 2024.

Global Neural Processor Market Trends and Insights

Drivers Impact Analysis

| DRIVER | (~) % IMPACT ON CAGR FORECAST | GEOGRAPHIC RELEVANCE | IMPACT TIMELINE |

|---|---|---|---|

| Accelerated AI Workloads in Data Centers | +6.2% | North America, Asia-Pacific | Medium term (2-4 years) |

| Proliferation of Edge AI in Consumer Devices | +5.8% | Asia-Pacific, Global | Short term (≤ 2 years) |

| Automotive ADAS and Autonomous Driving | +4.1% | North America, Europe | Long term (≥ 4 years) |

| Rising Demand for Energy-efficient AI | +3.9% | European Union, California | Medium term (2-4 years) |

| Open-source AI Framework Optimization | +2.7% | Global developer hubs | Short term (≤ 2 years) |

| National Semiconductor Self-sufficiency | +2.8% | Asia-Pacific, North America, Europe | Long term (≥ 4 years) |

| Source: Mordor Intelligence | |||

Accelerated AI Workloads in Data Centers

Data center operators are swapping general-purpose GPUs for task-tuned NPUs that shave 40-60% off total cost of ownership for large language model inference, as illustrated by Amazon Inferentia and Google TPU deployments.[1]AWS Team, “Amazon Inferentia Performance Benchmarks,” Amazon Web Services, aws.amazon.com ASIC-based neural processors now ship in volume for deterministic latency and lower watt-hour costs, particularly for conversational AI and image generation services. Pandemic-era digitization exposed cloud bottlenecks, further justifying in-house silicon strategies among hyperscalers. Continuous inference workloads replace sporadic training demands, maintaining high utilization and reducing payback periods for custom accelerators. The trend stimulates the broader neural processor market as enterprises adopt AI-native SaaS offerings that ride on NPU-dense server racks.

Proliferation of Edge AI in Consumer Devices

Smartphone OEMs, PC vendors, and IoT device makers have shifted from experimental on-device AI to ubiquitous neural engines that enhance real-time experiences and protect user privacy. The Apple Neural Engine, Qualcomm AI Engine, and Google Tensor silicon demonstrate that even mid-range handsets now embed NPUs capable of 15+ TOPS at sub-2W envelopes.[2]Qualcomm Engineers, “AI Engine Technology Overview,” Qualcomm Technologies, qualcomm.com Data localization rules under the GDPR and similar statutes require sensitive inference workloads, such as biometric authentication or contextual voice commands, to be processed at the endpoint. Battery-friendly designs leveraging 5 nm and 3 nm nodes reduce heat while preserving all-day battery, making the neural processor market integral to consumer electronics roadmaps. This surge lifts unit shipments for edge-focused NPUs across Asia-Pacific contract manufacturers that supply global brands.

Automotive ADAS and Autonomous Driving Adoption

From Level 2 driver assistance to Level 3 conditional autonomy, vehicle electronics require exponential increases in sensor fusion computing. Tesla’s FSD computer integrates 144 TOPS of neural processing, while NVIDIA Drive Orin scales to 254 TOPS, both of which are qualified for automotive temperature grades.[3]Tesla Autopilot Group, “Full Self-Driving Computer Architecture,” Tesla Inc., tesla.com Edge inference with sub-50 ms latency is non-negotiable for safety, forcing OEMs to adopt specialized chips that comply with ISO 26262. As regulatory approval for hands-off highways expands across the U.S., Europe, and China, the content of neural processors per vehicle increases. OEMs hedge supply-chain risk by developing proprietary silicon or exclusive foundry slots, anchoring long-horizon demand in the neural processor market.

Rising Demand for Energy-Efficient AI Acceleration

Electricity tariffs and carbon reporting rules elevate performance per watt as the lead procurement metric. The European Union’s Energy Efficiency Directive now ties tax incentives to data-center PUE targets, pressing operators to install chips that deliver more inferences per joule.[4]European Commission Directorate-General for Energy, “Energy Efficiency Directive Implementation,” European Commission, ec.europa.eu Neuromorphic designs and SRAM-centric memory hierarchies enable more than 10× gains over legacy architectures in sparse workload scenarios. Hyperscalers negotiate power purchase agreements in renewable micro-grids, yet silicon efficiency remains central to cost models. Edge devices amplify this imperative: battery-restricted wearables and drones integrate NPUs with power consumption under 1 W, expanding the addressable neural processor market into low-power niches.

Restraints Impact Analysis

| RESTRAINT | (~) % IMPACT ON CAGR FORECAST | GEOGRAPHIC RELEVANCE | IMPACT TIMELINE |

|---|---|---|---|

| Geopolitical Export Controls on Advanced Nodes | -3.8% | China, Russia | Medium term (2-4 years) |

| High up-Front Design and Tape-out Costs | -2.9% | Global | Long term (≥ 4 years) |

| Talent Scarcity in Neuromorphic Design | -2.1% | U.S., Taiwan, Israel | Long term (≥ 4 years) |

| Fragmentation of Software Toolchains | -1.7% | Global | Short term (≤ 2 years) |

| Source: Mordor Intelligence | |||

Geopolitical Export Controls on Advanced Nodes

Expanded BIS rules in 2024 now cap the shipment of EUV scanners and design IP for sub-14 nm nodes to certain destinations, throttling capacity for high-end NPU fabs.[5]U.S. Department of Commerce Bureau of Industry and Security, “Export Control Updates for Semiconductor Technology,” commerce.gov Chinese firms redesign at 28 nm or rush to implement multi-chiplet constructs to sidestep embargoes, thereby inflating BOM costs. Fragmented technology stacks reduce global volume leverage, slowing the erosion of prices. Compliance audits consume research and development budgets, dampening the speed of architectural innovation.

High Up-Front Design and Tape-Out Costs

A 3nm neural processor tape-out can exceed USD 100 million, including EDA licenses and mask sets, according to TSMC's pricing sheets. Venture capitalists demand proven design-win pipelines before underwriting such sums, nudging startups toward older nodes or architecture licensing deals. Consequently, only capital-rich players or hyperscalers roll out new silicon every 18 months, which narrows supplier diversity and marginally tempers the growth of the neural processor market.

Segment Analysis

By Product Type: Edge NPUs Drive Distributed Intelligence

The edge NPU sub-segment added the highest incremental value in 2024 and is projected to scale at a 29.4% CAGR to 2030, reflecting demand for low-latency AI in smartphones, AR wearables, and smart vehicles. Data center NPUs still account for 51.6% of the neural processor market share due to large cluster deployments among hyperscalers. Over the forecast horizon, edge devices such as connected cameras, voice assistants, and industrial robots will embed compact NPUs that consume <2 W but deliver double-digit TOPS, sustaining unit shipment momentum. Vision processors remain a notable niche, favored by surveillance and ADAS integrators seeking deterministic frame-rate performance without placing a burden on the main CPU. AI system-on-chips bundle CPUs, GPUs, and NPUs on a single die, offering cost-optimized SKUs for mid-tier OEMs and expanding the neural processor market into price-sensitive segments.

Simultaneously, data center NPUs are evolving toward memory-centric architectures, exemplified by Intel's Gaudi2, which features reduced DRAM hop latency, and AMD's MI300X, which supports 192 GB HBM3 stacks. High-bandwidth interconnects enable multi-chiplet scaling, preserving throughput as model parameters swell into the multi-trillion range. Edge-to-cloud symmetry is emerging; model segments are trained in centralized clusters and later deployed as quantized variants on endpoint NPUs, stitching a continuous value chain that amplifies silicon lifecycle volumes across the neural processor market.

By Architecture: ASIC Optimization Challenges GPU Dominance

GPUs generated 41.7% of the revenue in 2024, owing to the mature CUDA and ROCm ecosystems that expedite software portability. Yet ASIC-based NPUs are predicted to secure a notable share, as they clock more than 2× the performance per watt for speech and vision inference at a comparable silicon area. Orders from Amazon, Google, and Meta signal confidence in fixed-function efficiency even at 5 nm and below. FPGA-based NPUs persist in the telecom and aerospace industries, where field reconfiguration can override power loss. Hybrid chiplet strategies combine general-purpose GPU tiles with NPU tiles within a shared package, utilizing high-density interposers to reduce memory copy penalties.

Although ASIC design cycles stretch to 24 months, hyperscalers accept the risk to avoid GPU scarcity and licensing fees. Their internal software teams port frameworks at the compiler level, abstracting hardware idiosyncrasies. Meanwhile, mid-market enterprises continue to rely on GPUs for ecosystem stability, ensuring a dual-track demand curve that maintains market diversity for neural processors.

By End-Use Industry: Enterprise IT Leads Across Metrics

In 2024, enterprise IT and cloud workloads contributed 43.8% of revenue and are forecast to grow at 28.1% CAGR, underpinned by SaaS AI rollouts in CRM, HR, and cybersecurity. Consumer electronics ranked second, buoyed by smartphone shipments that topped 1.3 billion units, which almost universally embed AI photography pipelines. Automotive ADAS shipments rise in tandem with safety mandates, resulting in sizable multi-year contracts for Tier-1 silicon suppliers.

Healthcare adoption accelerates as radiology departments deploy NPUs to enhance CT and MRI reconstruction speeds, shaving patient throughput times. Regulatory graveyards once slowed the development of AI medical devices, yet FDA fast-track clearances for AI-assisted diagnostics have improved. Industrial verticals integrate NPUs for closed-loop process control, driving predictive maintenance savings. Collectively, this demand gamut creates revenue stability, cushioning the neural processor market against downturns in any single sector.

By Deployment Mode: Edge Computing Accelerates

Cloud deployments still command 58.7% revenue share because training clusters scale vertically in centralized hyperscale data centers. However, on-premise and edge installations are accelerating at a 27.8% CAGR as enterprises mitigate latency and data-sovereignty risks. Banking and telecom firms run inference locally to comply with residency rules, while video analytics operators push compute into smart cameras to reduce backhaul bandwidth. Hybrid cloud control planes orchestrate these disaggregated resources, enabling model updates without re-training.

LLM distillation and sparsity techniques now enable sub-10B parameter models to run on 20 TOPS edge NPUs under 5W, opening up new workloads in retail kiosks and field robotics. Regulatory impetus, such as the EU AI Act, further stimulates the adoption of local-processing architectures. This ledger of compliance, cost, and user-experience drivers positions the distributed deployment tier as the fulcrum for growth in the neural processor market.

Geography Analysis

North America maintained a 36.7% revenue lead in 2024, driven by hyperscaler cluster expansions and robust venture funding for AI hardware startups. Federal CHIPS Act incentives lower capex hurdles for domestic fabs, anchoring future tape-outs at Arizona and Ohio sites. Silicon Valley maintains a dense talent reservoir, while auto-tech corridors in Texas and Michigan escalate demand for in-vehicle NPUs.

The Asia-Pacific region is advancing at a 30.07% CAGR, fueled by sovereign chip subsidies, the rollout of 5G, and colossal consumer electronics assembly capacity. China’s publicly funded semiconductor funds support local NPU startups, while South Korea’s foundries fast-track 3nm high-volume manufacturing. Japan partners with the U.S. on advanced packaging, accelerating heterogenous integration pivotal to next-gen neural processors.

Europe balances strict data-privacy rules with strategic autonomy ambitions. Germany’s automotive clusters pilot Level 3 self-driving and drive demand for functionally safe-certified NPUs. The EU’s Energy Efficiency Directive incentivizes power-optimized AI accelerators in regional colocation centers. Meanwhile, emerging markets in South America, the Middle East, and Africa adopt mature-node NPUs for telecom and mining automation, illustrating a phased diffusion that widens the neural processor market base.

Competitive Landscape

First-tier players, including NVIDIA, Intel, and AMD, retain broad developer mindshare through CUDA, OpenVINO, and ROCm. NVIDIA’s 2024 H200 GPU increased inference throughput by 40% over its predecessor, reaffirming its leadership in hosting large models. Intel announced USD 15 billion in new U.S. factories to fab its next-generation Gaudi accelerators, signaling its intent to vertically integrate. AMD counters with MI300X, marrying 24 chiplets under a 3D fabric to deliver record on-package memory.

Hyperscalers intensify competition by internalizing silicon. Google’s TPUv5 scales transformer inference; Amazon Inferentia2 underwrites economical AI service tiers; Meta unveils custom inference accelerators for ranking and recommendation engines. Their success pressures merchant silicon suppliers on price and roadmap agility.

Startups push architectural frontiers: Cerebras scales wafer-sized chips for models with over 20 trillion parameters; Graphcore’s bow-tie sparsity engines excel in irregular workloads; SambaNova packages reconfigurable data-flow cores with turnkey software. Fabrication partnerships and adjacent IP portfolios dictate survival. Patent filings for neuromorphic and in-memory computing peaked in 2024, foreshadowing a more heterogeneous neural processor market by the end of the decade.

Neural Processor Industry Leaders

Nvidia Corporation

Intel Corporation

Cerebras Systems Inc.

Graphcore Ltd.

Qualcomm Technologies, Inc.

- *Disclaimer: Major Players sorted in no particular order

Recent Industry Developments

- October 2024: Intel earmarked USD 15 billion for advanced neural processor fabs in Arizona and Ohio, targeting 2026 production ramps.

- September 2024: NVIDIA launched H200 Tensor Core GPU with HBM3e, raising large-language-model inference by 40%.

- August 2024: Qualcomm closed a USD 1.4 billion acquisition of Nuvia to boost automotive and edge AI roadmaps.

- May 2024: Samsung and Google partnered on custom cloud NPUs leveraging Samsung 3 nm foundry nodes.

Global Neural Processor Market Report Scope

| Edge Neural Processing Units (NPUs) |

| Data Center NPUs |

| Co-Processors and Accelerators |

| Vision Processors |

| AI System-on-Chip (SoC) |

| ASIC-Based NPUs |

| GPU-Based NPUs |

| FPGA-Based NPUs |

| Hybrid / Chiplet Architecture |

| Consumer Electronics |

| Automotive and Transportation |

| Healthcare and Life Sciences |

| Industrial and Manufacturing |

| Enterprise IT and Cloud |

| On-Premise / Edge |

| Cloud |

| North America | United States | |

| Canada | ||

| Mexico | ||

| South America | Brazil | |

| Argentina | ||

| Rest of South America | ||

| Europe | Germany | |

| United Kingdom | ||

| France | ||

| Italy | ||

| Spain | ||

| Russia | ||

| Rest of Europe | ||

| Asia-Pacific | China | |

| Japan | ||

| India | ||

| South Korea | ||

| South-East Asia | ||

| Rest of Asia-Pacific | ||

| Middle East and Africa | Middle East | Saudi Arabia |

| United Arab Emirates | ||

| Rest of Middle East | ||

| Africa | South Africa | |

| Egypt | ||

| Rest of Africa | ||

| By Product Type | Edge Neural Processing Units (NPUs) | ||

| Data Center NPUs | |||

| Co-Processors and Accelerators | |||

| Vision Processors | |||

| AI System-on-Chip (SoC) | |||

| By Architecture | ASIC-Based NPUs | ||

| GPU-Based NPUs | |||

| FPGA-Based NPUs | |||

| Hybrid / Chiplet Architecture | |||

| By End-Use Industry | Consumer Electronics | ||

| Automotive and Transportation | |||

| Healthcare and Life Sciences | |||

| Industrial and Manufacturing | |||

| Enterprise IT and Cloud | |||

| By Deployment Mode | On-Premise / Edge | ||

| Cloud | |||

| By Geography | North America | United States | |

| Canada | |||

| Mexico | |||

| South America | Brazil | ||

| Argentina | |||

| Rest of South America | |||

| Europe | Germany | ||

| United Kingdom | |||

| France | |||

| Italy | |||

| Spain | |||

| Russia | |||

| Rest of Europe | |||

| Asia-Pacific | China | ||

| Japan | |||

| India | |||

| South Korea | |||

| South-East Asia | |||

| Rest of Asia-Pacific | |||

| Middle East and Africa | Middle East | Saudi Arabia | |

| United Arab Emirates | |||

| Rest of Middle East | |||

| Africa | South Africa | ||

| Egypt | |||

| Rest of Africa | |||

Key Questions Answered in the Report

What is the current valuation of the neural processor market?

The neural processor market size is expected to reach USD 96.1 billion by 2030, up from USD 31 billion in 2025.

How fast is revenue growing?

The market is expanding at a robust 25.39% CAGR through 2030, driven by AI workload growth in both cloud and edge segments.

Which region is expanding the fastest?

Asia-Pacific is the fastest-growing geography, advancing at a 30.07% CAGR due to sovereign chip incentives and electronics manufacturing strength.

Which end-use segment dominates revenue?

Enterprise IT and cloud applications lead with 43.8% revenue share in 2024 and maintain the strongest 28.1% CAGR.

Are GPUs still dominant in neural processors?

GPUs hold 41.7% revenue share, but ASIC-based NPUs are closing the gap thanks to 26.7% CAGR on workload-specific efficiency gains.

What restrains faster growth?

Export controls on advanced nodes and high tape-out costs shave 3.8% and 2.9% off potential CAGR, respectively, moderating otherwise stronger expansion.

Page last updated on: