Edge AI Chips Market Size and Share

Edge AI Chips Market Analysis by Mordor Intelligence

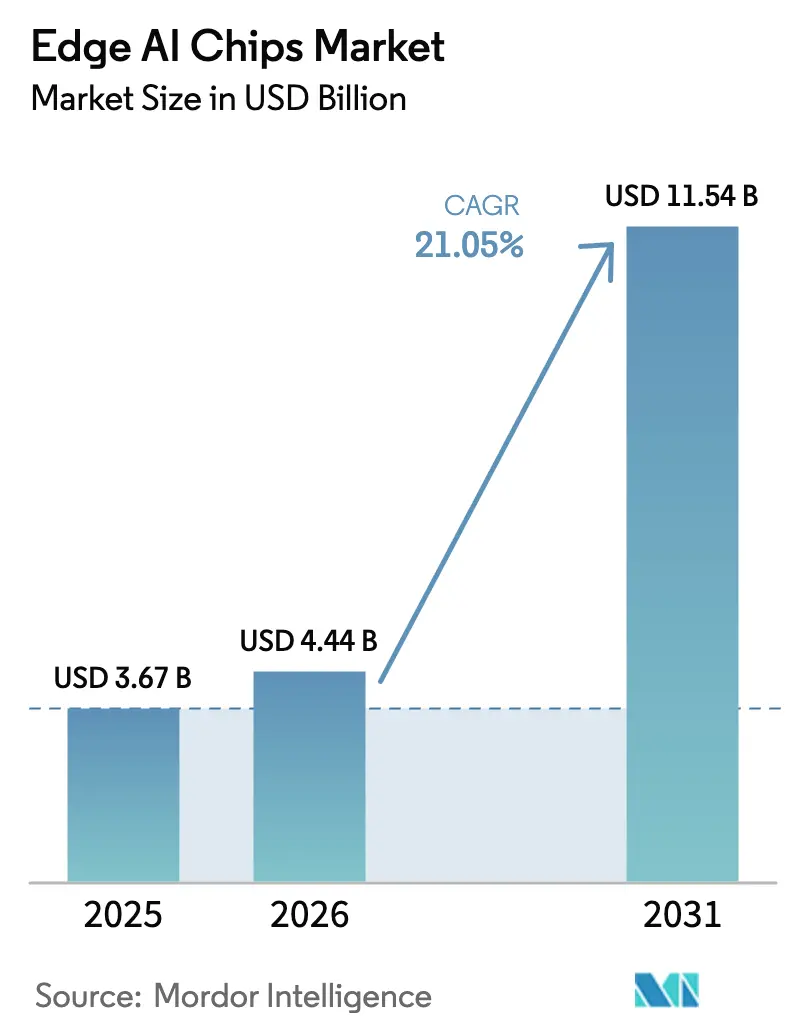

The Edge AI Chips market size was valued at USD 3.67 billion in 2025 and estimated to grow from USD 4.44 billion in 2026 to reach USD 11.54 billion by 2031, at a CAGR of 21.05% during the forecast period (2026-2031). Secular demand stems from distributed-intelligence architectures that shift inference workloads from centralized clouds to endpoints, a change encouraged by latency-sensitive use cases and by increasingly strict data-privacy regulations. Rapid node shrink below 5 nm, the addition of dedicated neural processing units, and improvements in software toolchains have collectively lowered energy per inference, widening the addressable opportunity across consumer, enterprise, and industrial domains. Regionally, government incentives that target domestic semiconductor sovereignty—especially in Asia-Pacific—have accelerated capacity expansions, while 5G rollout has enhanced the economic case for placing compute closer to data sources. Competitive intensity has therefore sharpened, with large incumbents integrating advanced packaging and chiplet designs to defend share and startups introducing domain-specific architectures to capture emerging workloads.

Key Report Takeaways

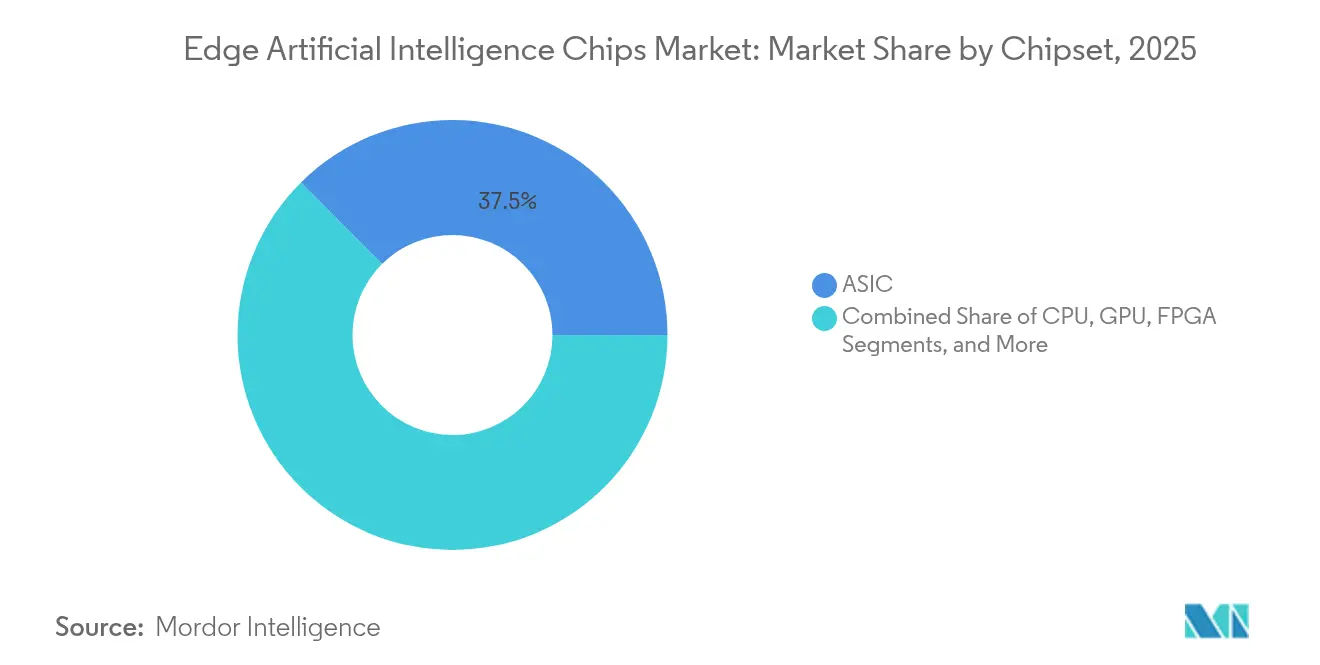

- By chipset, ASICs led with 37.45% revenue Edge AI Chips market share in 2025, while neuromorphic architectures are projected to post a 48.3% CAGR to 2031.

- By device category, consumer electronics contributed 44.20% of the 2025 Edge AI Chips market size, whereas enterprise/industrial devices are forecast to expand at a 24.1% CAGR through 2031.

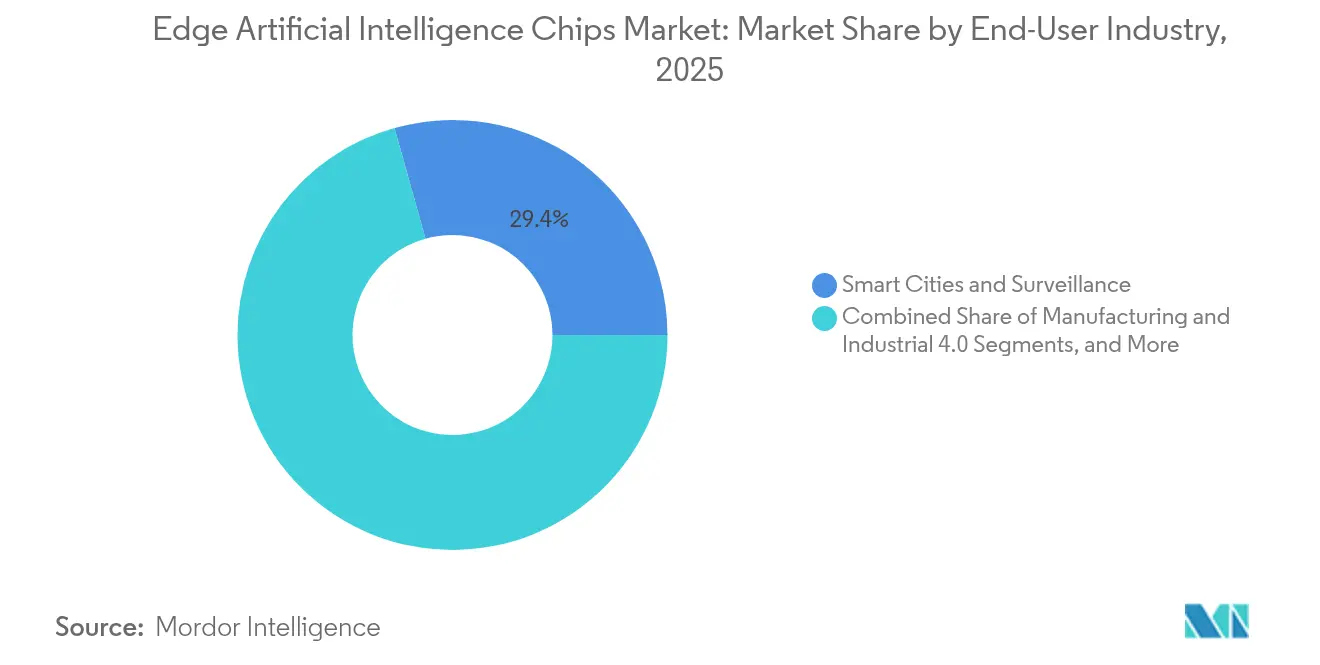

- By end-user industry, smart-city and surveillance systems held 29.35% of 2025 revenue; automotive and transportation applications are expected to advance at a 26.2% CAGR between 2026-2031.

- By process node, the ≥14 nm tier maintained a 39.20% share in 2025; the ≤5 nm tier is forecast to compound at a 55.4% CAGR through 2031.

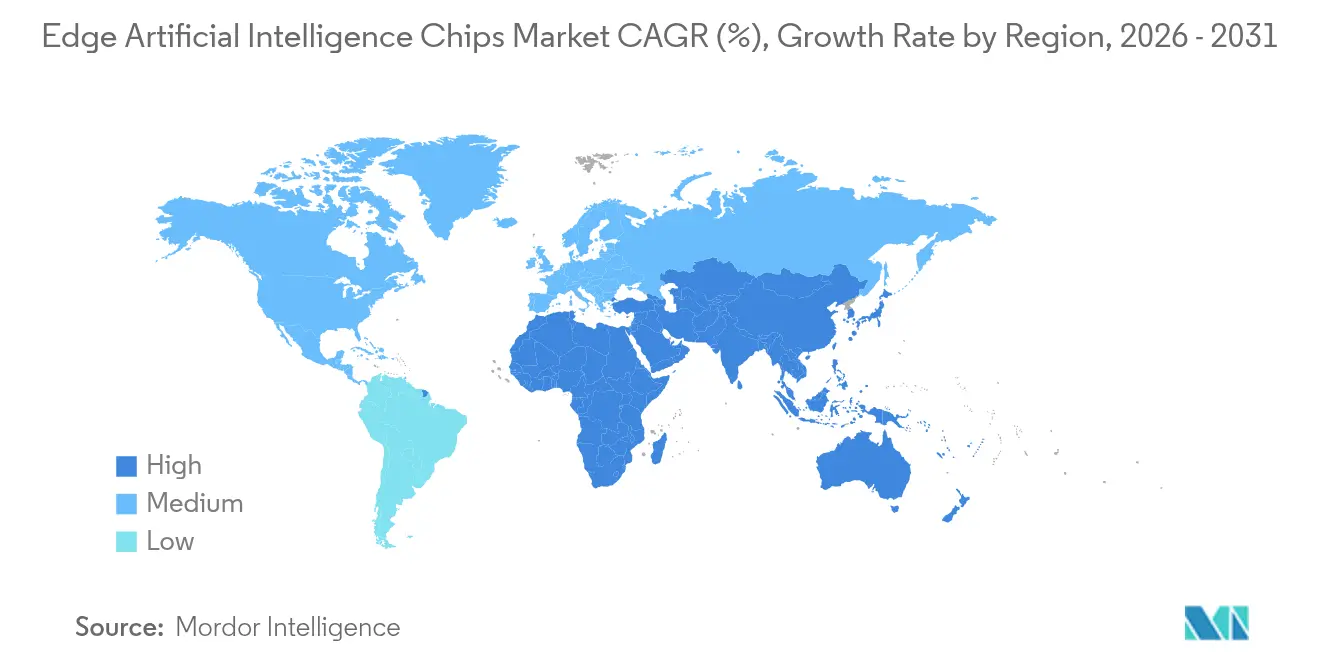

- By geography, Asia-Pacific dominated with 43.60% Edge AI Chips market share in 2025, while the Middle East and Africa is the fastest-growing region at a 22.4% CAGR for 2026-2031.

Note: Market size and forecast figures in this report are generated using Mordor Intelligence’s proprietary estimation framework, updated with the latest available data and insights as of 2026.

Global Edge AI Chips Market Trends and Insights

Drivers Impact Analysis*

| Driver | (~) % Impact on CAGR Forecast | Geographic Relevance | Impact Timeline |

|---|---|---|---|

| IoT-sensor data explosion | +3.2% | Global, with a concentration in Asia-Pacific manufacturing hubs | Medium term (2-4 years) |

| Privacy-preserving, low-latency inference | +5.4% | North America and the EU, with regulatory spillover to global markets | Short term (≤ 2 years) |

| Process-node shrink < 5 nm boosts TOPS/W | +6.5% | Asia-Pacific (Taiwan, South Korea), with global distribution | Medium term (2-4 years) |

| 5G-enabled distributed compute architectures | +4.3% | North America, Europe, and developed Asia-Pacific markets | Medium term (2-4 years) |

| Proliferation of TinyML in battery devices | +2.2% | Global, with early adoption in consumer electronics | Short term (≤ 2 years) |

| Source: Mordor Intelligence | |||

IoT-Sensor Data Explosion Drives Edge Processing Requirements

Installed IoT endpoints surpassed 29 billion in 2024, generating more than 73 zettabytes of data annually. Moving such volumes to centralized data centers proved both cost-prohibitive and latency-intolerant, prompting enterprises to embed inference locally. Industrial deployments documented network-traffic reductions of up to 95% after filtering data at the source, with Texas Instruments’ radar-sensor platform achieving an 87% bandwidth cut and a 76% response-time improvement.[1]Texas Instruments, “New Edge AI-Enabled Radar Sensor and Automotive Audio Processors,” ti.com Similar results were reported by smart-utility grids that now analyze vibration signatures inside transformers to trigger maintenance orders without cloud connectivity. These performance gains underpin continued expansion of the Edge AI Chips market across manufacturing, logistics, and utilities through the forecast horizon.

Privacy-Preserving, Low-Latency Inference Reshapes Deployment Models

Global regulations such as GDPR and California’s CCPA intensified fines for mishandling personally identifiable information, incentivizing on-device inference that keeps raw data local. Apple’s M4 processor processed speech models with 83% lower round-trip delay than cloud alternatives while guaranteeing in-device data retention, a benchmark that elevated consumer expectations. Hospitals, industrial safety systems, and telecom operators have since adopted similar frameworks, generating fresh demand for secure-enclave accelerators and bolstering the Edge AI Chips market position in regulated sectors.

Process-Node Shrink Below 5 nm Transforms Performance-Per-Watt Economics

TSMC’s 3 nm FinFET (N3) platform delivered a 70% logic density uplift and a 30% power reduction over 5 nm predecessors. Samsung’s gate-all-around variant added a further 45% power saving. These improvements lengthen battery runtimes in wearables, reduce cooling loads in fanless gateways, and permit larger model footprints inside fixed thermal envelopes. The resultant efficiency uptick expands deployment into retail shelf-scanners, uncrewed aerial vehicles, and autonomous inspection robots, collectively enlarging the Edge AI Chips market addressable base.

5G-Enabled Distributed Compute Architectures Create New Paradigms

Sub-10 ms air-interface latencies allow real-time workload allocation between on-device silicon, edge micro-data centers, and regional clouds. Telecom operators in the United States, Japan, and Germany now pilot network slices optimized for AI acceleration, enabling computer-vision tasks to shuttle seamlessly across strata. ZTE’s “Network + Computing + AI” stack deployed in GCC smart-city projects illustrated a 38% latency reduction at equivalent throughput. Such architectures elevate total silicon consumption per site, thereby magnifying revenue potential for the Edge AI Chips market.

Restraints Impact Analysis*

| Restraint | (~) % Impact on CAGR Forecast | Geographic Relevance | Impact Timeline |

|---|---|---|---|

| High design and tape-out costs | -3.2% | Global, with the highest impact on startups and smaller firms | Medium term (2-4 years) |

| Fragmented software stacks | -2.6% | Global, with particular impact on enterprise adoption | Short term (≤ 2 years) |

| Thermal limits in fanless edge form factors | -1.7% | Global, with higher impact in warmer climate regions | Medium term (2-4 years) |

| Export controls on advanced AI silicon | -1.1% | China, Russia, and restricted markets | Long term (≥ 4 years) |

| Source: Mordor Intelligence | |||

High Design and Tape-Out Costs Create Barriers to Entry

Designing a sub-5 nm accelerator can exceed USD 500 million, with each tape-out iteration costing roughly USD 30 million.[2]Modular, “Democratizing AI Compute Part 9: Why Hardware Companies Struggle,” modular.com Capital intensity favors incumbents, driving acquisition-led consolidation exemplified by NXP’s USD 307 million purchase of Kinara. Smaller innovators increasingly license IP blocks rather than pursue monolithic rollouts, but the financing gap still hinders the projected CAGR of the Edge AI Chips market.

Fragmented Software Stacks Impede Developer Adoption

Edge frameworks remain heterogeneous—ranging from vendor-specific toolchains to sparse open-source kernels—forcing developers to maintain multiple optimization pipelines. Lack of a CUDA-like standard means models must often be hand-tuned per silicon target, inflating project timelines for smart factories and connected-retail deployments. Enterprise procurement has therefore slowed in sectors requiring wide hardware interoperability, trimming near-term expansion in the Edge AI Chips market despite broader technological enthusiasm.

*Our updated forecasts treat driver/restraint impacts as directional, not additive. The revised impact forecasts reflect baseline growth, mix effects, and variable interactions.

Segment Analysis

By Chipset: ASIC Leadership Amid Neuromorphic Upsurge

ASICs accounted for 37.45% of 2025 revenue, validated by Google’s Edge TPU, which achieved 4 TOPS at 2 W, and by camera-centric SoCs that process multiple 4K video streams concurrently. Their deterministic data paths minimize latency and power draw, critical to surveillance and industrial-safety scenarios. Vendors integrate proprietary software kits that merge quantization, compilation, and runtime layers, encouraging ecosystem lock-in and elevating switching costs. As a result, ASIC roadmaps extend into multi-die packages that fuse NPUs with sensor hubs, further cementing leadership through domain-optimized silicon.

Neuromorphic architectures are projected to soar at a 48.3% CAGR to 2031 due to their brain-inspired event-driven design, which co-locates memory and compute. Intel’s Loihi 2 reported 10× lower power for spiking-neural networks used in always-on keyword spotting. Research consortia in Europe and Asia examine them for tactile robotics and autonomous-drone swarms, where micro-joule-level budgets govern viability. Though presently niche, the segment’s influence on the Edge AI Chips market is expected to widen as software libraries mature and fabrication processes accommodate asynchronous cores alongside standard digital blocks.

By Device Category: Consumer Volume, Enterprise Value

Consumer hardware—smartphones, wearables, and smart-home appliances—commanded 44.20% of 2025 shipments. Smartphones, equipped with NPUs such as Apple’s 16-core Neural Engine (38 TOPS) and Qualcomm’s Hexagon v68 DSP series, performed on-device translation, image segmentation, and sensor fusion without cloud assistance. Smart speakers embedded with far-field voice activation have also migrated to edge inference, lowering latency to <50 ms and easing privacy concerns. The high-unit volume anchors consumption growth for the Edge AI Chips market, though average selling prices remain compressed.

Enterprise and industrial devices, ranging from programmable logic controllers to ruggedized gateways, are forecast to expand at a 24.1% CAGR through 2031. Manufacturing plants deploy edge-enabled machine-vision stations that reject non-conforming parts in milliseconds, cutting waste by 15% in pilot programs. Healthcare providers roll out edge-based patient-monitoring units that detect cardiac anomalies on-device, transmitting anonymized trend data to hospital servers. These solutions demand longer operating lifespans, higher thermal tolerances, and field-upgradable firmware, permitting vendors to command premiums that outstrip consumer margins and lift the overall Edge AI Chips market size.

By End-User Industry: Smart-City Infrastructure Expands, Automotive Accelerates

Smart-city and surveillance systems held 29.35% of 2025 revenue, driven by municipal investments in traffic-light optimization, crowd-density analytics, and infrastructure inspection. On-device video analytics reduced backhaul traffic by 95% in trials featuring DFI and DEEPX’s multi-stream processing engine. Public-safety agencies appreciate lower latency in incident detection and the compliance advantage of keeping raw footage within jurisdictional boundaries. These benefits reinforce procurements that underpin the broader Edge AI Chips market demand across urban-management domains.

Automotive and transportation use cases, encompassing advanced driver-assistance systems and autonomous mobility, are expected to grow 26.2% annually between 2026-2031. Magna’s integration of NVIDIA’s DRIVE AGX Thor SoC, capable of 1,000 TOPS, highlights the appetite for in-vehicle compute that supports sensor fusion, path planning, and driver monitoring. Edge inference handles time-critical perception tasks locally, meeting stringent functional-safety targets (ISO 26262) while allowing over-the-air updates. High performance and ASIL-D certification requirements elevate chip value per vehicle, feeding long-run revenue in the Edge AI Chips market.

By Process Node: Mature Nodes Sustain Volume, Advanced Nodes Drive Innovation

The ≥14 nm cohort maintained a 39.20% share in 2025 owing to its favorable cost structure, robust yields, and ecosystem maturity. Analog and mixed-signal co-integration aligns naturally with mature nodes, enabling cost-effective sensor front-ends inside smart-home cameras and industrial HMIs. Automotive Tier-1 suppliers also favor proven geometries for longevity and reliability reasons. Continued design-win momentum at these nodes assures baseline volumes that stabilize manufacturing utilization rates for the Edge AI Chips market.

Conversely, the ≤5 nm tier is forecast to log a 55.4% CAGR through 2031. TSMC’s 3 nm process delivers 1.6× transistor density and 30% lower power compared with 5 nm, supporting transformer-based neural models once reserved for cloud servers. Apple secured the foundry’s initial capacity lot, while Samsung plans to ramp its 3 nm gate-all-around variant for wearables and AR glasses. The high-mix, low-volume nature of bleeding-edge nodes aligns with premium consumer devices and enterprise gateways that command elevated ASPs, elevating profitability within the Edge AI Chips market even as absolute shipments remain modest relative to mature-node totals.

Geography Analysis

Asia-Pacific retained 43.60% revenue dominance in 2025, underpinned by a vertically integrated supply chain that spans wafer fabrication, advanced packaging services, and ODM manufacturing. Taiwan’s TSMC operated at 100% utilization across its 5 nm and 3 nm lines. South Korea’s Samsung Electronics supplemented logic supply with high-bandwidth memory stacks, a synergy crucial for low-latency inference accelerators. China’s public-private funds redirected subsidies toward edge-oriented silicon once export rules curbed access to data-center GPUs, prompting innovation in smart-surveillance, electric-vehicle ECUs, and industrial-robot controllers. Japan contributed complementary strengths in image sensors and power-management ICs, rounding out a regional ecosystem that collectively underpins expansion in the Edge AI Chips market.

North America ranked second, differentiated by its leadership in intellectual-property design and software ecosystems. NVIDIA, Intel, and Qualcomm advanced heterogeneous die-stacking techniques that embed AI logic adjacent to CPUs and connectivity modules, delivering single-package solutions for robotics and private 5 G base stations. Cloud hyperscalers such as Google and Microsoft broadened their in-house silicon portfolios to include edge-inference ASICs embedded in on-premise appliances, expanding the regional share of the Edge AI Chips market. Automotive suppliers collaborated with Texas Instruments on radar-centric SoCs that enable occupant monitoring and driver-state detection, illustrating cross-vertical synergies within the continent’s technology stack.

Although smaller in absolute terms, the Middle East and Africa credits the fastest CAGR at 22.4% between 2026-2031. Saudi Arabia earmarked 20 billion SAR (USD 5.33 billion) for AI initiatives focused on edge-enablement urban services, while the UAE targeted a 14% GDP contribution from AI by 2030. Network-infrastructure build-outs adopted ZTE’s AI-capable edge servers to run video analytics in smart malls and to secure critical infrastructure. African deployments leaned on low-power edge modules that perform soil-moisture analytics and tuberculosis screening, operated in connectivity-restricted environments. Partnerships with multinational vendors shorten deployment lead times, accelerating the Edge AI Chips market trajectory across the region despite nascent indigenous manufacturing capacity.

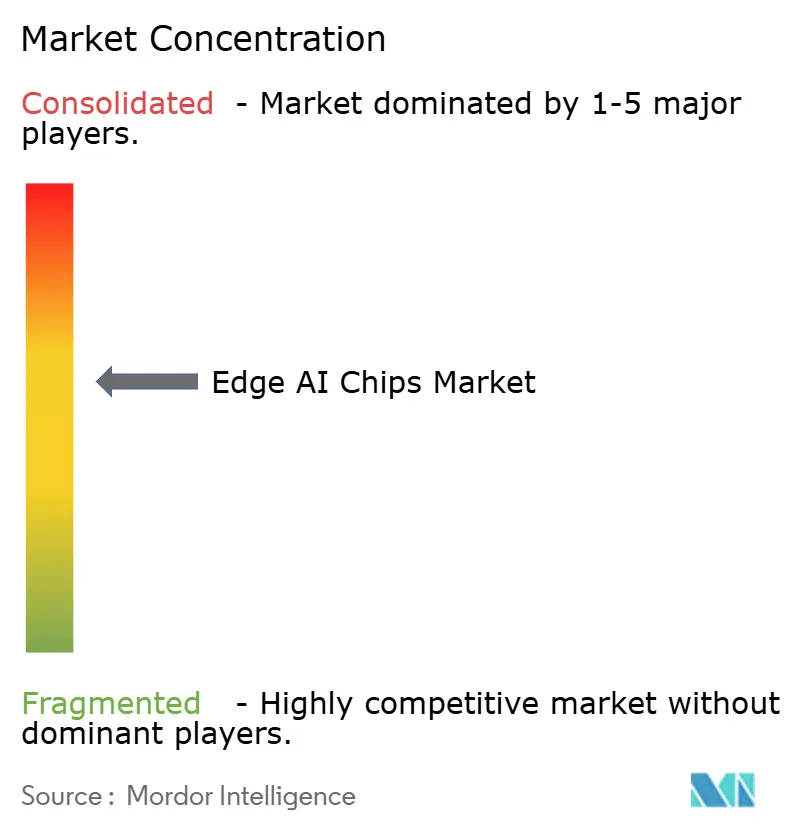

Competitive Landscape

The competitive structure bifurcates between diversified incumbents and agile specialists. NVIDIA extended its Jetson lineage by launching Orin Nano 8 GB, which delivers up to 40 TOPS at sub-15 W, targeting service robots and industrial PCs.[4]Vertu, “10 Leading AI Hardware Companies Shaping 2025,” vertu.com Intel refreshed its Core Ultra platform, integrating a matrix engine that yields 2.2× inference improvements at fixed power envelopes for edge PCs and thin clients. Qualcomm deepened its server-class ambitions by pairing its Oryon CPU cores with NVIDIA GPUs inside carrier-edge appliances, signaling converging interest between mobile and data-center incumbents.

Specialists such as Hailo, Blaize, and Kneron pursued ultra-low-power inference under 3 W, focusing on camera modules and battery-operated smart-home devices. Blaize partnered with KAIST to co-develop next-generation sparsity-aware acceleration for computer-vision workloads destined for autonomous shuttles. NXP’s acquisition of Kinara fortified its automotive and industrial MCU franchises with high-efficiency NPUs. Open-source hardware initiatives gained modest traction but have yet to neutralize proprietary tool-chain advantages that incumbents leverage to entrench customer loyalty within the Edge AI Chips market.

Patent activity offers an additional lens on rivalry: the US Patent and Trademark Office recorded a 78% year-over-year rise in edge-AI filings during 2024, spanning asynchronous compute fabrics, on-chip memory hierarchies, and thermal-aware placement. Advanced packaging, including 2.5D interposers and hybrid bonding, emerged as critical battlegrounds; TSMC’s planned 25% expansion in its CoWoS capacity reflects surging demand from chiplets that combine RF, analog, and AI tiles. Suppliers that secure leading-edge capacity plus robust software ecosystems are positioned to capture disproportionate economics as the Edge AI Chips market proceeds toward heterogeneous multi-die assemblies.

Edge AI Chips Industry Leaders

-

NVIDIA Corporation

-

Qualcomm Technologies Inc.

-

Intel Corporation

-

Apple Inc.

-

Alphabet Inc. (Google TPU)

- *Disclaimer: Major Players sorted in no particular order

Recent Industry Developments

- May 2025: The US government authorized exports of NVIDIA’s cutting-edge AI accelerators to the UAE between 2025-2027.

- May 2025: TSMC announced full 3 nm utilization and a 25% capacity expansion scheduled for H2-2025.

- May 2025: NVIDIA released Jetson Orin Nano 8 GB, delivering up to 40 TOPS in sub-15 W envelopes for robotics and embedded computing.

- March 2025: Blaize partnered with KAIST to advance low-power vision accelerators for autonomous vehicles.

Research Methodology Framework and Report Scope

Market Definitions and Key Coverage

Our study defines the edge artificial intelligence chips market as all purpose-built or re-purposed semiconductor dies, ASICs, GPUs, FPGAs, NPUs, and emerging neuromorphic cores integrated inside devices that execute AI workloads locally at the network edge rather than in hyperscale data centers.

Scope Exclusions: Chips designed exclusively for cloud-training systems or general-purpose microcontrollers without on-device AI acceleration are excluded.

Segmentation Overview

-

By Chipset

- CPU

- GPU

- ASIC

- FPGA

- Neuromorphic

-

By Device Category

- Consumer Devices

- Enterprise/Industrial Devices

-

By End-user Industry

- Manufacturing and Industrial 4.0

- Automotive and Transportation

- Smart Cities and Surveillance

- Healthcare and Wearables

- Retail and Hospitality

-

By Process Node

- ≥14 nm

- 7-10 nm

- ≤5 nm

-

Geography

-

North America

- United States

- Canada

-

South America

- Brazil

- Argentina

- Rest of South America

-

Europe

- Germany

- United Kingdom

- France

- Italy

- Russia

- Rest of Europe

-

Asia-Pacific

- China

- Japan

- South Korea

- India

- ASEAN

- Rest of Asia-Pacific

-

Middle East and Africa

-

Middle East

- GCC

- Rest of Middle East

-

Africa

- South Africa

- Rest of Africa

-

Middle East

-

North America

Detailed Research Methodology and Data Validation

Primary Research

Interviews with chip architects, smartphone OEM sourcing managers, and AI camera module integrators across North America, East Asia, and Europe enabled us to validate real ASP corridors, wafer capacity utilization, and adoption rates in smart vision, automotive ADAS, and industrial IoT devices. Insights from these discussions closed critical data gaps and recalibrated preliminary desk assumptions.

Desk Research

We first inspected freely available tier-1 statistics such as World Semiconductor Trade Statistics shipment volumes, US International Trade Commission customs codes, OECD ICT indicators, and patent filing trends archived in Questel to outline production baselines and technology pacing. Complementary signals were gathered from industry bodies like the Global Semiconductor Alliance, open IEEE journals on 5 nm process nodes, company 10-K filings, and investor decks that detail edge AI roadmap volumes. Subscription datasets, WSTS for quarterly unit splits, D&B Hoovers for vendor revenue splits, and Dow Jones Factiva for product-launch news helped map supplier footprints and average selling price (ASP) drifts. This list is illustrative; many other public and proprietary sources fed the desk phase.

Market-Sizing & Forecasting

A top-down reconstruction that blends WSTS shipment units with edge-device penetration rates by category (smartphones, surveillance cameras, autonomous vehicles, wearables) sets the 2025 baseline. Selective bottom-up supplier roll-ups and channel checks on sampled ASP × volume anchor reasonableness. Key variables like foundry wafer starts at ≤7 nm, average TOPS/Watt road maps, 5G smartphone install base, smart-city camera installs, and automotive L2+ ADAS attach rates drive year-on-year deltas. Five-year forecasts employ multivariate regression informed by the above drivers and expert consensus, while scenario analysis tests sensitivity to silicon node transitions and regulatory privacy mandates.

Data Validation & Update Cycle

Outputs pass multi-layer variance checks versus historical WSTS and customs totals; anomalies trigger re-contact of sources before analyst sign-off. Mordor Intelligence refreshes every twelve months and issues interim revisions if material events, such as new export controls or sub-5 nm yield breakthroughs, shift outlooks.

Why Mordor's Edge AI Chips Baseline Commands Reliability

Published figures rarely match because firms differ on chip taxonomy, device inclusion, ASP derivations, and forecast cadence. Our disciplined scope, annual refresh, and dual-path (top-down plus bottom-up) audit minimize those variances.

Benchmark comparison

| Market Size | Anonymized source | Primary gap driver |

|---|---|---|

| USD 3.67 B (2025) | Mordor Intelligence | - |

| USD 20.9 B (2024) | Global Consultancy A | Blends data-center AI accelerators with edge chips, inflating value |

| USD 3.0 B (2024) | Industry Association B | Omits neuromorphic and sub-1 W NPUs, understating future share |

| USD 7.05 B (2024) | Regional Consultancy C | Uses list-price ASPs without channel discounts, overstating revenue |

In sum, clients gain a balanced, transparent baseline that traces every figure to observable units, validated prices, and repeatable steps, giving decision-makers confidence that our numbers mirror the real market pulse today and tomorrow.

Key Questions Answered in the Report

What is the projected value of the Edge AI Chips market by 2031?

The market is forecast to reach USD 11.54 billion by 2031, rising from USD 3.67 billion in 2025.

Which chipset category dominates present sales?

ASICs held 37.45% of revenue in 2025, reflecting superior performance-per-watt for targeted edge workloads.

Which segment of the Edge AI Chips industry is expanding quickest?

Neuromorphic architectures are expected to post a 48.3% CAGR through 2031, far exceeding the overall market pace.

Why is Asia-Pacific pivotal to the Edge AI Chips market?

It hosts leading-edge fabrication, advanced packaging clusters, and large consumer electronics demand, delivering 43.60% of global revenue in 2025.

What is the single biggest barrier to new entrants?

Sub-5 nm design programs can cost more than USD 500 million, with tape-out expenses of roughly USD 30 million per spin, deterring smaller firms.

How will 5G influence the Edge AI Chips market over the next five years?

5G’s low latency and network slicing enable workload distribution across device, edge node, and cloud tiers, boosting silicon demand and adding about 4.3% to the forecast CAGR.

Page last updated on: