Semiconductor Silicon Intellectual Property Market Analysis by Mordor Intelligence

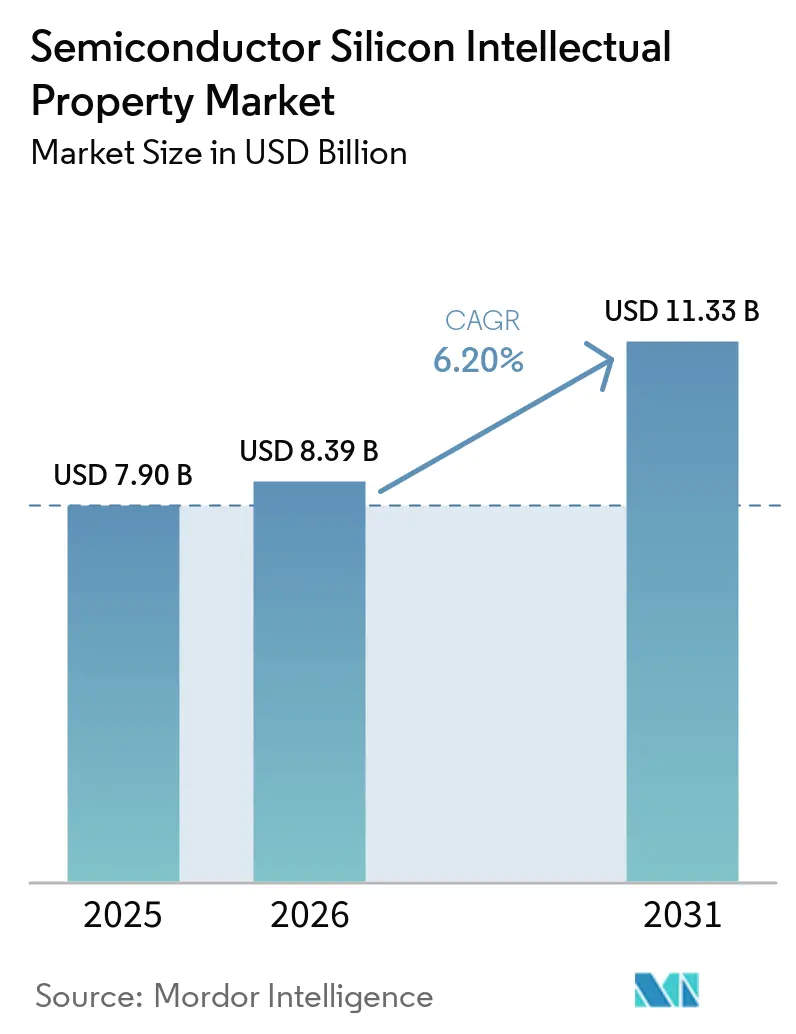

The Semiconductor silicon IP market size is expected to grow from USD 7.9 billion in 2025 to USD 8.39 billion in 2026 and is forecast to reach USD 11.33 billion by 2031 at 6.2% CAGR over 2026-2031. The rising dependence on reusable intellectual-property blocks for complex system-on-chip designs, the accelerating deployment of IoT endpoints, and the sustained migration toward advanced manufacturing nodes continue to underpin demand. Processor, interface, and security IP portfolios are expanding as chipmakers seek to compress time-to-market, while verification-ready RISC-V cores and chaplet-optimized interconnects are opening new revenue pools. Momentum around edge AI and functional-safety certification is intensifying competitive differentiation, as is tighter collaboration with foundries on process-specific optimization. License revenues remain dominant, but service-centric engagements covering customization, integration, and lifecycle support are becoming a material growth lever, especially at 5 nm and below, where design complexity peaks.

Key Report Takeaways

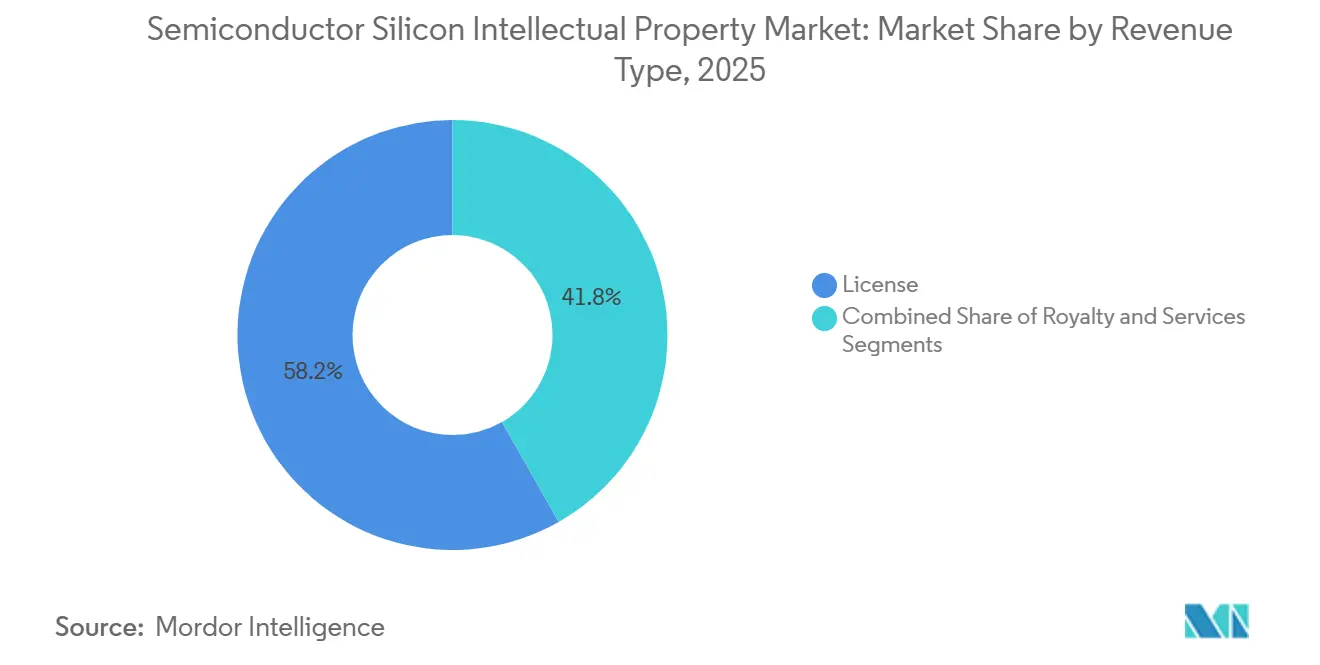

- By revenue type, license captured 58.22% of the Semiconductor silicon IP market share in 2025, whereas services are projected to expand at an 8.12% CAGR through 2031.

- By IP type, processor IP led with 45.88% revenue share in 2025, while wireless interface IP is advancing at a 7.05% CAGR.

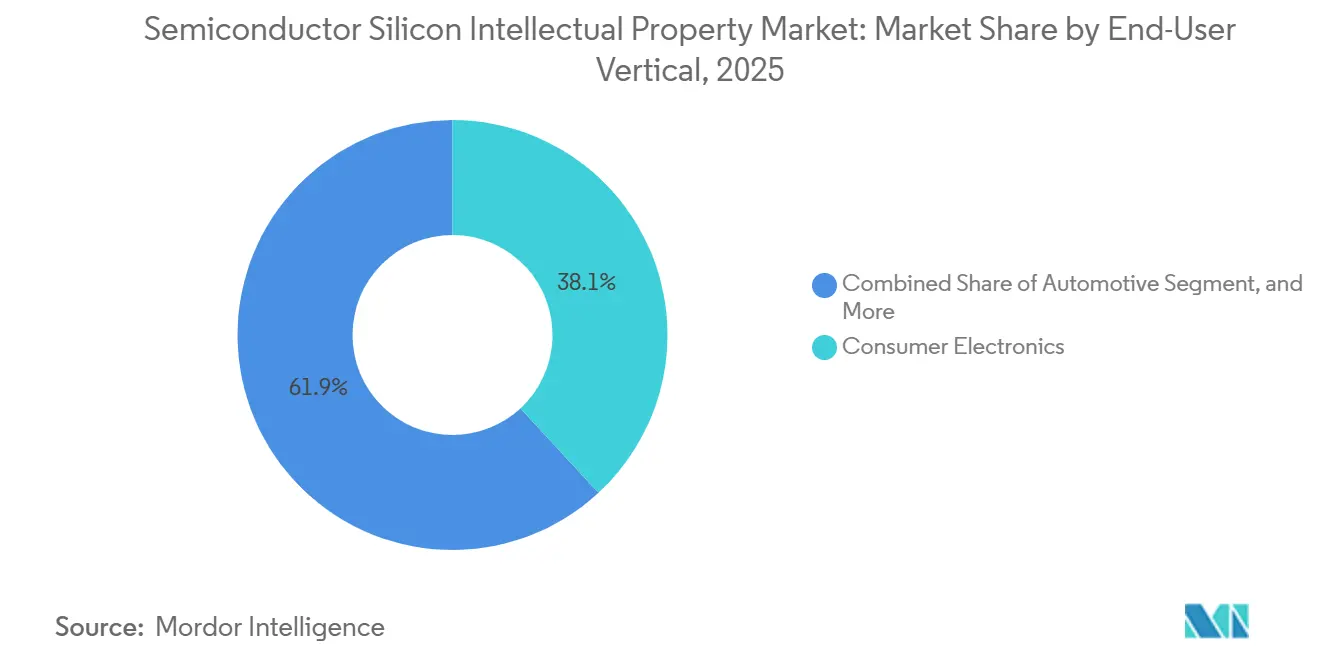

- By end-user vertical, consumer electronics accounted for 38.12% of the Semiconductor silicon IP market size in 2025; however, the automotive sector is poised for the fastest growth, with an 7.86% CAGR to 2031.

- By process node, 28 nm and above retained 41.73% share in 2025; the 5 nm and below tier is forecast to post a 7.55% CAGR.

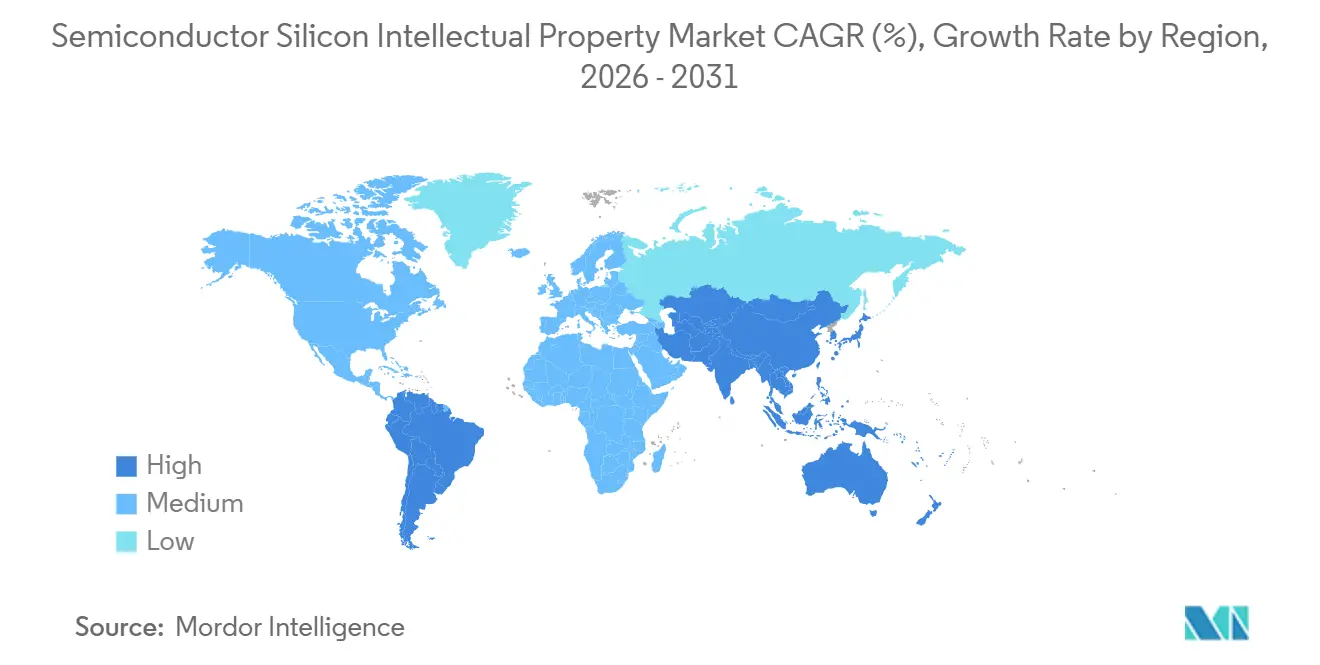

- By geography, Asia-Pacific held 52.14% of global revenue in 2025, and South America is expected to deliver the highest 8.24% CAGR.

Note: Market size and forecast figures in this report are generated using Mordor Intelligence’s proprietary estimation framework, updated with the latest available data and insights as of 2026.

Global Semiconductor Silicon Intellectual Property Market Trends and Insights

Drivers Impact Analysis*

| Driver | (~) % Impact on CAGR Forecast | Geographic Relevance | Impact Timeline |

|---|---|---|---|

| Proliferation of IoT-enabled connected devices | +1.80% | Global, with APAC leadership | Medium term (2-4 years) |

| Complexity of SoC designs and shrinking time-to-market | +1.50% | Global, concentrated in North America and APAC | Short term (≤ 2 years) |

| AI/ML accelerators integrated into edge devices | +1.20% | North America and EU leading, APAC following | Medium term (2-4 years) |

| Commercial demand for verified RISC-V CPU IP | +0.90% | Global, with strong momentum in China and Europe | Long term (≥ 4 years) |

| Chiplet and UCIe-based heterogeneous integration | +0.70% | North America and APAC core markets | Long term (≥ 4 years) |

| Automotive functional-safety (ISO 26262) compliance | +0.60% | Global, led by Europe and North America | Medium term (2-4 years) |

| Source: Mordor Intelligence | |||

Proliferation of IoT-Enabled Connected Devices

Record shipments of smart meters, wearables, and asset-tracking tags are driving a surge in low-power processor, wireless transceiver, and sensor-hub IP demand. Edge architectures now favor domain-specific blocks that execute real-time inference close to the data source, reducing latency and backhaul bandwidth.[1]Intel Corporation, “Form 10-K 2024,” intel.com Vendors offering turnkey subsystems that bundle MPU, RF, and secure-element IP are capturing design wins because they enable OEMs to integrate connectivity without expanding their internal teams. Heightened emphasis on hardware-rooted security is driving up attachment rates for cryptographic accelerators and physically unclonable function seeds, particularly where critical infrastructure is exposed to cyber risk. Proof-of-concepts piloted in smart factories and utilities during 2024 are moving to volume production, sustaining a multiyear growth runway for specialized IP portfolios.

Complexity of SoC Designs and Shrinking Time-to-Market

Top-tier smartphone and automotive chips now integrate upward of 50 IP blocks, spanning multiple voltage islands and asynchronous clock domains. Coordinating verification across this landscape adds schedule risk that most OEMs mitigate by sourcing pre-verified IP with published safety artifacts.[2]Universal Chiplet Interconnect Express Consortium, “UCIe Specification 2.0,” ucie.io Foundry-qualified variants trimmed for leakage, variation, and electromigration further shorten tape-out cycles, prompting suppliers to expand consultancy services that cover RTL, physical implementation, and package co-design. Chiplet architectures amplify the value of interface IP, adhering to the UCIe 2.0 spec because heterogeneous dies must interoperate across vendor boundaries. Fast-tracking silicon on these modular platforms has turned IP reuse into an operational necessity rather than a cost preference.

AI and ML Accelerators Integrated into Edge Devices

Growth in transformer-based language models and perception stacks is spreading beyond data centers into smartphones, cameras, and industrial robots. Neural-processing IP blocks that marry systolic arrays with local SRAM scratchpads now accompany mainstream CPU cores to perform on-device inference under 1 W power budgets.[3]NVIDIA Corporation, “Form 10-K 2024,” nvidia.com Demand for high-bandwidth memory controllers, optimized cache hierarchies, and sparsity-aware matrix engines is translating into larger silicon royalty pools per design-win. Compliance with nascent AI governance legislation in the EU has introduced new requirements around explainability, prompting IP vendors to embed telemetry hooks and secure debug features that enable post-deployment audits.

Commercial Demand for Verified RISC-V CPU IP

RISC-V International membership climbed past 3,000 organizations in 2024, reflecting broad confidence in the open ISA model. Commercial cores from SiFive, Andes, and others ship with deterministic latency, functional-safety packages, and extensible instruction sets that let customers tailor accelerators without paying blanket royalties to incumbent architectures. National chip-sovereignty programs in China and the EU are pouring grants into RISC-V tool-chain maturation, catalyzing a pipeline of application-specific SoCs. Mainstream EDA vendors have responded by pre-integrating RISC-V models into verification flows, easing adoption for automotive and industrial clients previously deterred by ecosystem fragmentation.

Restraints Impact Analysis*

| Restraint | (~) % Impact on CAGR Forecast | Geographic Relevance | Impact Timeline |

|---|---|---|---|

| High upfront licensing costs and scale disadvantages | -1.10% | Global, particularly affecting smaller companies | Short term (≤ 2 years) |

| Royalty disputes and patent-litigation exposure | -0.80% | Global, concentrated in major markets | Medium term (2-4 years) |

| Government chip-sovereignty programs favouring in-house IP | -0.60% | China, EU, India primarily | Long term (≥ 4 years) |

| Security vulnerabilities eroding third-party IP trust | -0.40% | Global, with heightened concern in defense sectors | Medium term (2-4 years) |

| Source: Mordor Intelligence | |||

High Upfront Licensing Costs and Scale Disadvantages

Multi-million-dollar entry fees for high-end processors or SerDes IP deter startups and niche players, forcing them toward less capable open-source blocks or older nodes. Revenue-sharing and subscription licensing models are emerging but remain a minority, as entrenched suppliers protect premium pricing tied to proven validation collateral.[4]Cadence Design Systems, “Form 10-K 2024,” cadence.com Porting a popular IP core from 28 nm to 5 nm frequently doubles engineering cost, further widening the gap between tier-one chipmakers and smaller design houses. Consequently, market entry barriers slow overall innovation velocity and may cap addressable demand among mid-volume OEMs until alternative licensing frameworks scale.

Royalty Disputes and Patent-Litigation Exposure

Ongoing lawsuits such as ARM against Qualcomm highlight how ambiguous core-modification rights invite costly litigation. Patent assertion entities have intensified scrutiny of interface and memory-controller IP, triggering retroactive royalty claims that disrupt supply chains. OEMs now conduct deeper freedom-to-operate audits, which lengthen design cycles and occasionally shift vendor selection to balance legal risk over technical merit. For IP licensors, legal defense budgets divert R and D resources and may dampen roadmap aggressiveness, particularly for smaller firms unable to absorb unpredictable settlements.

*Our updated forecasts treat driver/restraint impacts as directional, not additive. The revised impact forecasts reflect baseline growth, mix effects, and variable interactions.

Segment Analysis

By Revenue Type: Service Engagements Accelerate Value Capture

Service-related payments represent the fastest-growing portion of the Semiconductor silicon IP market, climbing at an 8.12% CAGR through 2031 as chipmakers outsource customization, hardening, and bring-up tasks that exceed their internal bandwidth. However, licenses controlled 58.22% of revenue in 2025, and customers deploying 5 nm and below reported a steep rise in post-license engineering hours, making bundled service contracts attractive. IP vendors now position platform subscriptions that include continuous performance tuning, over-the-air security patch support, and silicon lifecycle analytics. These programs enhance account stickiness and mitigate cyclical swings associated with tape-out volume.

The shift also cushions price pressure facing commodity cores, particularly in mid-range processor and Ethernet IP categories. Vendors with large field-application teams leverage integration consulting as a margin-enhancing strategy, offsetting declining per-unit royalties as volumes shift to cost-sensitive IoT devices. Hybrid revenue models spur recurring cash flows and align supplier incentives with customer production milestones, reinforcing the prospect that services could capture a larger slice of the Semiconductor silicon IP market size by the end of the decade.

By IP Type: Wireless Interface Momentum Outpaces Processor Growth

Expanding 5G infrastructure, WiFi 7 adoption, and Bluetooth LE Audio upgrades are propelling wireless interface IP toward a 7.05% CAGR. Chipmakers integrating multi-standard radios seek ready-made RF, baseband, and coexistence logic that meets global certification requirements, allowing for consumer device launches on aggressive timelines. Processor IP nevertheless remained the single biggest revenue contributor at 45.88% in 2025, anchored by the ubiquity of CPU cores in every SoC.

Competitive intensity within processor IP has increased due to the entry of RISC-V entrants, prompting incumbents to widen their differentiators through integrated AI acceleration and power management enhancements. In parallel, wired interface IP continues to serve data center and automotive connectivity demands at stable mid-single-digit growth. Security, memory-controller, and analog IP round out the opportunity landscape, collectively benefiting from SoC silicon area inflation and the rise of application-specific designs that require specialized subsystems.

By End-User Vertical: Automotive Electronics Surges Amid Software-Defined Vehicle Shift

Consumer devices, such as smartphones and smart TVs, maintained dominance with 38.12% of 2025 revenue; however, deceleration in mature handset markets shifts future momentum to vehicles, industrial robotics, and edge computing. The automotive silicon content per vehicle is rising because centralized domain controllers and advanced driver-assistance systems require powerful processors, domain-specific accelerators, and high-speed interconnects certified to ISO 26262 ASIL confidence levels. This environment is expected to support an 7.86% CAGR for automotive IP demand as OEMs transition to over-the-air updatable ECUs that require verified safety IP and secure boot chains.

Industrial automation and smart factory initiatives similarly fuel demand for determinism-focused IP such as real-time Ethernet and time-sensitive networking blocks. Medical and aerospace applications remain smaller niches but carry premium ASPs because of rigorous qualification cycles and longevity commitments, enabling select vendors to command higher margins within an otherwise price-pressured Semiconductor silicon IP market.

By Process Node: Advanced Geometry Adoption Commands Premiums

While legacy 28 nm platforms still represented 41.73% of total 2025 spend, designers targeting flagship smartphones and AI accelerators migrated aggressively toward 5 nm and below for performance-per-watt gains, bringing that tier a 7.55% forward CAGR. Porting leading CPU or GPU IP to extreme-ultraviolet lithography nodes incurs significant characterization cost, yet chipmakers justify the premium through higher ASPs in end products. Tier-one vendors with multi-node portfolios monetize process-specific variants and design kits, thereby strengthening their share against specialized boutiques that lack the resources for continuous node shuttles.

Mid-range 16/14 nm remains popular among automotive suppliers seeking a balance of cost and performance, especially as full ISO 26262 kits are only now emerging for sub-10 nm fabrication. Demand for 10/7 nm geometries extends through mainstream mobile and consumer AI assistants, sustaining diversified revenue streams across the full process spectrum and ensuring the Semiconductor silicon IP market retains a broad technology footprint.

Geography Analysis

The Asia-Pacific region led global revenue with a 52.14% stake in 2025, driven by its deep manufacturing ecosystems in China, South Korea, Taiwan, and Japan, as well as supportive semiconductor stimulus packages. Foundry co-development programs foster close collaboration on design rules and IP hardening, thereby enhancing regional adoption rates for both domestic and international portfolios. China’s self-reliance mandate propels investment into RISC-V and security IP, while South Korea’s K-Semiconductor Belt strengthens demand for memory-centric interface blocks. Japan concentrates on automotive semiconductors and advanced packaging, adding traction for functional-safety IP and chiplet interconnects.

North America remains pivotal as home to major IP licensors, hyperscale data center chip designers, and defense contractors. The CHIPS Act’s incentives for onshore fabrication encourage coordinated IP, EDA, and foundry engagements that prioritize supply chain resiliency. Strong venture funding for AI startups translates into rapid prototyping of custom accelerators, sustaining domestic demand across all IP categories. Canada’s growing quantum-computing ecosystem also emerges as a niche customer segment for cryogenic interface IP.

Europe, though smaller in aggregate revenue, exerts outsized influence through leadership in automotive electronics, industrial automation, and power semiconductors. EU Chips Act subsidies are earmarked for state-of-the-art pilot lines, spurring requests for 7 nm and below IP with built-in fail-operational safety logic. Meanwhile, South America’s Semiconductor silicon IP market is projected to post the highest 8.24% CAGR as Brazil’s localization incentives and Argentina’s talent base attract design centers, expanding regional consumption of verified IP cores. Middle East and Africa remain a nascent market but shows potential through sovereign datacenter investments and edge-AI surveillance rollouts in the Gulf Cooperation Council, laying groundwork for future IP spending.

Competitive Landscape

The Semiconductor silicon IP market exhibits moderate concentration, with ARM, Synopsys, and Cadence retaining significant portfolios that span CPU, interface, security, and analog categories. Each leverages a broad partner ecosystem and long-standing design-in relationships to preserve incumbency, yet faces share erosion as open-source RISC-V cores and niche accelerator IP gain traction. Competitive pressure intensifies in wireless interface and AI-specific domains, where vendors such as Imagination and SiFive push differentiated architectures tuned for power efficiency.

Strategic initiatives are increasingly focused on platform completeness rather than individual block excellence. Synopsys’s USD 35 billion acquisition of Ansys in September 2024 created an end-to-end design and simulation suite expected to accelerate customer migration to service-oriented engagements. Cadence partnered with TSMC in July 2024 to co-develop chiplet-ready interconnect IP, signaling an industry shift toward vertically aligned solution stacks optimized for advanced packaging. ARM’s 3nm-ready Cortex-X925 aims to solidify its processor leadership in high-end mobile and laptop segments, emphasizing integrated NPU blocks to counter custom silicon threats.

Emerging white-space opportunities include quantum-secure cryptographic IP, 224 G SerDes for next-gen datacenter fabrics, and thermal-aware AI accelerators for edge robotics. Vendors able to align roadmaps with foundry FinFET and gate-all-around transitions, while securing early access to backside-power delivery flows, stand to influence the trajectory of the Semiconductor silicon IP market through 2030. Consolidation is likely to continue as capital intensity and verification complexity rise, drawing clear lines between full-stack providers and specialized boutiques.

Semiconductor Silicon Intellectual Property Industry Leaders

Faraday Technology Corporation

Fujitsu Ltd

LTIMindtree Limited

ARM Ltd (SoftBank )

Synopsys Inc.

- *Disclaimer: Major Players sorted in no particular order

Recent Industry Developments

- October 2024: SiFive announced a USD 175 million Series F funding round led by Qualcomm Ventures and Samsung Catalyst Fund, earmarked for expanding RISC-V CPU IP aimed at automotive and datacenter silicon.

- September 2024: Synopsys completed its USD 35 billion acquisition of Ansys, integrating multi-physics simulation into its IP and EDA portfolio.

- August 2024: ARM Holdings launched Cortex-X925 and Cortex-A725 CPU IP for 3 nm nodes, embedding enhanced neural-processing units for AI workloads.

- July 2024: Cadence Design Systems entered a strategic partnership with TSMC to co-develop chiplet interconnect and 3D-stacking-optimized IP solutions.

Global Semiconductor Silicon Intellectual Property Market Report Scope

A semiconductor intellectual property (IP) core is a reclaimable logic, functional unit, cell, or layout design typically licensed to multiple vendors as building blocks in different chip designs. In today’s IC design era, more and more system functionality is integrated into single chips (system-on-chip/SOC designs). These pre-designed IP cores/blocks are becoming increasingly important in these SOC designs. This is because most of the SOC designs have a standard microprocessor and a lot of system functionality, which are standardized and hence can be reused across several designs if designed once.

The semiconductor silicon intellectual property market is segmented by revenue type (license, royalty, and services), IP type (processor IP, wired & wireless interface IP, and other IP types), end-user vertical (consumer electronics, computers & peripherals, automobile, industrial, and other end-user verticals), and geography (North America (United States, Canada), Europe (United Kingdom, Germany, France, Rest of Europe), Asia Pacific (China, Taiwan, Japan, South Korea, India) Rest of Asia Pacific), and Rest of the World). The market sizes and forecasts are provided in terms of value (USD) for all the above segments.

| License |

| Royalty |

| Services |

| Processor IP |

| Wired Interface IP |

| Wireless Interface IP |

| Other IP Types |

| Consumer Electronics |

| Computers and Peripherals |

| Automotive |

| Industrial |

| Other Verticals |

| 28 nm and Above |

| 16/14 nm |

| 10/7 nm |

| 5 nm and Below |

| North America | United States |

| Canada | |

| Mexico | |

| Europe | United Kingdom |

| Germany | |

| France | |

| Italy | |

| Rest of Europe | |

| Asia-Pacific | China |

| Japan | |

| India | |

| South Korea | |

| Rest of Asia | |

| Middle East | Israel |

| Saudi Arabia | |

| United Arab Emirates | |

| Turkey | |

| Rest of Middle East | |

| Africa | South Africa |

| Egypt | |

| Rest of Africa | |

| South America | Brazil |

| Argentina | |

| Rest of South America |

| By Revenue Type | License | |

| Royalty | ||

| Services | ||

| By IP Type | Processor IP | |

| Wired Interface IP | ||

| Wireless Interface IP | ||

| Other IP Types | ||

| By End-User Vertical | Consumer Electronics | |

| Computers and Peripherals | ||

| Automotive | ||

| Industrial | ||

| Other Verticals | ||

| By Process Node | 28 nm and Above | |

| 16/14 nm | ||

| 10/7 nm | ||

| 5 nm and Below | ||

| By Geography | North America | United States |

| Canada | ||

| Mexico | ||

| Europe | United Kingdom | |

| Germany | ||

| France | ||

| Italy | ||

| Rest of Europe | ||

| Asia-Pacific | China | |

| Japan | ||

| India | ||

| South Korea | ||

| Rest of Asia | ||

| Middle East | Israel | |

| Saudi Arabia | ||

| United Arab Emirates | ||

| Turkey | ||

| Rest of Middle East | ||

| Africa | South Africa | |

| Egypt | ||

| Rest of Africa | ||

| South America | Brazil | |

| Argentina | ||

| Rest of South America | ||

Key Questions Answered in the Report

What is the current valuation of the Semiconductor silicon IP market?

The Semiconductor silicon IP market size stands at USD 8.39 billion in 2026 and is projected to hit USD 11.33 billion by 2031.

Which revenue model is growing fastest among IP vendors?

Services linked to customization, integration, and lifecycle optimization are recording an 8.12% CAGR, outpacing traditional license and royalty streams.

Why is wireless interface IP attracting heightened demand?

Rollouts of 5G, WiFi 7, and Bluetooth LE Audio in consumer and industrial devices require certified RF and baseband IP that enable multi-standard connectivity without extending development cycles.

How is the automotive sector influencing IP adoption?

Automotive demand is growing at an 7.86% CAGR as ISO 26262-certified processor, interconnect, and security IP become essential for software-defined vehicles and advanced driver-assistance systems.

Which region leads global consumption of silicon IP blocks?

Asia-Pacific commands 52.14% of worldwide revenue owing to its dense manufacturing base and government-backed chip investment programs.

What technological transition poses the biggest opportunity through 2031?

The shift toward 5 nm and below nodes, paired with chiplet-based architectures, is expected to spur premium pricing for advanced interface and low-power IP portfolios.

Page last updated on:

_Intellectual_Property_Market_competive_logo.webp)