Tamanho e Participação do Mercado de Memória de Acesso Aleatório Dinâmica (DRAM)

Análise do Mercado de Memória de Acesso Aleatório Dinâmica (DRAM) pela Mordor Intelligence

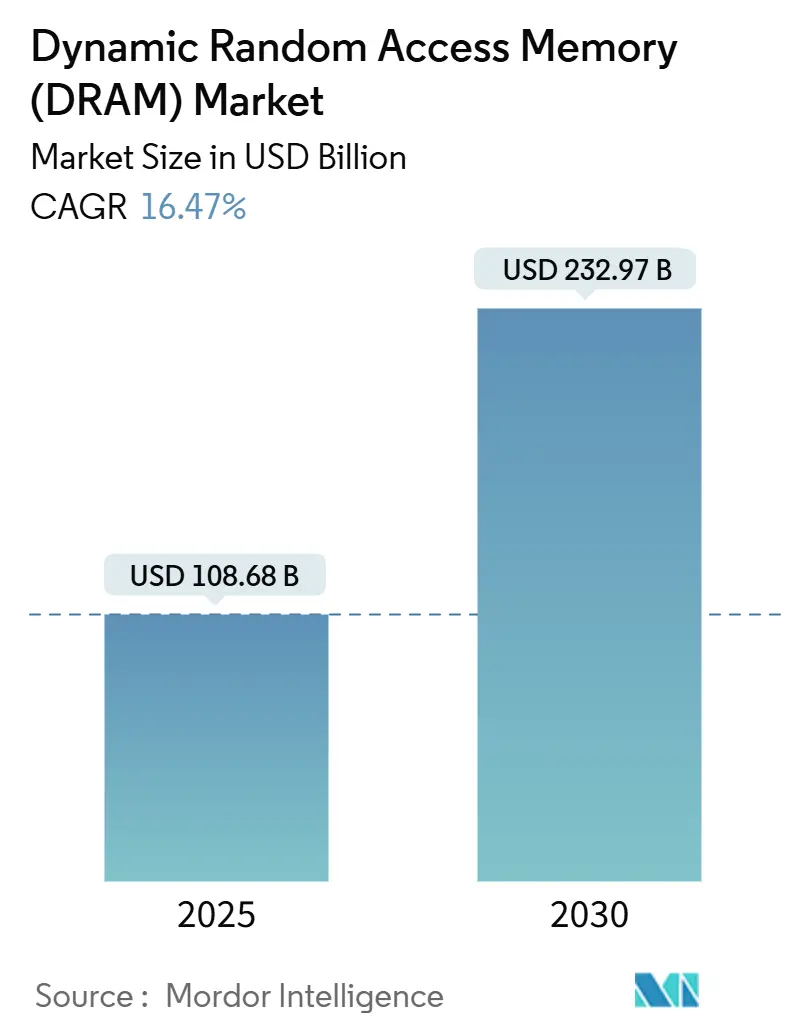

O tamanho do mercado de Memória de Acesso Aleatório Dinâmica está avaliado em USD 108,68 bilhões em 2025 e está projetado para alcançar USD 232,97 bilhões até 2030, resultando em uma forte CAGR de 16,47%. A adoção acelerada de servidores centrados em IA, o aumento acentuado da memória de alta largura de banda e os requisitos de qualificação automotiva mais rigorosos mudaram os critérios de compra da capacidade sozinha para um foco equilibrado em largura de banda, potência e desempenho térmico. Os operadores de nuvem de hiperescala começaram a renovar racks com módulos DDR5 e HBM3E durante 2024, enquanto os OEMs de handsets na Ásia moveram grande parte de seus portfólios flagship e de médio porte para LPDDR5X, mantendo coletivamente a utilização de fabricação acima de 95% até meados de 2025. O conteúdo de memória por veículo elétrico subiu rapidamente à medida que arquiteturas zonais substituíram redes ECU tradicionais, empurrando a demanda automotiva de DRAM para o território de múltiplos gigabytes. Ao mesmo tempo, conflitos de alocação de fornecimento entre linhas lucrativas de HBM3E e DDR4 legado desencadearam picos de preços que remodelaram trade-offs de custo-desempenho para PCs, smartphones e placas IoT industriais.

Principais Conclusões do Relatório

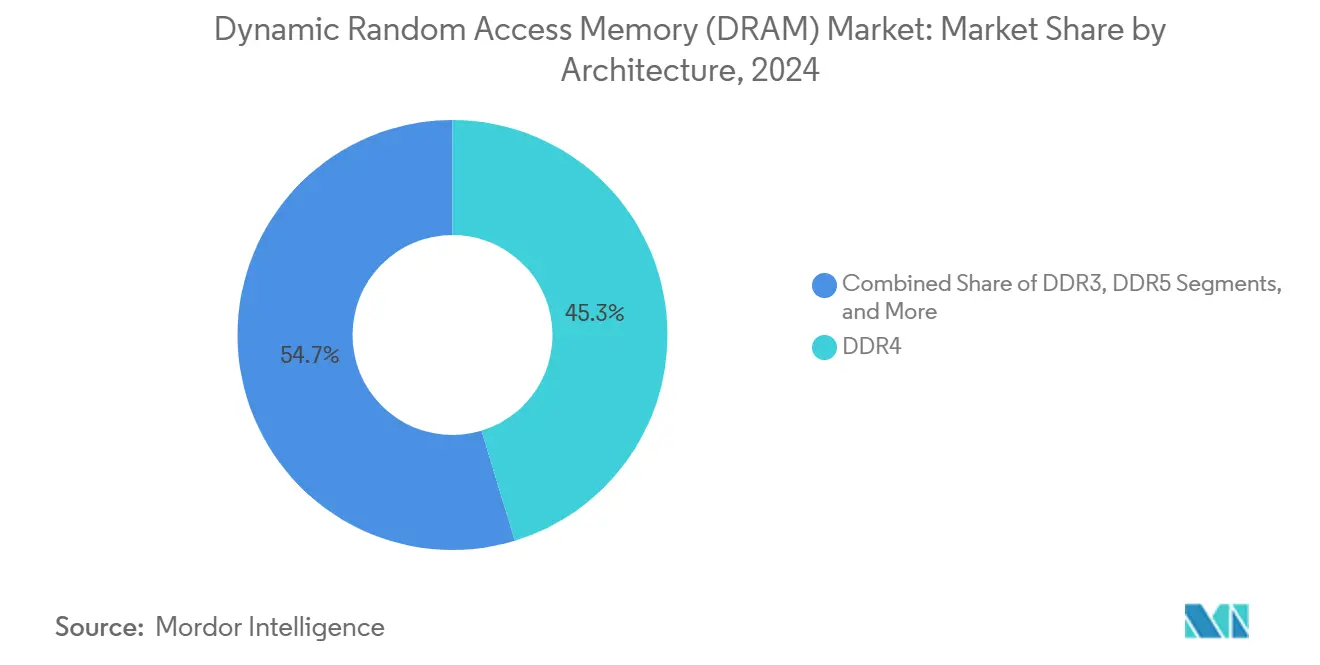

- Por arquitetura, DDR4 deteve 45,3% de participação no mercado de Memória de Acesso Aleatório Dinâmica em 2024, enquanto DDR5 está previsto para expandir a uma CAGR de 30,2% até 2030.

- Por nó tecnológico, a categoria de 19 nm-10 nm capturou 42,3% do tamanho do mercado de Memória de Acesso Aleatório Dinâmica em 2024 e está avançando a uma CAGR de 25,2% até 2030.

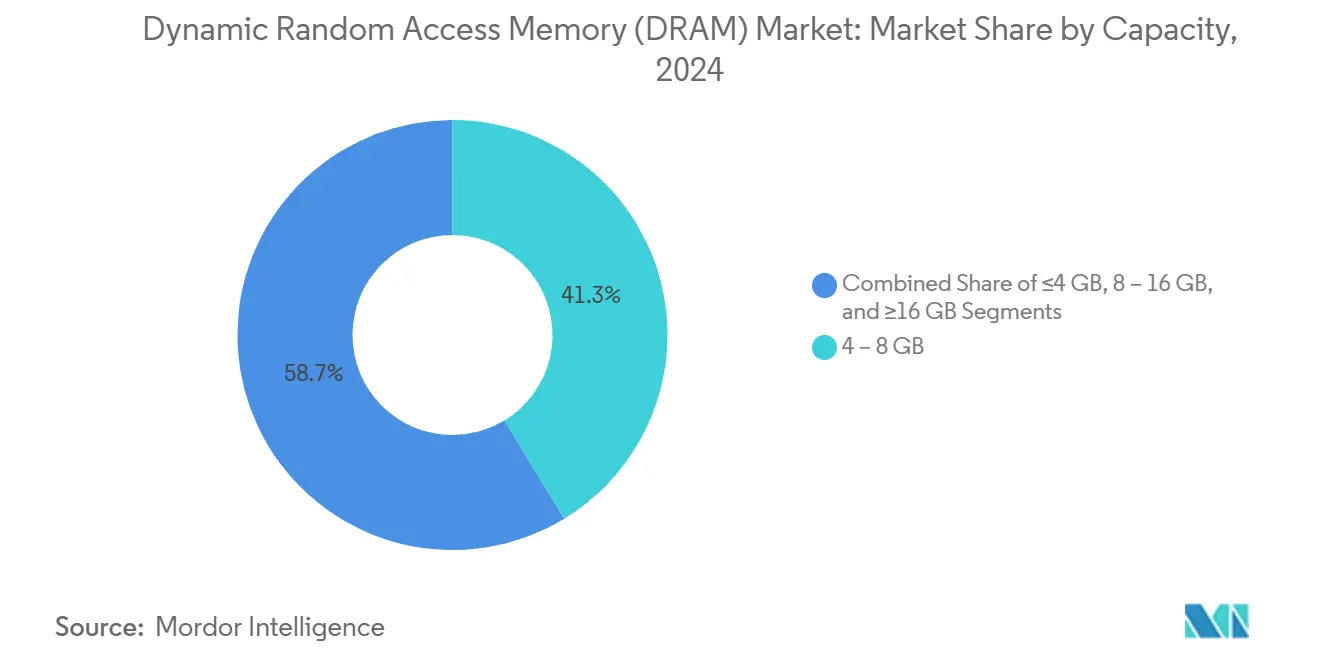

- Por capacidade, módulos de 4-8 GB comandaram 41,3% do tamanho do mercado de Memória de Acesso Aleatório Dinâmica em 2024, enquanto configurações ≥16 GB estão definidas para crescer 28,2% entre 2025 e 2030.

- Por aplicação de uso final, smartphones e tablets lideraram com 35,2% de participação na receita em 2024; eletrônicos automotivos está projetado para subir a uma CAGR de 31,2% até 2030.

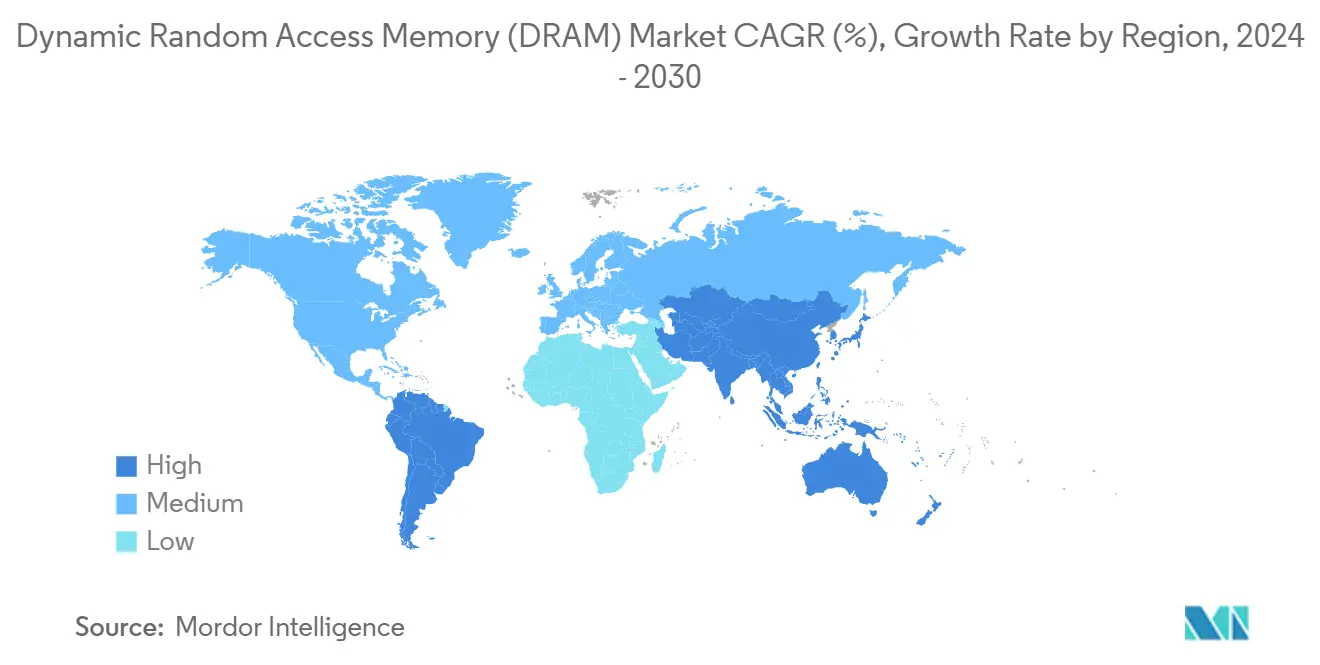

- Por geografia, Ásia-Pacífico respondeu por 31,2% das vendas de 2024, enquanto a América do Sul espera-se que registre uma CAGR de 22,2% durante o período de previsão.

Tendências e Insights do Mercado Global de Memória de Acesso Aleatório Dinâmica (DRAM)

Análise de Impacto dos Direcionadores

| Direcionador | (~) % Impacto na Previsão CAGR | Relevância Geográfica | Cronograma de Impacto |

|---|---|---|---|

| Pegada de Conteúdo Ascendente de Cargas de Trabalho de IA e IA Generativa em Data Centers de Hiperescala | +4.2% | Global, com concentração na América do Norte e APAC | Médio prazo (2-4 anos) |

| Adoção Crescente de LPDDR em Smartphones 5G Flagship e de Médio Porte Através da APAC | +3.8% | APAC central, expansão para mercados globais | Curto prazo (≤ 2 anos) |

| Controladores Zonais/de Domínio Automotivos Migrando de NOR para DRAM de Alta Temperatura | +2.9% | Global, adoção inicial na Europa e América do Norte | Longo prazo (≥ 4 anos) |

| Placas de Edge-AI e IoT Industrial Requerendo Módulos DRAM de Temperatura Estendida | +2.1% | Global, com hubs de manufatura na APAC | Médio prazo (2-4 anos) |

| Transição de Provedores de Serviços de Nuvem para Pools de Memória Conectados por CXL | +1.8% | América do Norte e UE, expandindo para APAC | Longo prazo (≥ 4 anos) |

| Fonte: Mordor Intelligence | |||

Pegada de conteúdo ascendente de cargas de trabalho de IA e IA generativa em data centers de hiperescala

As plataformas GP-AI Blackwell 2025 da NVIDIA estabeleceram linhas de base de largura de banda que eclipsaram arquiteturas DDR convencionais, elevando a memória média de servidor de 256 GB em 2024 para implementações de múltiplos terabytes até meados de 2025. Com cada stack HBM3E fornecendo mais de 1 TB/s, operadores de nuvem rearquitetaram racks em torno de topologias centradas em memória. A Samsung entregou DRAM CXL 2.0 pronta para produção que permitiu ao Azure e outros provedores agrupar memória através de hosts, melhorando a utilização enquanto adia capex em nós de computação adicionais.[1]Samsung Electronics, "CXL DRAM Enables New Data-Center Memory Architecture," semiconductor.samsung.com Fornecedores consequentemente mudaram starts de wafer de DDR4 para HBM, desencadeando escassez em graus legados mas acelerando o crescimento de lucro no segmento premium.

Adoção crescente de LPDDR em smartphones 5G flagship e de médio porte através da APAC

Amostras LPDDR5X 1γ da Micron rodando a 9.200 MT/s alcançaram fabricantes de handsets no Q1 2025, cortando energia em 20% e elevando configurações de linha de base em modelos chineses e indianos de 8 GB para 12 GB de RAM. Xiaomi, OPPO e marcas emergentes como Transsion estão presas em contratos futuros que consomem uma fatia crescente da capacidade de fabricação APAC, forçando fornecedores a equilibrar compromissos entre linhas móveis e de datacenter. A mudança deu ao LPDDR uma curva de crescimento mais acentuada do que qualquer outra memória móvel desde que LPDDR4 entrou em produção em massa em 2015.

Controladores zonais e de domínio automotivos migrando de NOR para DRAM de alta temperatura

Veículos elétricos construídos em plataformas definidas por software requeriam pools de memória que superavam em muito as pegadas de infoentretenimento legadas. Vários OEMs europeus validaram DRAM qualificada AEC-Q100 de 16 GB em 2024 e subsequentemente elevaram metas de plataforma para 90 GB por veículo em cronogramas de 2025. Samsung e SK Hynix investiram em ajustes de processo de temperatura ampla para garantir conformidade ISO 26262, criando barreiras para novos entrantes e melhorando disciplina de preços no canto de grau automotivo do mercado de Memória de Acesso Aleatório Dinâmica.

Placas de Edge-AI e IoT industrial requerendo módulos DRAM de temperatura estendida

Fornecedores de automação de fábrica atualizaram controladores lógicos programáveis e sistemas de visão com DDR4-3200 em classificações de -40 °C a 85 °C, permitindo inferência local de IA que corta latência de ida e volta na nuvem. ATP e Innodisk capitalizaram no nicho oferecendo DIMMs revestidos conforme com gerenciamento de refresh agressivo, que OEMs industriais aceitaram com prêmios de 30% sobre peças de grau comercial. O uplift de margem resultante incentivou grandes da DRAM a licenciar processos de ruggedização, expandindo fornecimento até 2026.

Análise de Impacto das Restrições

| Restrição | (~) % Impacto na Previsão CAGR | Relevância Geográfica | Cronograma de Impacto |

|---|---|---|---|

| Ciclicalidade Oferta-Demanda Conduzindo Volatilidade Extrema de ASP | -2.8% | Global, com efeitos amplificados em mercados spot | Curto prazo (≤ 2 anos) |

| Desafios de Erosão de Rendimento Abaixo de Nós EUV de 10 nm | -1.9% | Global, concentrado em fabs avançadas | Médio prazo (2-4 anos) |

| Controles Geopolíticos de Exportação na China Limitando Embarques de DRAM de Servidor de Alta Densidade | -1.4% | Focado na China, com impactos na cadeia de suprimentos global | Longo prazo (≥ 4 anos) |

| Fonte: Mordor Intelligence | |||

Ciclicalidade oferta-demanda conduzindo volatilidade extrema de ASP

Pull-ins de HBM de alta margem persuadiram fabs a adiar rodadas DDR4 no início de 2025, incendiando um salto de preço spot de 50% para módulos mainstream em maio. Contratos DDR5 também subiram 15-20%, levando OEMs a re-engenheirar listas de materiais de produtos ou sobre-encomendar para proteger contra picos adicionais. O loop de feedback amplificou volatilidade e cortou visibilidade para planejamento de produção, derrubando dois pontos ou mais da CAGR prevista do mercado de Memória de Acesso Aleatório Dinâmica.

Desafios de erosão de rendimento abaixo de nós EUV de 10 nm

Rodadas iniciais de nós 1β e 1γ sofreram defectividade de máscara e rugosidade estocástica de borda de linha, arrastando rendimentos para a faixa baixa de 70% em algumas fabs. Samsung e Micron alocaram orçamentos de P&D consideráveis para melhorias de resistência e nova tecnologia de pellicle, ainda assim curvas de aprendizado alongaram cronogramas de rampa. Rendimentos apertados restringiram produção de die durante uma janela de demanda de pico, adicionando pressão de custo que cascateou através de segmentos de consumidor e empresa.[2]TrendForce, "Samsung Targets 1c DRAM Yield Improvement by Mid-2025," trendforce.com

Análise de Segmento

Por Arquitetura: Aceleração DDR5 Remodela Hierarquias de Memória

DDR5 respondeu por uma participação mínima do mercado de Memória de Acesso Aleatório Dinâmica em 2024, ainda carregou a mais rápida CAGR prevista de 30,2%, sustentada pela atualização JESD79-5C da JEDEC que elevou tetos de desempenho para 8.800 Mbps. Esse salto técnico permitiu que construtores de nuvem tier-1 executassem configurações mistas DDR5-HBM3E que dobraram a largura de banda efetiva por socket. A DDR5 1γ da Micron alcançou 9.200 MT/s em fevereiro de 2025, um marco que empurrou OEMs de servidor a antecipar atualizações de plataforma. Enquanto isso, DDR4 reteve uma participação de 45,3% no mercado de Memória de Acesso Aleatório Dinâmica através de 2024 porque orçamentos de TI corporativa ainda favoreciam configurações otimizadas por custo. Pegadas legadas DDR3 e DDR2 continuaram a encolher à medida que design-ins industriais e automotivos migraram para padrões mais novos.

Fornecedores confrontaram um ato de equilíbrio: cada wafer reatribuído para DDR5 significava menos chips DDR4 para PCs, conduzindo picos de custo que fluíram a jusante para montadores de notebook na China. Detentores de inventário de cauda longa exploraram negociação de arbitragem, descarregando DDR4 estocado com prêmios não vistos desde 2017. O novo fator de forma CAMM2 da JEDEC removeu as restrições de altura de SO-DIMMs, permitindo que laptops e servidores edge adotassem stacks de lado único mais densos. Esses ganhos de empacotamento alimentaram o momentum do mercado de Memória de Acesso Aleatório Dinâmica em direção a normas de largura de banda mais alta através de dispositivos de consumidor e empresa.

Nota: Participações de segmento de todos os segmentos individuais disponíveis mediante compra do relatório

Por Nó Tecnológico: Processos Avançados Conduzem Diferenciação Competitiva

A faixa de 19 nm-10 nm deteve 42,3% do tamanho do mercado de Memória de Acesso Aleatório Dinâmica em 2024 e está projetada para crescer 25,2% até 2030 à medida que fornecedores espremem dies adicionais por wafer sem mergulhar no abismo de risco de rendimento de sub-10 nm. Produção 1γ habilitada por EUV começou a embarcar unidades de receita no Q1 2025, mas rendimentos de linha permaneceram pelo menos oito pontos abaixo de linhas 1z maduras. Consequentemente, muitos fabricantes de dispositivos renovaram acordos para graus 1z e 1y para amortecer risco de custo, dando aos processos de nó médio um impulso de volume.

SK Hynix apresentou um roadmap DRAM de porta vertical que promete empilhamento a nível de wafer além de 2027, sinalizando o pivô de longo prazo de escalonamento lateral para arquiteturas 3D. Cada encolhimento planar sucessivo entrega menos de 12% de redução de custo depois que conjunto de máscaras, materiais e depreciação são fatorados, empurrando fabs a procurar redesenhos estruturais em vez de encolhimento geométrico sozinho. Sensibilidade de custo em eletrônicos móveis e de consumidor manteve nós ≥20 nm vivos para SKUs focados em preço, garantindo uma mistura de produção estratificada que diversificou produção de fab e sustentou resiliência de receita geral.

Por Capacidade: Configurações de Alta Densidade Aceleram Através de Aplicações

Módulos ≥16 GB estão projetados para registrar uma CAGR de 28,2% e mover de status de nicho em 2024 para adoção mainstream em automotivos e handsets premium até 2030. Conteúdo por veículo elétrico subiu de gigabytes de dígito único no início de 2024 para aproximadamente 40 GB em builds piloto do final de 2025, e discussões de roadmap entre OEMs europeus referenciam metas de 4 TB para autonomia Nível-4 até o fim da década. Líderes de smartphone adotaram camadas de 16 GB para lançamentos flagship centrados em IA no H1 2025, ampliando o guarda-chuva de preço para dispositivos de médio porte de 12 GB. A categoria 4-8 GB, embora ainda 41,3% do tamanho do mercado de Memória de Acesso Aleatório Dinâmica em 2024, começou a ceder participação à medida que telefones de entrada cruzaram a linha de base de 6 GB.

Fornecedores se beneficiaram de ASPs mais ricos em dies de alta densidade mas enfrentaram restrições de start de wafer, especialmente ao equilibrar compromissos HBM3E. Aprendizado de rendimento em nós 1γ e futuros 1δ ditará se misturas de capacidade podem inclinar ainda mais para cima sem desencadear choques de preço indevidos. Distribuidores de canal em Shenzhen relataram inventário mais apertado de chips de 8 GB durante Q2 2025 à medida que fabs priorizaram correspondências de die de 16 GB para garantir pedidos de data center, exemplificando a competição entre vetores de demanda de consumidor e empresa.

Por Aplicação de Uso Final: Eletrônicos Automotivos Emerge como Líder de Crescimento

Eletrônicos automotivos está previsto para subir a uma CAGR de 31,2%, eclipsando tablets e PCs como o vertical de movimento mais rápido do mercado de Memória de Acesso Aleatório Dinâmica. Arquiteturas de computação zonal mandataram DRAM de alta temperatura e alta confiabilidade que opera sobre -40 °C a 125 °C, e vitórias de design em plataformas de ano-modelo 2026 travaram compromissos de compra estendendo além de 2029. Pools de memória se aproximaram de 90 GB em protótipos EV premium durante 2025, equipando veículos para atualizações contínuas over-the-air e assistência ao motorista baseada em IA. Embarques de smartphone e tablet ainda entregaram uma participação de receita de 35,2% em 2024, mas saturação em regiões maduras temperou sua trajetória de crescimento.

Demanda de datacenter permaneceu robusta, conduzida por clusters de inferência e treinamento de IA cujos ciclos de expansão são agora medidos em trimestres em vez de anos. Atualizações de gráficos e consoles de jogos programadas para final de 2026 fornecerão um uplift cíclico para variantes GDDR e DDR6. IoT industrial e gateways edge tomaram participação incremental ao adotar módulos de 8-16 GB endurecidos por temperatura, embora sua natureza fragmentada diluísse o poder de barganha de qualquer OEM único. A paisagem de aplicação heterogênea reforça complexidades de alocação de fornecimento, compelindo fornecedores a equilibrar diferentes certificações de qualidade, fatores de forma e ciclos de vida em paralelo.

Análise Geográfica

Ásia-Pacífico reteve uma posição de receita de 31,2% em 2024 na força de fabs agrupados através da Coreia do Sul, Taiwan e China continental. Fornecedores sul-coreanos prometeram KRW 120 trilhões (USD 84 bilhões) para build-outs de capacidade até 2028, uma figura destinada a salvaguardar liderança tanto em produção HBM quanto DRAM tradicional.[3]SK Hynix, "SEDEX 2024: Showcasing AI Memory Leadership," news.skhynix.com Casas de montagem por contrato de Taiwan, enquanto isso, expandiram linhas de empacotamento avançado para atender demanda crescente de HBM4, alavancando know-how de front-end de nós lógicos para introduzir inovações Through-Silicon-Via que reduzem resistência térmica.

América do Norte formou o maior mercado de consumo à medida que construtores de hiperescala aceleraram atualizações de rack e montadoras nos Estados Unidos integraram controladores zonais. Micron garantiu USD 6,1 bilhões em financiamento CHIPS Act para construir uma nova megafab, um movimento visando des-riscar exposição geopolítica e encurtar lead times para clientes domésticos. Europa manteve um foco tecnológico em aplicações automotivas e industriais, com OEMs alemãos insistindo em garantias de temperatura estendida e longevidade que buscaram preços premium.

América do Sul está prevista para crescer a uma CAGR de 22,2% à medida que Brasil, Argentina e México nutrem ecossistemas de montagem eletrônica para localizar fornecimento. Incentivos de política cortaram tarifas de importação em componentes de memória montados domesticamente, criando mudanças modestas mas significativas em estratégias de sourcing. O Oriente Médio e África exibiram crescimento de dígito médio ancorado por build-outs de data-center em estados do Conselho de Cooperação do Golfo e penetração crescente de smartphone na Nigéria e Quênia, ainda instabilidade política continuou a temperar adoção mais ampla. Combinadas, essas narrativas regionais sublinham como o mercado de Memória de Acesso Aleatório Dinâmica diversifica fluxos de receita mesmo quando manufatura permanece concentrada no Leste Asiático.

Panorama Competitivo

O mercado de Memória de Acesso Aleatório Dinâmica operou como um oligopólio em 2025, com Samsung, SK Hynix e Micron detendo conjuntamente aproximadamente 95% da capacidade de wafer. SK Hynix avançou para 36% de participação no Q1 2025 após ser a primeira a produzir em volume stacks HBM3E de 1,15 TB/s para programas líderes de acelerador de IA. Samsung reteve liderança em linhas de grau automotivo e garantiu um acordo de fornecimento de USD 3 bilhões com AMD para futuros nós HBM3E. Micron fechou a lacuna tecnológica ao embarcar DDR5 e LPDDR5X 1γ seis meses à frente de seu roadmap original, restaurando equilíbrio competitivo em categorias DIMM mainstream.

Diferenciação tecnológica girou em torno da adoção EUV, com cada camada de máscara removida traduzindo em economias de custo de die apreciáveis. Ainda a intensidade de capital íngreme criou barreiras para jogadores de segundo nível como Nanya e Winbond, que escolheram se especializar em segmentos industriais de nicho ou de baixa potência em vez de perseguir nós de ponta. Firmas chinesas CXMT e JHICC expandiram produção DDR5 usando processos 1x maduros, fornecendo montadores de smartphone domésticos que procuraram mitigar restrições de exportação dos EUA.

Alianças de ecossistema também emergiram em torno de padrões de interconexão como CXL. Marvell fez parceria com múltiplos fornecedores DRAM para lançar controladores de expansão de memória que elevam taxas de anexação tanto para DDR4 quanto DDR5 ao agrupar recursos através de lâminas de servidor. A especificação HBM4 da JEDEC, publicada em abril de 2025, despertou acordos de desenvolvimento conjunto frescos entre fabricantes de dispositivos e fundições para alinhar em pitch TSV, orçamentos térmicos e confiabilidade de empacotamento.[4]JEDEC, "JEDEC Publishes HBM4 Standard," jedec.org Contra esse pano de fundo, startups explorando MRAM, ReRAM e 3D X-AI visaram offloads de carga de trabalho de nicho, embora nenhuma ainda tivesse demonstrado paridade de custo com DRAM commodity até meados de 2025.

Líderes da Indústria de Memória de Acesso Aleatório Dinâmica (DRAM)

-

Samsung Electronics Co. Ltd.

-

Micron Technology Inc.

-

SK Hynix Inc.

-

Nanya Technology Corporation

-

Winbond Electronics Corporation

- *Isenção de responsabilidade: Principais participantes classificados em nenhuma ordem específica

Desenvolvimentos Recentes da Indústria

- Abril de 2025: JEDEC lançou o padrão HBM4 (JESD270-4), dobrando contagem de canal para 32 e elevando largura de banda de pico para 2 TB/s.

- Março de 2025: SMART Modular introduziu um módulo de memória CXL não-volátil em fator de forma EDSFF para servidores intensivos em dados.

- Março de 2025: KIOXIA revelou um SSD NVMe de 122,88 TB baseado em BiCS FLASH de oitava geração, voltado para conjuntos de dados de IA.

- Fevereiro de 2025: Micron Technology anunciou embarque em volume de DDR5 1γ rodando a 9.200 MT/s com 20% menos energia, marcando a primeira DRAM de sexta geração baseada em EUV no mercado.

Escopo do Relatório Global do Mercado de Memória de Acesso Aleatório Dinâmica (DRAM)

Memória de acesso aleatório dinâmica, chamada DRAM, é usada em vários dispositivos de computação e eletrônicos como PCs, smartphones, players de música, laptops, netbooks e computadores tablet. O escopo do estudo foca na análise de mercado de semicondutores DRAM vendidos através do globo, e dimensionamento de mercado abrange a receita gerada através de DRAM vendida por vários players de mercado para indústrias de usuário final. O estudo também rastreia os parâmetros-chave do mercado, influenciadores de crescimento subjacentes e principais fornecedores operando na indústria, que apoiarão as estimativas de mercado e taxas de crescimento durante o período de previsão. O estudo analisa ainda o impacto geral da COVID-19 no ecossistema.

O mercado DRAM é segmentado por arquitetura (DDR3, DDR4, DDR5 e DDR2), aplicações (smartphones/tablets, PC/laptops, data centers, gráficos, produtos de consumo e automotivo), e geografia (Estados Unidos, Europa, Coreia, China, Taiwan, Resto da Ásia-Pacífico e Resto do Mundo). O relatório oferece previsões e tamanhos de mercado em valor (USD) para todos os segmentos acima.

| DDR2 e Anteriores |

| DDR3 |

| DDR4 |

| DDR5 |

| LPDDR |

| GDDR |

| ≥20 nm |

| 19 nm - 10 nm |

| <10 nm (EUV) |

| ≤4 GB |

| 4 - 8 GB |

| 8 - 16 GB |

| ≥16 GB |

| Smartphones e Tablets |

| PCs e Laptops |

| Servidores e Data Centers de Hiperescala |

| Gráficos e Consoles de Jogos |

| Eletrônicos Automotivos |

| Eletrônicos de Consumo (Set-top Boxes, Smart TV, VR/AR) |

| Dispositivos Industriais e IoT |

| Outros |

| América do Norte | Estados Unidos | |

| Canadá | ||

| México | ||

| Europa | Alemanha | |

| França | ||

| Reino Unido | ||

| Países Nórdicos | ||

| Resto da Europa | ||

| Ásia-Pacífico | China | |

| Taiwan | ||

| Coreia do Sul | ||

| Japão | ||

| Índia | ||

| Resto da Ásia-Pacífico | ||

| América do Sul | Brasil | |

| Chile | ||

| Argentina | ||

| Resto da América do Sul | ||

| Oriente Médio e África | Oriente Médio | Arábia Saudita |

| Emirados Árabes Unidos | ||

| Turquia | ||

| Resto do Oriente Médio | ||

| África | África do Sul | |

| Resto da África | ||

| Por Arquitetura | DDR2 e Anteriores | ||

| DDR3 | |||

| DDR4 | |||

| DDR5 | |||

| LPDDR | |||

| GDDR | |||

| Por Nó Tecnológico | ≥20 nm | ||

| 19 nm - 10 nm | |||

| <10 nm (EUV) | |||

| Por Capacidade | ≤4 GB | ||

| 4 - 8 GB | |||

| 8 - 16 GB | |||

| ≥16 GB | |||

| Por Aplicação de Uso Final | Smartphones e Tablets | ||

| PCs e Laptops | |||

| Servidores e Data Centers de Hiperescala | |||

| Gráficos e Consoles de Jogos | |||

| Eletrônicos Automotivos | |||

| Eletrônicos de Consumo (Set-top Boxes, Smart TV, VR/AR) | |||

| Dispositivos Industriais e IoT | |||

| Outros | |||

| Por Geografia | América do Norte | Estados Unidos | |

| Canadá | |||

| México | |||

| Europa | Alemanha | ||

| França | |||

| Reino Unido | |||

| Países Nórdicos | |||

| Resto da Europa | |||

| Ásia-Pacífico | China | ||

| Taiwan | |||

| Coreia do Sul | |||

| Japão | |||

| Índia | |||

| Resto da Ásia-Pacífico | |||

| América do Sul | Brasil | ||

| Chile | |||

| Argentina | |||

| Resto da América do Sul | |||

| Oriente Médio e África | Oriente Médio | Arábia Saudita | |

| Emirados Árabes Unidos | |||

| Turquia | |||

| Resto do Oriente Médio | |||

| África | África do Sul | ||

| Resto da África | |||

Questões-Chave Respondidas no Relatório

Qual é o valor atual do mercado de Memória de Acesso Aleatório Dinâmica?

O mercado está avaliado em USD 108,68 bilhões em 2025 e está definido para alcançar USD 232,97 bilhões até 2030.

Qual arquitetura DRAM está crescendo mais rapidamente?

DDR5 está previsto para subir a uma CAGR de 30,2%, conduzido por servidores de IA e PCs de próxima geração.

Por que os preços DRAM estão tão voláteis em 2025?

Fabs desviaram capacidade para HBM3E de margem mais alta, levando a um pico de preço spot de 50% para DDR4 e aumentos de 15-20% para DDR5 em maio de 2025.

Como o setor automotivo está influenciando a demanda DRAM?

Veículos definidos por software requerem DRAM de alta temperatura, empurrando conteúdo de memória de gigabytes de dígito único em 2024 para aproximadamente 90 GB em protótipos de 2025 e muito maior em futuras plataformas EV.

Qual região espera-se crescer mais rapidamente até 2030?

América do Sul está projetada para expandir a uma CAGR de 22,2% à medida que incentivos de montagem local atraem produção eletrônica.

Quem lidera o segmento HBM hoje?

SK Hynix avançou sendo primeira a fabricar stacks HBM3E de 16 camadas, garantindo uma participação de 36% de embarques DRAM gerais no Q1 2025.

Página atualizada pela última vez em: