Tamanho e Participação do Mercado de Memória de Acesso Aleatório Estática (SRAM)

Análise do Mercado de Memória de Acesso Aleatório Estática (SRAM) pela Mordor Intelligence

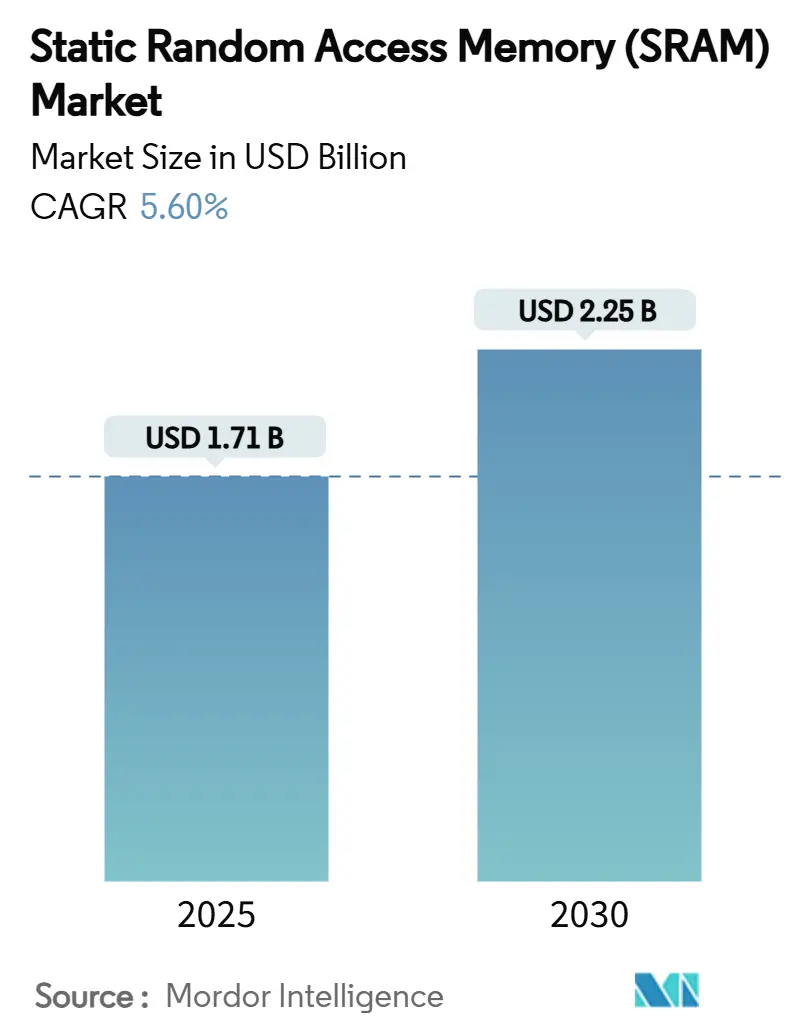

O tamanho do mercado global de Memória de Acesso Aleatório Estática situou-se em US$ 1,71 bilhão em 2025 e está previsto para avançar a uma TCAC de 5,60% para alcançar US$ 2,25 bilhões até 2030. O crescimento refletiu a transição em direção à computação centrada em IA, implementações de 5G e processamento de borda em tempo real, todos os quais dependem da latência ultra-baixa da SRAM para hierarquias de cache. Fornecedores de semicondutores priorizaram o encolhimento das células SRAM em 2 nm para suportar caches L2/L3 maiores enquanto mantêm orçamentos de energia sob controle. A modernização de data centers impulsionou a demanda por buffers de alta velocidade em switches e aceleradores, enquanto ciclos de renovação de dispositivos de consumo mantiveram uma linha de base estável. A resiliência da cadeia de suprimentos tornou-se fundamental após o terremoto de 2024 em Taiwan interromper a produção de foundries, levando a iniciativas de diversificação geográfica. Enquanto isso, memórias não-voláteis emergentes como MRAM intensificaram a pressão competitiva sobre SRAM convencional em projetos com backup de bateria.[1]Everspin Technologies, "MRAM Replaces nvSRAM," everspin.com

Principais Conclusões do Relatório

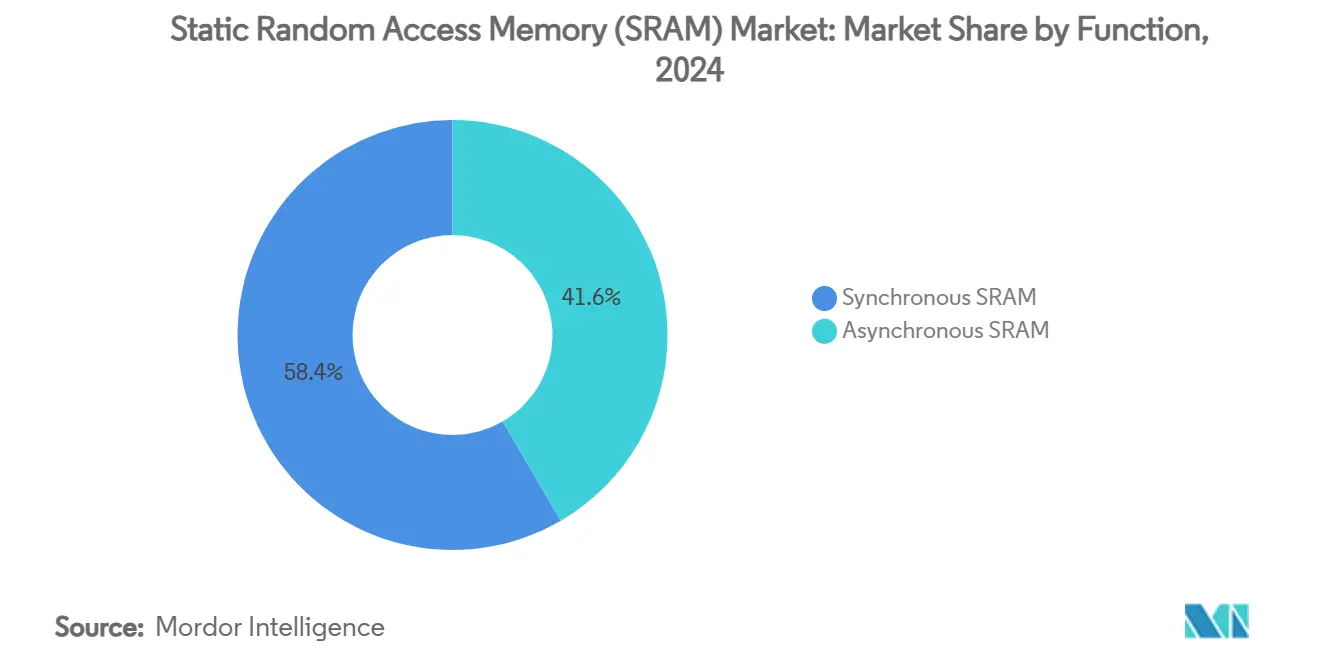

Por função, SRAM síncrona deteve 58,4% da participação do mercado de Memória de Acesso Aleatório Estática em 2024; SRAM assíncrona registrou a TCAC mais rápida de 6,4% até 2030.

Por tipo de produto, pseudo-SRAM liderou com 54,4% da participação de receita em 2024, enquanto SRAM não-volátil está projetada para expandir a uma TCAC de 8,7%.

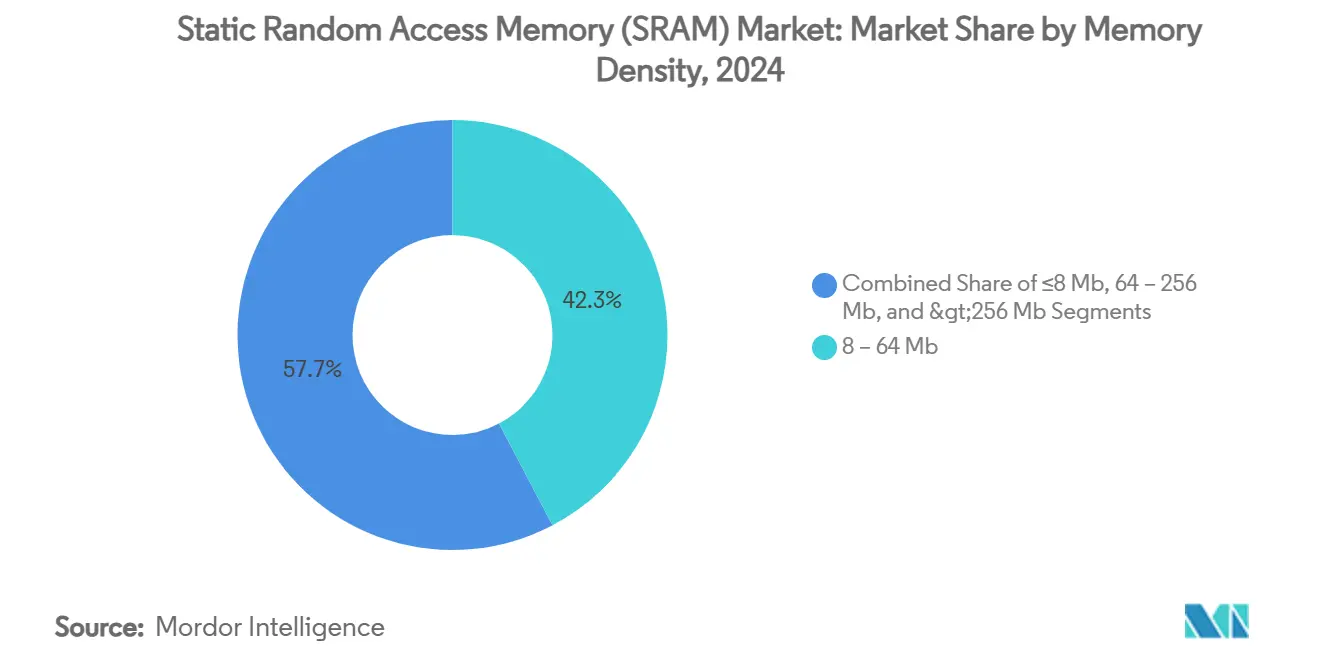

Por densidade de memória, o segmento de 8-64 Mb representou 42,3% do tamanho do mercado de Memória de Acesso Aleatório Estática em 2024; densidades acima de 256 Mb estão posicionadas para crescer a uma TCAC de 7,5%.

Por usuário final, eletrônicos de consumo capturaram 46,3% da receita em 2024; automotivo e aeroespacial estão avançando a uma TCAC de 9,1%.

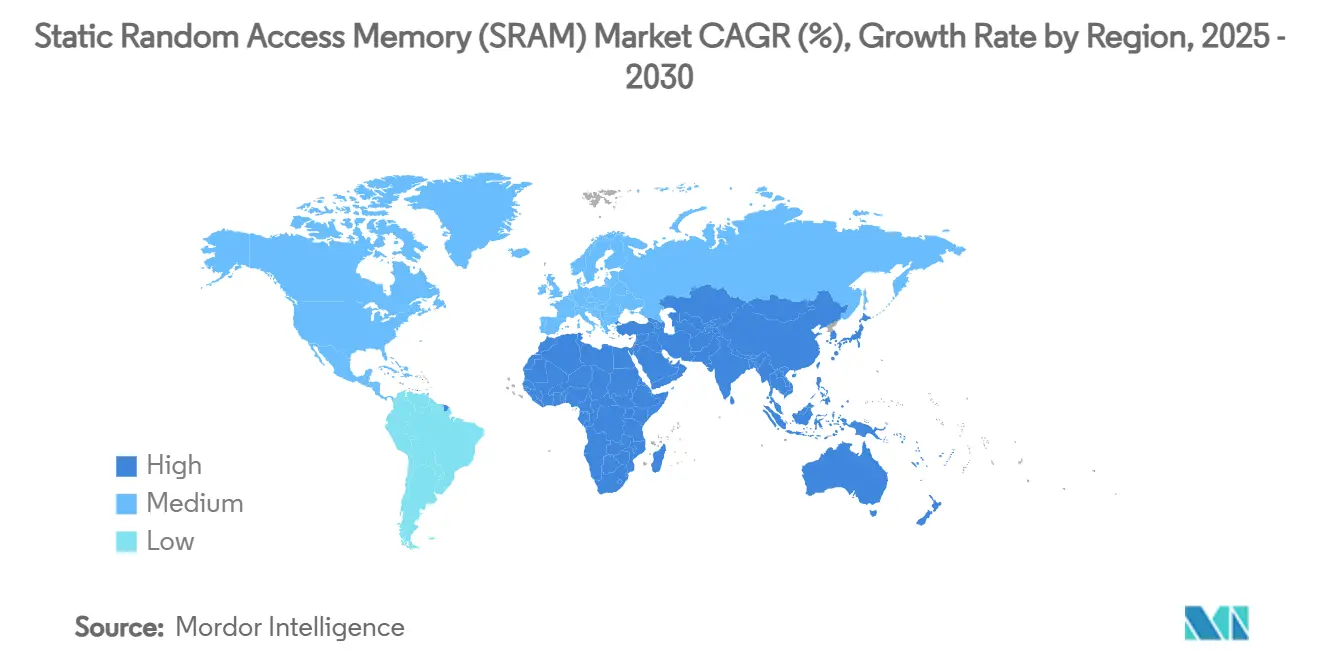

Por geografia, Ásia-Pacífico comandou 61,4% da participação do mercado de Memória de Acesso Aleatório Estática em 2024, enquanto Oriente Médio e África são as regiões de crescimento mais rápido com TCAC de 7,5%.

Tendências e Insights do Mercado Global de Memória de Acesso Aleatório Estática (SRAM)

Análise de Impacto dos Direcionadores

| Direcionador | (~) % Impacto na Previsão de TCAC | Relevância Geográfica | Cronograma de Impacto |

|---|---|---|---|

| Crescente demanda por memórias cache mais rápidas | +1.2% | Global, concentrada na América do Norte e Ásia-Pacífico | Médio prazo (2-4 anos) |

| Construção de data centers e redes 5G | +1.0% | Global, com ênfase na Ásia-Pacífico e América do Norte | Curto prazo (≤ 2 anos) |

| Proliferação de dispositivos IoT e wearables | +0.8% | Global, liderada por centros de manufatura da Ásia-Pacífico | Médio prazo (2-4 anos) |

| SRAM 3D integrada para chiplets | +0.6% | América do Norte e fábricas avançadas da Ásia-Pacífico | Longo prazo (≥ 4 anos) |

| SRAM resistente à radiação para satélites LEO | +0.4% | Global, concentrada na América do Norte e Europa | Longo prazo (≥ 4 anos) |

| Adoção de aceleradores de IA em memória | +0.7% | Global, com liderança da América do Norte e Ásia-Pacífico | Médio prazo (2-4 anos) |

| Fonte: Mordor Intelligence | |||

Crescente demanda por memórias cache mais rápidas

CPUs e GPUs avançadas enviadas em 2025 apresentaram caches on-chip maiores para reduzir latência de inferência, com o Xeon 6 da Intel mostrando um aumento de performance de 1,4× ligado à otimização de cache. A plataforma de 2 nm da TSMC entregou maior densidade de células SRAM do que nós 18A concorrentes, dando aos clientes de hiperescala mais cache L3 por watt. A Marvell revelou SRAM personalizada de 2 nm que empacota 6 Gb de memória de baixo consumo, reduzindo o uso de energia em 66% versus nós anteriores. Tais inovações permitiram que aceleradores de IA mantivessem parâmetros de modelo mais próximos às unidades de computação, sustentando throughput enquanto continham tráfego DRAM. Consequentemente, o mercado de Memória de Acesso Aleatório Estática se beneficiou de atualizações de capacidade recorrentes em silício de data center e borda.

Construção de data centers e redes 5G

Operadores de nuvem dobraram densidades de rack para hospedar servidores de IA, promovendo uso mais amplo de buffers de pacote baseados em SRAM em switches top-of-rack. A Microsoft testou backplanes wireless de 246-275 GHz em halls de servidores, onde buffering em escala de microssegundos dependia de SRAM de alta velocidade. O transporte 5G convergido da Cisco promoveu latência determinística, necessitando filas profundas de SRAM em roteadores. A Corning prevê um salto de 18× na demanda por fibra por rack de IA, espelhando o dimensionamento de buffers de switch construídos em SRAM síncrona. Esta onda de infraestrutura reforçou visibilidade de receita de curto prazo para o mercado de Memória de Acesso Aleatório Estática.

Proliferação de dispositivos IoT e wearables

Chips de borda de ultra-baixo consumo alimentando wearables de saúde adotaram blocos SRAM personalizados que retêm dados em microwatts de dígito único; processadores neurais da Syntiant exemplificaram a tendência. Gateways Edge2LoRa incorporaram SRAM modesta para pré-processar dados de sensores, cortando largura de banda de backhaul em 90%. MCUs automotivas como o R-Car da Renesas integram SRAM determinística para atualizações over-the-air e cargas de trabalho ADAS. Coletivamente, essas implementações ampliaram a base de clientes para produtos SRAM assíncronos e pseudo-SRAM adaptados a restrições de energia.

Adoção de aceleradores de IA em memória

Protótipos de pesquisa demonstraram SRAM fotônica com lógica XOR incorporada executando em >10 GHz enquanto consome 13,2 fJ por bit, apontando para futuras arquiteturas de compute-in-memory. Uma SRAM compute-in-memory de 28 nm 36 Kb reduziu energia de atualização de peso, pavimentando o caminho para motores de inferência de IA incorporados. O PERSYST da Everspin posicionou memória persistente para cargas de trabalho de IA críticas para segurança onde retenção de dados é necessária após perda de energia. Esses avanços aumentaram o interesse em SRAM especializada que combina velocidade com programabilidade, expandindo ainda mais o mercado de Memória de Acesso Aleatório Estática.

Análise de Impacto das Restrições

| Restrição | (~) % Impacto na Previsão de TCAC | Relevância Geográfica | Cronograma de Impacto |

|---|---|---|---|

| Alto custo por bit vs. DRAM/NAND | -0.9% | Global, particularmente impactando aplicações sensíveis ao custo | Curto prazo (≤ 2 anos) |

| Escalada de potência em nós ≤5 nm | -0.7% | Fábricas avançadas na Ásia-Pacífico e América do Norte | Médio prazo (2-4 anos) |

| Deslocamento por NVM emergentes (MRAM/ReRAM) | -0.5% | Global, com adoção inicial em automotivo e industrial | Longo prazo (≥ 4 anos) |

| Perda de rendimento por variabilidade litográfica | -0.4% | Nós de processo avançados globalmente | Médio prazo (2-4 anos) |

| Fonte: Mordor Intelligence | |||

Alto custo por bit vs. DRAM/NAND

SRAM permaneceu várias vezes mais cara por bit do que DRAM commodity, pressionando designers a cortar uso em gadgets de mercado de massa. Preços de módulos DDR4 subiram aproximadamente 50% no H1 2025, ilustrando volatilidade ao longo da pilha de memória. A Samsung aproveitou o aperto de suprimento para elevar preços LPDDR4, mas essa tática arriscou acelerar interesse de OEMs em arquiteturas híbridas SRAM-DRAM para reduzir listas de materiais. Consequentemente, o mercado de Memória de Acesso Aleatório Estática enfrentou resistência em segmentos de consumo de entrada até que trade-offs densidade-versus-custo melhorassem.

Deslocamento por NVM emergentes (MRAM/ReRAM)

Junções de túnel magnético CoFeB/MgO de nanômetro único alcançaram comutação sub-10 ns e retenção de dez anos, permitindo que MRAM substituísse nvSRAM em sistemas robustos. A Everspin comercializou MRAM como substituto plug-in para SRAM com backup de bateria, oferecendo não-volatilidade sem capacitores externos. Fornecedores de FPGA automotivo como Lattice mudaram de flash para memória de configuração MRAM, mostrando adoção real.[2]Jim Tavacoli, "From Flash to MRAM," Lattice Semiconductor, latticesemi.com Se os custos de produção caírem ainda mais, uma parcela do mercado de Memória de Acesso Aleatório Estática poderia migrar para alternativas persistentes.

Análise de Segmentos

Por Função: Performance depende de arquiteturas síncronas

SRAM síncrona capturou 58,4% da participação do mercado de Memória de Acesso Aleatório Estática em 2024, sublinhando sua indispensabilidade para operação determinística de cache em CPUs, GPUs e ASICs de rede. MCUs automotivas usaram arrays síncronos para atender requisitos rigorosos de tempo real para cargas de trabalho de assistência ao motorista. O segmento manterá liderança à medida que nós avançados estendem envelopes de frequência e reduzem tensões de núcleo.

SRAM assíncrona expandiu a uma TCAC de 6,4% e cada vez mais serviu wearables IoT e gateways de borda onde orçamentos de energia superam alvos de latência. Projetos eficientes em energia eliminaram árvores de clock e simplificaram layouts de placa, uma vantagem para dispositivos de saúde operados por bateria empregando coprocessadores neurais da Syntiant. Esta divergência enfatizou a tendência do mercado de Memória de Acesso Aleatório Estática em direção à otimização específica de aplicação em vez de busca por performance universal.

Nota: Participações de segmentos de todos os segmentos individuais disponíveis mediante compra do relatório

Por Tipo de Produto: Pseudo-SRAM otimizada para custo prevalece

Pseudo-SRAM deteve uma participação de 54,4% em 2024 ao incorporar células DRAM por trás de uma interface estilo SRAM, alcançando maior densidade sem gerenciamento de refresh no nível do sistema. RAAAM Memory Technologies e NXP alegaram 50% de economia de área e 10× de potência versus SRAM clássica de alta densidade, atraindo microcontroladores de mercado de massa.

SRAM não-volátil cresceu mais rapidamente a 8,7% de TCAC à medida que fábricas e veículos demandaram integridade de dados durante quedas de tensão. Participantes de automação industrial selecionaram módulos nvSRAM para proteger variáveis de processo, evitando tempo de inatividade custoso. Embora nicho, este grupo enriqueceu o cenário do mercado de Memória de Acesso Aleatório Estática com recursos de resiliência de valor agregado.

Por Densidade de Memória: Faixa média permanece ponto ideal

O segmento de 8-64 Mb representou 42,3% do tamanho do mercado de Memória de Acesso Aleatório Estática em 2024, correspondendo a footprints típicos de cache L2/L3 em CPUs mainstream. A SRAM rápida de 32 Mb da Alliance Memory em embalagem FBGA ilustrou refinamento contínuo nesta zona.

Dispositivos >256 Mb registraram uma TCAC robusta de 7,5% à medida que aceleradores de IA buscaram caches on-chip maiores para minimizar buscas DRAM. A Micron projetou que automóveis logo carregariam 90 GB de memória total, sugerindo demanda crescente de SRAM de alta densidade em controladores zonais. A evolução da densidade, portanto, espelhou crescimento de cargas de trabalho intensivas em computação sustentando o mercado de Memória de Acesso Aleatório Estática.

Por Usuário Final: Volume de consumo vs. velocidade automotiva

Eletrônicos de consumo geraram 46,3% da receita de 2024 graças à vasta escala de smartphones, tablets e PCs. Micron e Samsung integraram LPDDR5X e SRAM on-board no Galaxy S24, elevando responsividade de IA móvel.

Segmentos automotivo e aeroespacial registraram uma TCAC de 9,1% à medida que veículos definidos por software requeriam cache determinística para fusão de sensores e reconfiguração over-the-air. O MCU S32K5 da NXP com RAM magnética incorporada escreve 15× mais rápido que flash, demonstrando o apetite por memória de alta confiabilidade.[3]NXP Semiconductors, "S32K5 MCU," stocktitan.net Tal momentum ampliou o mercado de Memória de Acesso Aleatório Estática além dos ciclos tradicionais de renovação de consumo.

Análise Geográfica

Ásia-Pacífico reteve 61,4% da participação do mercado de Memória de Acesso Aleatório Estática em 2024, impulsionada pelo domínio de foundry de Taiwan, inovação de memória da Coreia do Sul e esforços de escalonamento da China. A ascensão da SK Hynix a 36% da produção global de DRAM destacou a profundidade tecnológica da região. Ainda assim, o terremoto de 2024 em Taiwan expôs risco de concentração, levando a fábricas de contingência no Japão e Singapura. O Japão projetou vendas de equipamentos semicondutores de JPY 5,51 trilhões (US$ 38,35 bilhões) no AF26, sublinhando construção contínua de capacidade.

Oriente Médio e África traçaram a TCAC mais rápida de 7,5%, ancorada por gastos de fundos soberanos para posicionar o Golfo como um hub de dados tri-continental. Automação de armazéns na região estava definida para crescimento anual de 17,5% para US$ 1,6 bilhão até 2025, impulsionando demanda por caches on-board confiáveis. Projetos de energia da África destinaram US$ 730 bilhões em novo capex até 2030, requerendo sistemas de controle industrial que dependem de SRAM para resposta determinística.

América do Norte focou em implementações de datacenter de IA, enquanto a Europa dobrou a aposta na soberania através do Chips Act de EUR 43 bilhões. STMicroelectronics garantiu EUR 5 bilhões (US$ 5,4 bilhões) para um campus de Carbeto de Silício na Itália, ampliando competência regional em eletrônica de potência que também consomem SRAM especializada. Escassez de talentos, no entanto, ameaçou expansão, com ASML alertando que poderia mudar operações se imigração se apertasse. Estes contrastes destacam diversas alavancas regionais moldando o mercado de Memória de Acesso Aleatório Estática.

Cenário Competitivo

O mercado exibiu consolidação moderada em torno de fabricantes de dispositivos integrados e desafiantes alinhados a foundry. Samsung, SK Hynix e Micron fortificaram posições ao escalar roadmaps HBM; Samsung acelerou sua fab de wafer Pyeongtaek para capturar negócios HBM4. SK Hynix fez parceria com TSMC em embalagem avançada para sustentar liderança em largura de banda.[4]SK hynix, "Partners with TSMC to Strengthen HBM Leadership," skhynix.com

Na camada de IP e especialidade, GSI Technology e Cypress miraram equipamentos de rede de baixa latência, enquanto novatos como Numem planejaram chiplets MRAM prometendo throughput classe HBM até 2025. Imec, TSMC e Samsung-IBM cada um demonstraram protótipos SRAM CFET com redução de área de célula de 40%, antecipando híbridos de lógica-memória empilhados em 3D.

Nichos emergentes incluíram células 18T resistentes à radiação para satélites LEO que melhoraram estabilidade de leitura enquanto reduzem potência standby. Financiamento do Conselho Europeu de Inovação permitiu que RAAAM avançasse pseudo-SRAM on-chip para mercados MCU, ilustrando como política regional catalisou novos entrantes. Vantagem competitiva assim pivotou em inovação de embalagem, know-how de processo especializado e amplitude de propriedade intelectual, todos moldando posicionamento futuro do mercado de Memória de Acesso Aleatório Estática.

Líderes da Indústria de Memória de Acesso Aleatório Estática (SRAM)

-

Renesas Electronics Corporation

-

STMicroelectronics N.V.

-

Toshiba Corporation

-

Cypress Semiconductor

-

Integrated Silicon Solution, Inc. (ISSI)

- *Isenção de responsabilidade: Principais participantes classificados em nenhuma ordem específica

Desenvolvimentos Recentes da Indústria

- Julho de 2025: Samsung acelerou planta de wafer Pyeongtaek para garantir capacidade HBM4.

- Junho de 2025: Marvell introduziu SRAM personalizada de 2 nm entregando capacidade de 6 Gb com 66% menos potência.

- Junho de 2025: SK Hynix registrou aumento de lucro de KRW 9 trilhões na demanda HBM.

- Maio de 2025: Samsung e SK Hynix avançaram ligação híbrida para HBM de próxima geração.

Escopo do Relatório do Mercado Global de Memória de Acesso Aleatório Estática (SRAM)

SRAM (RAM estática) é memória de acesso aleatório (RAM) que retém bits de dados em sua memória enquanto energia estiver sendo fornecida. Diferentemente da RAM dinâmica (DRAM), que armazena bits em células consistindo de um capacitor e um transistor, SRAM não precisa ser periodicamente atualizada. RAM estática fornece acesso mais rápido a dados e é mais cara que DRAM.

| SRAM Assíncrona |

| SRAM Síncrona |

| Pseudo SRAM (PSRAM) |

| SRAM Não-Volátil (nvSRAM) |

| Outros Tipos de Produtos |

| ≤8 Mb |

| 8 - 64 Mb |

| 64 - 256 Mb |

| >256 Mb |

| Eletrônicos de Consumo |

| Industrial |

| Infraestrutura de Comunicação |

| Automotivo e Aeroespacial |

| Outros Usuários Finais |

| América do Norte | Estados Unidos | |

| Canadá | ||

| México | ||

| América do Sul | Brasil | |

| Argentina | ||

| Resto da América do Sul | ||

| Europa | Alemanha | |

| Reino Unido | ||

| França | ||

| Itália | ||

| Rússia | ||

| Resto da Europa | ||

| Ásia-Pacífico | China | |

| Japão | ||

| Coreia do Sul | ||

| Índia | ||

| Taiwan | ||

| Resto da Ásia-Pacífico | ||

| Oriente Médio e África | Oriente Médio | Turquia |

| Israel | ||

| Países do CCG | ||

| Resto do Oriente Médio | ||

| África | África do Sul | |

| Nigéria | ||

| Resto da África | ||

| Por Função | SRAM Assíncrona | ||

| SRAM Síncrona | |||

| Por Tipo de Produto | Pseudo SRAM (PSRAM) | ||

| SRAM Não-Volátil (nvSRAM) | |||

| Outros Tipos de Produtos | |||

| Por Densidade de Memória | ≤8 Mb | ||

| 8 - 64 Mb | |||

| 64 - 256 Mb | |||

| >256 Mb | |||

| Por Usuário Final | Eletrônicos de Consumo | ||

| Industrial | |||

| Infraestrutura de Comunicação | |||

| Automotivo e Aeroespacial | |||

| Outros Usuários Finais | |||

| Por Geografia | América do Norte | Estados Unidos | |

| Canadá | |||

| México | |||

| América do Sul | Brasil | ||

| Argentina | |||

| Resto da América do Sul | |||

| Europa | Alemanha | ||

| Reino Unido | |||

| França | |||

| Itália | |||

| Rússia | |||

| Resto da Europa | |||

| Ásia-Pacífico | China | ||

| Japão | |||

| Coreia do Sul | |||

| Índia | |||

| Taiwan | |||

| Resto da Ásia-Pacífico | |||

| Oriente Médio e África | Oriente Médio | Turquia | |

| Israel | |||

| Países do CCG | |||

| Resto do Oriente Médio | |||

| África | África do Sul | ||

| Nigéria | |||

| Resto da África | |||

Principais Perguntas Respondidas no Relatório

Qual é o valor atual do mercado de Memória de Acesso Aleatório Estática?

O mercado alcançou US$ 1,71 bilhão em 2025 e está previsto para subir para US$ 2,25 bilhões até 2030.

Qual região domina a receita do mercado de Memória de Acesso Aleatório Estática?

Ásia-Pacífico representou 61,4% da receita global em 2024, ancorada pelos ecossistemas de manufatura de Taiwan e Coreia do Sul.

Qual segmento do mercado de Memória de Acesso Aleatório Estática está crescendo mais rapidamente?

Aplicações automotivas e aeroespaciais estão expandindo a uma TCAC de 9,1% à medida que veículos adotam arquiteturas definidas por software requerendo caches de baixa latência.

Como a tecnologia MRAM emergente está impactando a demanda por SRAM?

MRAM oferece não-volatilidade e menor potência standby, desafiando SRAM em sistemas com backup de bateria e robustos, potencialmente desviando participação ao longo prazo.

Qual classe de densidade é mais comum nos chips SRAM de hoje?

A faixa de 8-64 Mb capturou 42,3% das vendas de 2024 porque se alinha com tamanhos de cache de processadores mainstream.

Por que SRAM síncrona superou tipos assíncronos em participação de receita?

Projetos sincronizados por clock fornecem timing determinístico essencial para CPUs, GPUs e ASICs de rede de alta performance, garantindo 58,4% da participação de mercado em 2024.

Página atualizada pela última vez em: