Silicon On Insulator Market Size and Share

Silicon On Insulator Market Analysis by Mordor Intelligence

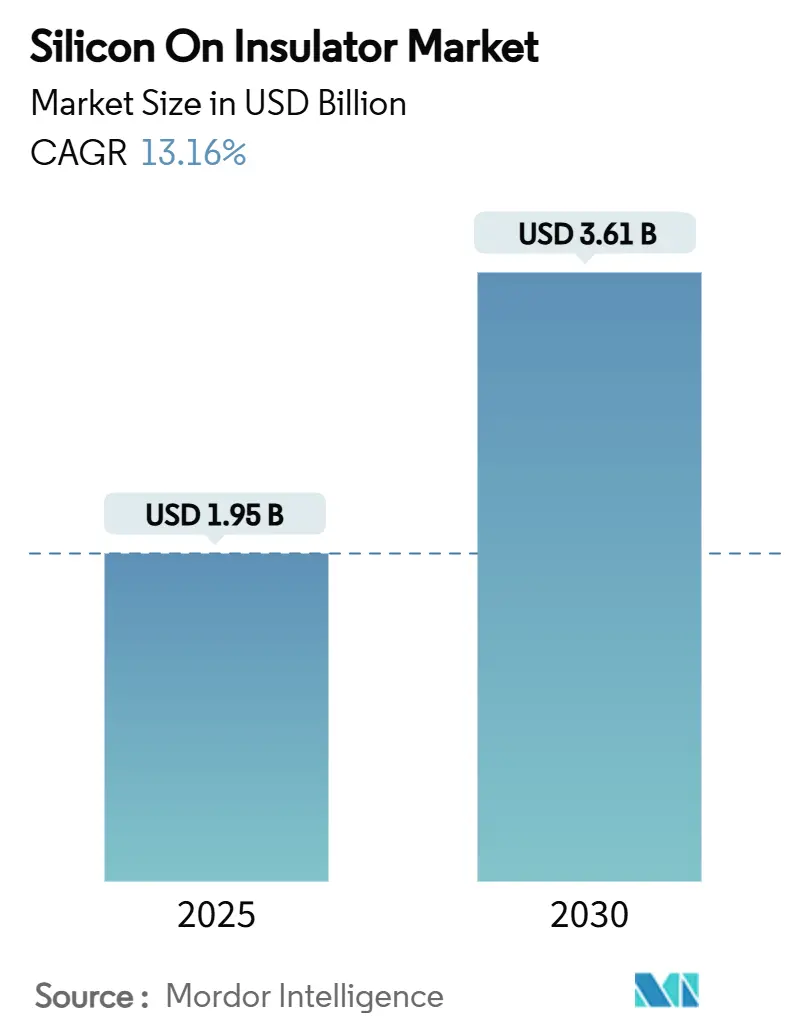

The Silicon on insulator market size stood at USD 1.95 billion in 2025 and is projected to reach USD 3.61 billion by 2030, advancing at a 13.16% CAGR over the forecast period. Accelerated adoption of fully depleted architectures in sub-7 nm logic, millimeter-wave RF front-ends for 5G/6G, and ultra-low-leakage memory arrays for edge-AI accelerators is expanding the addressable base for silicon-on-insulator substrates. Growing capital outlays by leading foundries to unlock 300 mm FD-SOI capacity, coupled with Smart Cut process refinements that support 5 nm-thin active layers, underpin long-term growth. Supply-side tightness, rooted in the limited number of licensees able to produce Smart Cut wafers, continues to buoy average selling prices, even as downstream device makers push for cost parity with bulk silicon. With automotive electrification, data-center photonics, and quantum-ready cryogenic control ICs crossing from pilot to early-production phases, the Silicon on insulator market is positioned for sustained double-digit expansion.

Key Report Takeaways

- By technology, Smart Cut held 52.18% of Silicon on insulator market share in 2024; the segment is forecast to grow at a 13.83% CAGR through 2030.

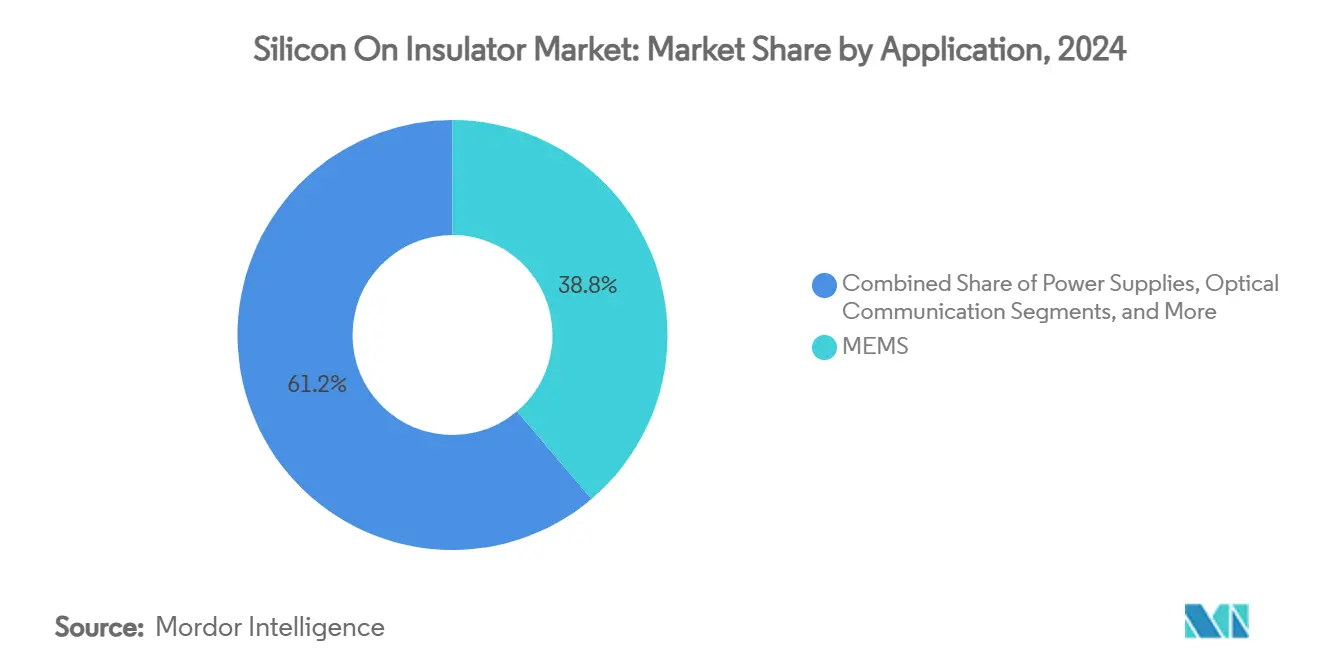

- By application, MEMS captured 38.82% share of the Silicon on insulator market size in 2024, while optical communication is slated to record the highest CAGR at 13.56% to 2030.

- By wafer size, Less than or equal to 200mm substrates accounted for 64.98% of Silicon on insulator market size in 2024, whereas 201mm and above wafers are expected to post a 13.19% CAGR by 2030.

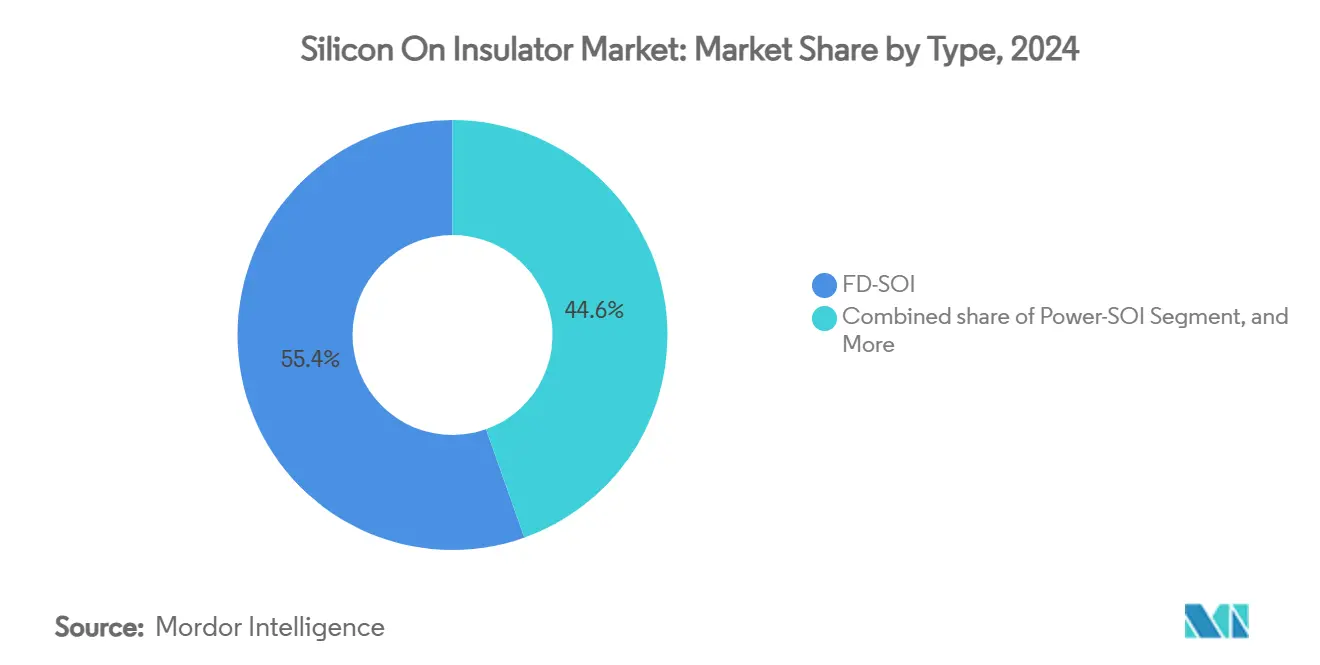

- By type, FD-SOI dominated with 55.43% Silicon on insulator market share in 2024 and is forecast to register a 13.61% CAGR through 2030.

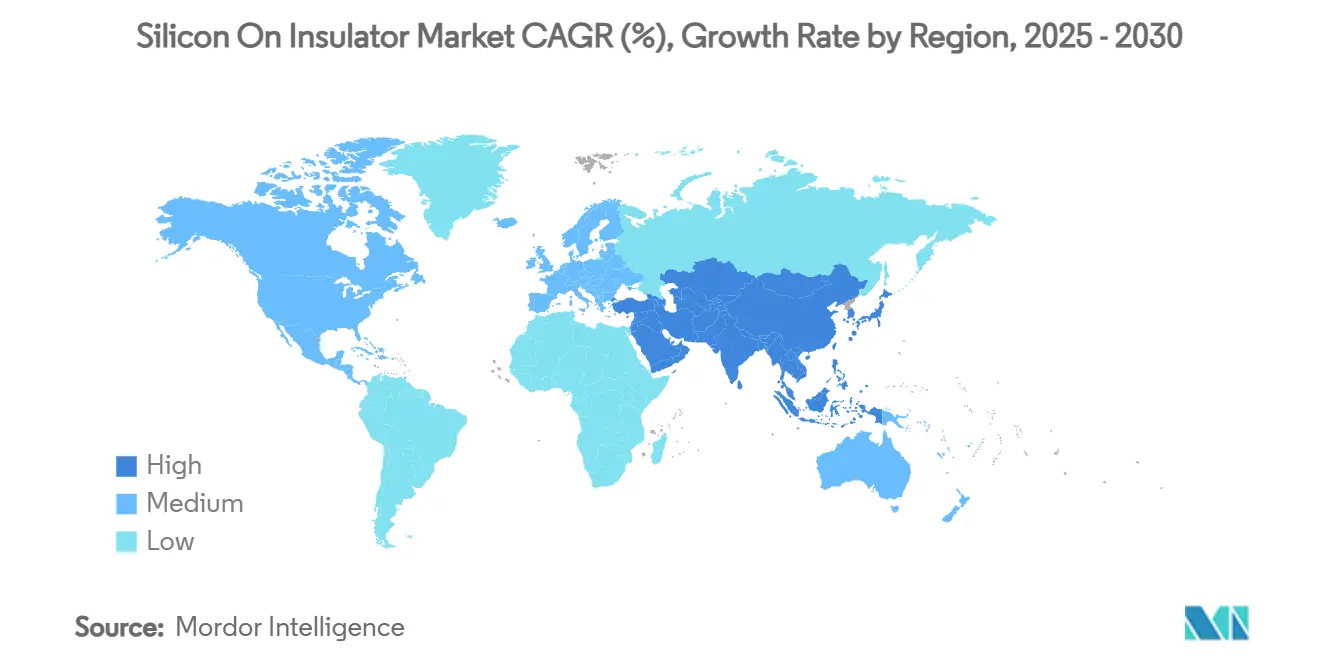

- By geography, Asia-Pacific led with 46.49% revenue share in 2024; the Middle East and Africa region is projected to expand at a 13.94% CAGR during 2025-2030.

Global Silicon On Insulator Market Trends and Insights

Drivers Impact Analysis

| Driver | (~) % Impact on CAGR Forecast | Geographic Relevance | Impact Timeline |

|---|---|---|---|

| Rapid adoption of FD-SOI for sub-7 nm logic | +2.4% | Global, Asia-Pacific leadership | Medium term (2-4 years) |

| High-efficiency power electronics in EVs | +1.8% | North America and EU, expanding to Asia-Pacific | Long term (≥ 4 years) |

| Integration of 5G/6G RF front-ends | +1.5% | Global, smartphone hubs | Short term (≤ 2 years) |

| Expanding smartphone image-sensor resolution | +1.2% | Asia-Pacific core, spill-over global | Medium term (2-4 years) |

| Edge-AI accelerators with ultra-low leakage | +0.8% | North America and EU, Asia-Pacific manufacturing | Medium term (2-4 years) |

| Quantum-computing control IC prototypes | +0.6% | North America and EU research centers | Long term (≥ 4 years) |

| Source: Mordor Intelligence | |||

Rapid adoption of FD-SOI for sub-7 nm low-power logic

Chipmakers migrating below 7 nm see FD-SOI as a cost-effective path that combines fully depleted channels with body-biasing to fine-tune threshold voltage on-the-fly. STMicroelectronics validated the approach by selecting 18 nm FD-SOI for next-generation microcontrollers, matching 16 nm FinFET performance while streamlining process complexity. [1]Robert Huntley, “STMicroelectronics Picks 18 nm FD-SOI for Next-Gen MCUs,” EE Times Europe, eetimes.euBody-bias enables sub-threshold swings of 7 mV/dec at cryogenic temperatures, extending use cases to IoT and automotive domains where battery life or stability under harsh conditions is paramount. Samsung Foundry’s expanded FD-SOI roadmap signals consensus that classic planar scaling faces diminishing returns that SOI can offset. Foundries already equipped for FD-SOI gain a timing and cost advantage because the platform reuses much of the existing CMOS toolset.

Rising demand for high-efficiency power electronics in EVs

Automakers are pivoting to 800 V drivetrains, forcing traction inverters to handle higher switching frequencies with minimal conduction loss. onsemi’s EliteSiC M3e platform, adopted by Volkswagen Group, embeds SOI-based driver and control ICs next to SiC dies to trim stray capacitance and thermal impedance, yielding measurable mileage gains. [2]Soitec, “Connect RFeSI SOI,” soitec.comIn industrial renewables, ROHM’s 2 kV SiC MOSFETs housed within Semikron Danfoss modules underline SOI’s ability to preserve isolation integrity under cosmic-radiation exposure, a growing reliability requirement for large-scale solar installations. Given 15-year automotive design cycles, design-wins secured today translate into steady substrate demand well beyond the forecast window.

Integration of 5G/6G RF front-ends

Handset makers pressed by tighter form factors are consolidating power amplifiers, filters, and switches on single dies. Tower Semiconductor’s 300 mm RFSOI platform delivered Wi-Fi 7 front-end modules for Broadcom, replacing multi-chip solutions and slashing insertion loss across 2.4–7 GHz. Soitec’s trap-rich RFeSI wafers achieve harmonic quality factors above 50, crucial for stable millimeter-wave transmission. [3]onsemi, “onsemi Selected to Power Volkswagen Group's Next-Generation Electric Vehicles,” onsemi.com NXP extended its 28 nm RF-CMOS radar line on SOI to integrate transceiver arrays with on-chip processing, proving viability for software-defined vehicles. Rapid 5G rollouts and annual smartphone refresh cycles translate into immediate substrate pull.

Expanding smartphone image-sensor resolution

Mobile cameras surpassing 100 MP force pixel pitches below 0.7 µm, increasing crosstalk risk. Stacked CMOS sensors implemented on 45 nm SOI processes attain dark currents of 3.2 e ⁄s at 60 °C while preserving 0.90 e- rms read noise. The buried oxide layer improves electrical isolation without sacrificing optical stack integrity. Sony’s sustained leadership in premium image sensors relies on SOI-compatible back-side illumination flows that maintain quantum efficiency at nano-scale depths. SOI also supports near-infrared sensing for AR and biometric unlock, broadening revenue potential.

Restraints Impact Analysis

| Restraint | (~) % Impact on CAGR Forecast | Geographic Relevance | Impact Timeline |

|---|---|---|---|

| Premium wafer cost versus bulk silicon | -1.5% | Global, cost-sensitive segments | Short term (≤ 2 years) |

| Limited foundry capacity for 300 mm FD-SOI | -0.9% | Global, advanced-node facilities | Medium term (2-4 years) |

| Smart Cut license concentration risk | -0.7% | Europe-centric licensing pool | Medium term (2-4 years) |

| TSV yield challenges in 3D integration | -0.4% | Global R&D hubs | Long term (≥ 4 years) |

| Source: Mordor Intelligence | |||

Premium wafer cost versus bulk silicon

SOI substrates command 2–3 times the price of comparable bulk wafers because Smart Cut entails bonding, layer transfer, and polishing steps absent from conventional Czochralski growth. This premium compresses margins in high-volume consumer devices where bill-of-materials targets dominate supplier decisions. While 5G smartphones accept RF-SOI for performance reasons, many mid-range models revert to bulk silicon alternatives. Automotive and aerospace segments tolerate higher costs due to mission-critical reliability requirements, muting the near-term impact in those end-markets.

Limited foundry capacity for 300 mm FD-SOI

GlobalFoundries remains the only high-volume FD-SOI supplier, rendering fabless firms vulnerable to capacity crunches. Lead times for automotive-grade FD-SOI wafers have stretched to 26 weeks, double bulk equivalents. Samsung’s investment thrust favors FinFET and GAA nodes, while TSMC’s FD-SOI offering is limited, reinforcing bottlenecks. Design teams therefore commit early to secure allocation, trading technology flexibility for guaranteed supply—an imbalance likely to persist until GlobalWafers’ Texas fab and similar projects come online after 2027.

Segment Analysis

By Type: FD-SOI Dominates Advanced Applications

FD-SOI captured 55.43% Silicon on insulator market share in 2024 and is forecast to post a 13.61% CAGR to 2030. The platform’s fully depleted channel suppresses random-dopant fluctuation and short-channel effects, stabilizing threshold voltage across devices even at cryogenic temperatures. Automotive microcontrollers and battery-powered IoT nodes value body-biasing, which allows real-time power-performance tuning without added geometry complexity.

Partially depleted SOI retains relevance for high-voltage functions where charge sharing still meets tolerance windows, while Power-SOI targets gate-driver ASICs that interface directly with SiC switches. Niche categories addressing quantum control or specialty MEMS round out the type mix. Competitive differentiation hinges on wafer uniformity and defect density; vendors exhibiting <0.12 defects /cm² command premium contracts. As FD-SOI continues penetrating sub-10 nm designs, its share within the Silicon on insulator market is expected to edge past 58% by 2030.

By Wafer Size: The 300 mm Shift Accelerates

Wafers less than or equal to 200mm represented 64.98% of Silicon on insulator market size in 2024, reflecting entrenched RF and MEMS volumes that run cost-effectively on legacy fabs. Yet the 201mm and above band is forecast to advance at 13.19% CAGR, outpacing the overall Silicon on insulator market. Larger diameters lower die cost for high-density systems-on-chip and permit adoption of EUV lithography, essential for tight overlay control in 5G beam-forming arrays.

GlobalWafers’ USD 4 billion Texas investment earmarks a new dedicated 300 mm SOI line, signalling confidence that automotive ADAS and server-class photonics will migrate to 12-inch wafers for supply assurance. Legacy 150 mm lines will continue serving specialty MEMS where tool amortisation is complete, creating a dual-track supply chain.

By Technology: Smart Cut Maintains Innovation Lead

Smart Cut held 52.18% share in 2024 and is projected to grow at 13.83% CAGR, exceeding overall Silicon on insulator market growth. The method’s precision in cleaving ultra-thin active layers, as small as 5 nm, enables vertical 3D integration that pushes past planar scaling limits. Soitec’s partnership with PSMC to commercialise Transistor Layer Transfer underscores Smart Cut’s adaptability to heterogeneous stacking.

Bonding SOI and Layer Transfer SOI occupy research or low-volume niches where process flexibility trumps cost. Their combined share is likely to decline slightly as Smart Cut patents expire post-2028, widening access for second-source suppliers.

By Application: MEMS Leadership Meets Optical Surge

MEMS devices commanded 38.82% of Silicon on insulator market size in 2024, leveraging buried oxide as an etch-stop that simplifies deep-reactive ion etching for inertia sensors and micro-mirrors. Stable mechanical properties across-40 °C to 150 °C suit automotive and industrial environments.

Optical communication, however, tops growth at 13.56% CAGR, propelled by 400G/800G datacenter interconnects and future 1.6 Tbps optics demonstrated by Tower Semiconductor and OpenLight. Silicon photonics exploits the high refractive index delta between silicon and buried oxide to confine light tightly, shrinking modulator footprints and energy per bit. Diverse power-supply, image-sensing, and emerging quantum applications keep the demand profile broad, insulating suppliers from single-segment swings.

By End User Vertical: Automotive Disrupts Consumer Primacy

Consumer electronics still led with 35.28% share in 2024, driven by smartphones that integrate RF-SOI front-ends and high-resolution image sensors. Design cycles of 12–18 months sustain predictable wafer pull.

Automotive exhibits the highest 13.43% CAGR as EV powertrains and ADAS radar shift toward SOI for radiation hardness and thermal stability. Vehicle architectures moving from 12 V to 48 V boost demand for Power-SOI gate drivers. Aerospace, industrial automation, and telecom infrastructure add incremental volume, each valuing SOI’s isolation benefits in harsh operating envelopes.

Geography Analysis

Asia-Pacific’s 46.49% share in 2024 reflects manufacturing cluster effects spanning substrate vendors, foundries, and OSAT houses. Shin-Etsu, TSMC, Samsung, and UMC together anchor a tight supply-chain radius that cuts transit times and inventories. Japan’s USD 6 billion subsidy to TSMC’s Kumamoto project highlights sovereign interest in safeguarding SOI-enabled advanced nodes. Chinese entrants are building local substrate competence, but remain behind in Smart Cut yield mastery, preserving Soitec’s edge.

North America benefits from GlobalFoundries’ and GlobalWafers’ domestic expansions aligned with CHIPS Act incentives. These moves shorten lead times for automotive and aerospace primes and lift the region’s share of the Silicon on insulator market size. Europe continues to punch above its capacity weight thanks to design-in wins among premium automotive OEMs and industrial automation leaders that specify FD-SOI for functional-safety reasons.

Middle East and Africa, starting from a low base, posts the fastest 13.94% CAGR through 2030. Saudi Arabia’s National Semiconductor Hub targets relocation of 50 design houses by decade-end, creating green-field demand for foundry partners able to prototype mixed-signal chips on SOI. Nascent solar and telecom rollouts across North Africa could further catalyse Power-SOI pull as infrastructure spending accelerates.

Competitive Landscape

Upstream substrate supply is highly concentrated. Soitec’s Smart Cut patent estate underpins >50% revenue share and affords pricing leverage over global foundries. Shin-Etsu and GlobalWafers provide alternative wafers yet rely on long-term contracts to secure Smart Cut licenses, curbing aggressive price competition.

Midstream, GlobalFoundries leads FD-SOI at 22FDX and 12FDX nodes, with a USD 16 billion expansion plan that will double output in New York by 2028. Samsung balances FD-SOI with gate-all-around research, while TSMC’s limited SOI mix keeps focus on high-margin FinFET. Tower Semiconductor differentiates via 300 mm RFSOI and silicon photonics, addressing handset RF and datacenter optics respectively.

Downstream, design-wins in automotive radar and 5G modems translate directly into substrate pull-through. The emergence of cryogenic control ICs for quantum computing opens a green-field niche where SOI’s low leakage at 4 K outperforms bulk. Patent expiry in the late-2020s could loosen Soitec’s grip, yet new IP around layer-transfer logistics is already extending the moat.

Silicon On Insulator Industry Leaders

Soitec

Shin-Etsu Chemical Co., Ltd.

GlobalWafers Co., Ltd.

STMicroelectronics N.V.

Samsung Electronics Co., Ltd.

- *Disclaimer: Major Players sorted in no particular order

Recent Industry Developments

- June 2025: Soitec and PSMC unveiled transistor layer-transfer collaboration for 5 nm-class 3D stacking.

- June 2025: GlobalFoundries committed USD 16 billion to boost FDX capacity in the United States.

- May 2025: GlobalWafers raised total U.S. investment to USD 7.5 billion, adding 300 mm SOI output in Texas.

- April 2025: ROHM introduced 2 kV SiC MOSFETs within Semikron Danfoss modules for large-scale PV inverters.

Global Silicon On Insulator Market Report Scope

| Fully Depleted Silicon on Insulator (FD-SOI) |

| Partially Depleted Silicon on Insulator (PD-SOI) |

| Power-SOI |

| Others |

| Less than or equal to 200mm |

| 201mm and above |

| Bonding SOI |

| Layer Transfer SOI |

| Smart Cut |

| MEMS |

| Power Supplies |

| Optical Communication |

| Image Sensing |

| Others |

| Consumer Electronics |

| Automotive |

| IT and Telecommunication |

| Aerospace and Defense |

| Industrial |

| Others |

| North America | United States |

| Rest of North America | |

| South America | Brazil |

| Rest of South America | |

| Europe | Germany |

| France | |

| Rest of Europe | |

| Asia-Pacific | China |

| Japan | |

| India | |

| South Korea | |

| Taiwan | |

| Rest of Asia-Pacific | |

| Middle East and Africa | Middle East |

| Africa |

| By Type | Fully Depleted Silicon on Insulator (FD-SOI) | |

| Partially Depleted Silicon on Insulator (PD-SOI) | ||

| Power-SOI | ||

| Others | ||

| By Wafer Size | Less than or equal to 200mm | |

| 201mm and above | ||

| By Technology | Bonding SOI | |

| Layer Transfer SOI | ||

| Smart Cut | ||

| By Application | MEMS | |

| Power Supplies | ||

| Optical Communication | ||

| Image Sensing | ||

| Others | ||

| By End User Vertical | Consumer Electronics | |

| Automotive | ||

| IT and Telecommunication | ||

| Aerospace and Defense | ||

| Industrial | ||

| Others | ||

| By Geography | North America | United States |

| Rest of North America | ||

| South America | Brazil | |

| Rest of South America | ||

| Europe | Germany | |

| France | ||

| Rest of Europe | ||

| Asia-Pacific | China | |

| Japan | ||

| India | ||

| South Korea | ||

| Taiwan | ||

| Rest of Asia-Pacific | ||

| Middle East and Africa | Middle East | |

| Africa | ||

Key Questions Answered in the Report

What CAGR is projected for the Silicon on insulator market through 2030?

The market is forecast to grow at 13.16% per year, reaching USD 3.61 billion by 2030.

Which region will add the fastest incremental revenue?

The Middle East & Africa region is expected to expand at a 13.94% CAGR, outpacing all other geographies.

Why is FD-SOI preferred for sub-7 nm low-power chips?

FD-SOI offers fully depleted channels and dynamic body-biasing, which lower leakage and simplify fabrication compared with FinFET at similar nodes.

How does wafer diameter impact cost in SOI manufacturing?

Transitioning from 200 mm to 300 mm wafers improves die output per run, lowering unit cost and supporting high-volume automotive and consumer applications.

What is the main bottleneck limiting SOI supply?

Limited 300 mm FD-SOI capacity—primarily at GlobalFoundries—extends lead times and constrains fabless adoption in fast-growing sectors.

Page last updated on: