Programmable ASIC Market Size and Share

Programmable ASIC Market Analysis by Mordor Intelligence

The programmable ASIC market size was valued at USD 20.22 billion in 2025 and estimated to grow from USD 21.99 billion in 2026 to reach USD 33.51 billion by 2031, at a CAGR of 8.79% during the forecast period (2026-2031). The current expansion phase reflects the semiconductor sector’s sharpened focus on application-specific solutions that outperform general-purpose processors while avoiding the rigidity of fixed ASICs. Adoption has advanced most rapidly where the economics of scale coincide with compute-intensive workloads, most visibly inside hyperscale data-center footprints, advanced driver-assistance stacks, 5G radio units, and high-volume IoT form factors. Foundry investment in advanced packaging, particularly chiplet-based integration, is further widening the addressable envelope by letting designers co-opt mature and leading-edge nodes within single multi-die systems. At the same time, national security priorities and the global push for supply-chain resilience are nudging critical-infrastructure buyers toward domestically sourced programmable devices that embed hardware-level security features.

Key Report Takeaways

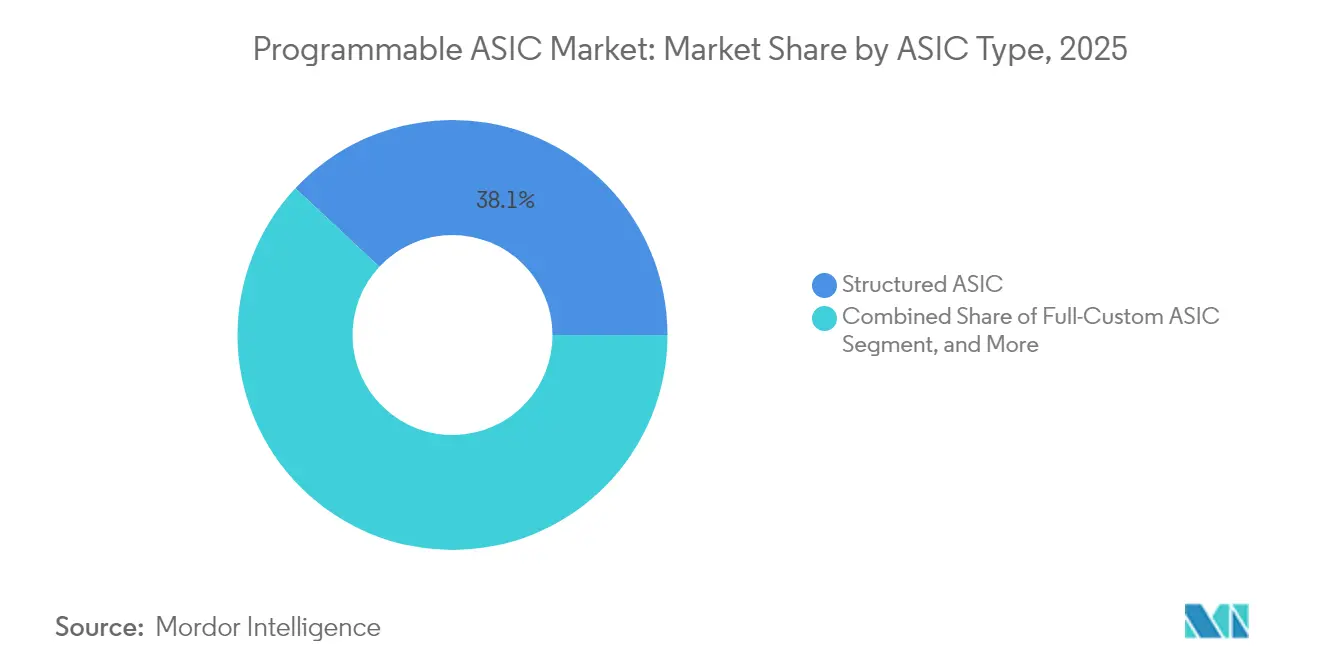

- By ASIC type, structured devices led with 38.05% of programmable ASIC market share in 2025; RF ASICs are projected to expand at a 9.42% CAGR through 2031.

- By end-use industry, consumer electronics accounted for 31.10% share of the programmable ASIC market size in 2025, while automotive and transportation is advancing at a 9.25% CAGR to 2031.

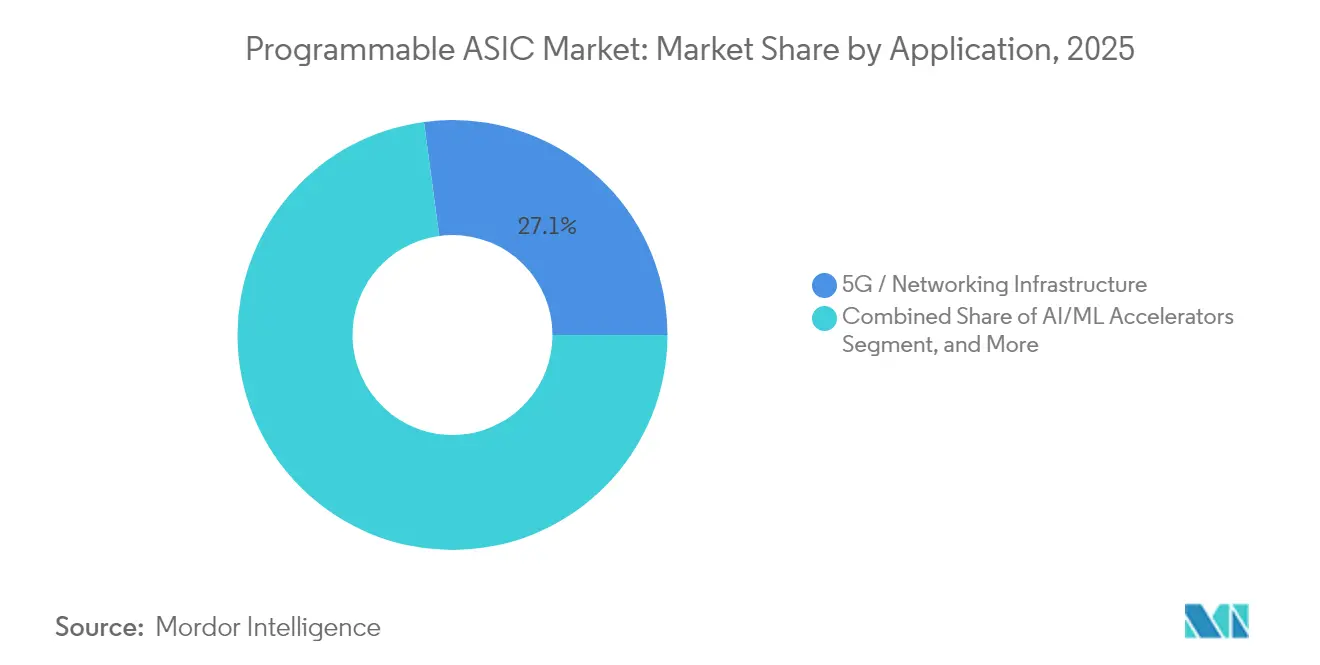

- By application, 5G and networking hardware accounted for a 27.12% share of the programmable ASIC market size in 2025, while AI/ML accelerators are advancing at a 9.18% CAGR to 2031.

- By process node, mature technologies above 28 nm captured the largest slice at 43.05% in 2025 in the programmable ASIC market, whereas designs taped out on 5/4/3 nm are on track to grow 9.76% per year to the end of the decade.

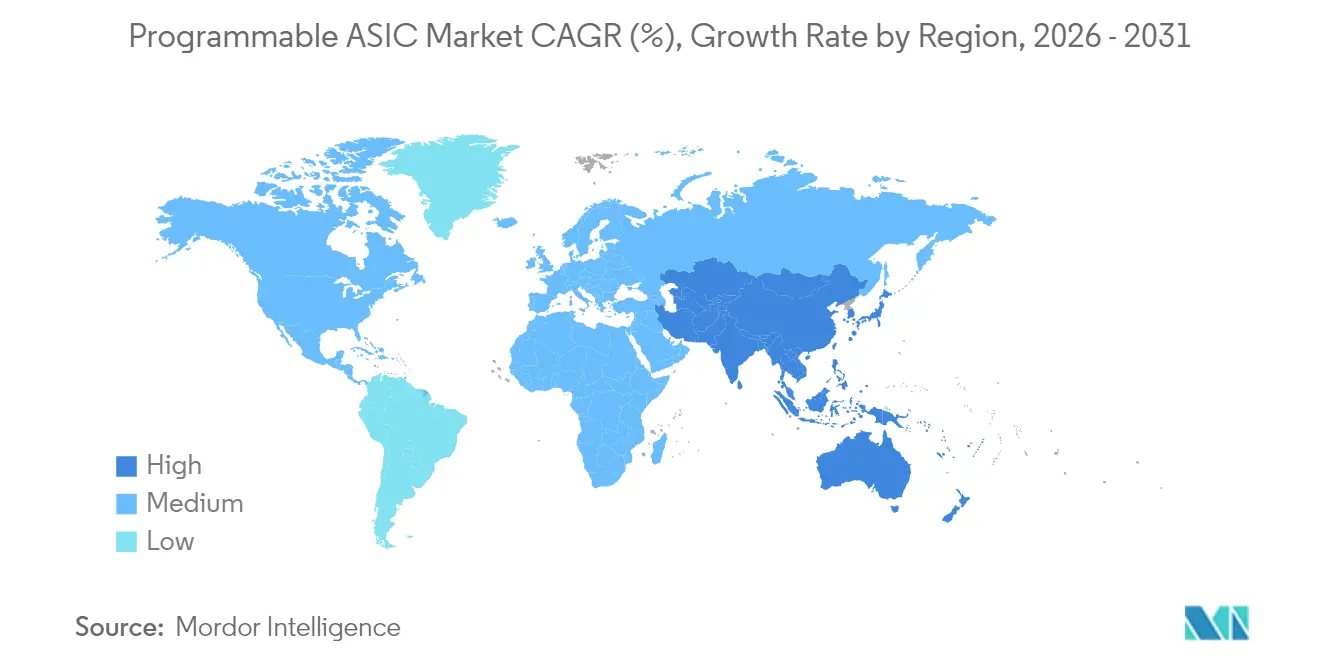

- By geography, North America retained 38.20% revenue leadership in 2025 in the programmable ASIC market; Asia Pacific is poised for the fastest regional expansion at a 9.61% CAGR to 2031.

Note: Market size and forecast figures in this report are generated using Mordor Intelligence’s proprietary estimation framework, updated with the latest available data and insights as of 2026.

Global Programmable ASIC Market Trends and Insights

Drivers Impact Analysis*

| Driver | (~) % Impact on CAGR Forecast | Geographic Relevance | Impact Timeline |

|---|---|---|---|

| Proliferation of IoT and edge devices | +2.1% | Global, with APAC manufacturing concentration | Medium term (2-4 years) |

| Adoption of AI/ML accelerators | +1.8% | North America and China leading, EU emerging | Short term (≤ 2 years) |

| Rapid deployment of 5G infrastructure | +1.6% | Global, with Asia Pacific early deployment | Medium term (2-4 years) |

| Automotive shift toward ADAS and electrification | +1.4% | North America and Europe regulatory-driven, China volume | Long term (≥ 4 years) |

| Chiplet-based heterogeneous integration boosts structured ASIC uptake | +1.2% | North America and Taiwan foundry ecosystem | Medium term (2-4 years) |

| Defense push for on-shore secure reconfigurable ASICs (CHIPS Act) | +0.8% | North America, with allied nation partnerships | Long term (≥ 4 years) |

| Source: Mordor Intelligence | |||

Proliferation of IoT and Edge Devices

Growth in connected-sensor endpoints is prompting OEMs to favor silicon that balances low-power operation with the headroom to execute evolving algorithms. Programmable ASICs meet this need by delivering a power-per-operation profile that outperforms microcontrollers yet retains post-fabrication flexibility. Shipments of AI-enabled wearables, for example, surpassed 10 million units in 2025, illustrating volume economics that justify custom masks. Hardware-rooted security functions embedded at the metal-layer level help makers comply with pending device-authentication regulations. As smart-home appliances, industrial probes and medical wearables converge around always-on inference, the programmable ASIC market is expected to benefit from a steady migration away from purely software-defined solutions.

Adoption of AI/ML Accelerators

Cloud operators now view proprietary inference engines as a hedge against GPU supply constraints and as an efficiency lever capable of trimming total cost of ownership by up to 40% on workload-stable fleets. Customer demand for high-bandwidth memory, vector engines and low-latency interconnects has moved the center of gravity toward chiplet-enabled structured ASICs, which offer a middle path between FPGAs and full-custom silicon. Industry leaders that can pair advanced-node design with vertically integrated packaging have already secured multi-year purchase commitments, underscoring the durable pull of AI-specific devices in the programmable ASIC market.

Rapid Deployment of 5G Infrastructure

The step-up from 4G to 5G Massive-MIMO radios requires precise beam-forming and mmWave power-amplifier control, functions ill-suited to off-the-shelf processors. Mixed-signal programmable ASICs fabricated on specialty RF processes such as 6 nm N6RF+ from TSMC are helping base-station makers shrink power budgets while condensing board real estate.[1]Taiwan Semiconductor Manufacturing Company, “N2 Technology Update,” tsmc.com Regional rollouts are dictating divergent demand profiles: Asia Pacific operators emphasize coverage density, whereas European carriers concentrate on network slicing for enterprise. Across all geographies, stricter security directives are steering telecom OEMs toward silicon vendors with proven hardware root-of-trust IP.

Chiplet-Based Heterogeneous Integration

With advanced mask sets now surpassing USD 50 million, the economics of monolithic SoCs are tilting toward disaggregated die-level construction. High-density bridges such as TSMC’s CoWoS and Intel’s EMIB enable programmable ASIC vendors to drop in hardened analog, RF or security tiles next to compute logic while maintaining package-level power integrity.[2]MediaTek, “N6RF+ Process Announcement,” mediatek.com The arrival of open UCIe interfaces is broadening multi-vendor collaboration, giving structured ASIC suppliers a standard on-ramp to heterogeneous systems that were historically closed ecosystems.

Restraints Impact Analysis*

| Restraint | (~) % Impact on CAGR Forecast | Geographic Relevance | Impact Timeline |

|---|---|---|---|

| High NRE and mask costs at advanced nodes | -1.5% | Global, with concentration at leading foundries | Short term (≤ 2 years) |

| Foundry capacity constraints and supply shocks | -1.2% | Global, with TSMC dependency creating bottlenecks | Medium term (2-4 years) |

| Rising design complexity lengthening time-to-market | -0.8% | North America and Europe design centers, APAC manufacturing | Medium term (2-4 years) |

| Open-source hardware (RISC-V) diluting proprietary ASIC demand | -0.6% | Global, with strongest adoption in China and emerging markets | Long term (≥ 4 years) |

| Source: Mordor Intelligence | |||

High NRE and Mask Costs at Advanced Nodes

Steep non-recurring engineering outlays at 3 nm and below are discouraging lower-volume projects and pushing mid-tier customers toward structured or mature-node alternatives. Design teams must master complex tool chains and guard-band for variability, inflating both schedule and tape-out risk. Foundry concentration amplifies bargaining asymmetry: wafer pricing at leading nodes continues to rise as capacity books out 12 months in advance, limiting agile pivots to new designs.

Foundry Capacity Constraints and Supply Shocks

A single advanced-node supplier currently holds more than two-thirds of global 5 nm-class output, making the supply chain vulnerable to geopolitical or natural-disaster disruptions. Spot allocations during the 2024–2025 shortage commanded premiums as high as 25% above contract pricing, squeezing gross margins for fab-less programmable ASIC providers. While SEMI expects 18 new fabs to break ground in 2025, most additional wafer starts are on mature technologies, leaving leading-edge tightness largely intact.[3]SEMI, “World Fab Forecast Q1 2025,” semi.org

*Our updated forecasts treat driver/restraint impacts as directional, not additive. The revised impact forecasts reflect baseline growth, mix effects, and variable interactions.

Segment Analysis

By ASIC Type: Structured Devices Anchor the Flexibility–Performance Continuum

Structured designs accounted for 38.05% of programmable ASIC market revenue in 2025, underscoring their status as the default option for projects that demand moderate customization with lower tape-out risk. Because only the top metal layers vary, mask sets can be turned around faster and at a fraction of full-custom cost, letting OEMs hit consumer-electronics rhythms without ceding performance. In contrast, RF ASICs, buoyed by 5G mmWave and satellite-link deployments, are forecast to post a 9.42% CAGR to 2031, the swiftest clip among all device classes. RF variants integrate low-noise amplifiers, phase shifters and power stages into single die, eliminating board-level tuning steps that once slowed carrier certification.

Full-custom implementations remain indispensable where watt-per-tera-operation efficiency drives hyperscale economics, but they now coexist with chiplet-sized structured blocks inside the same multichip modules. Mixed-signal flavors are gaining visibility as IoT nodes, automotive radar and smart-factory sensors all require high-accuracy ADCs stitched to digital logic. Crucially, the advent of dielectric bridge packaging is letting foundries marry analog-optimized mature nodes with bleeding-edge compute tiles, raising the ceiling on structured ASIC applicability without penalizing bill-of-materials cost.

Note: Segment shares of all individual segments available upon report purchase

By End-Use Industry: Consumer Electronics Retains Volume Lead as Mobility Applications Accelerate

Mobile and home-entertainment brands kept consumer electronics at the top of the revenue table in 2025, driven by demand for display engines, connectivity chipsets and battery-life optimizers that exceed the efficiency envelope of off-the-shelf processors. The shift toward edge AI audio and video enhances silicon content per device, locking in a multi-year refresh cycle favorable to the programmable ASIC market. Automotive OEMs, while smaller by shipment volume, are staging the fastest proportional gains as software-defined vehicles roll out centralized compute and zonal architectures. Safety-critical requirements under ISO 26262 necessitate deterministic timing and hardware redundancy that programmable ASICs are well-placed to deliver.

Industrial equipment builders and collaborative-robot manufacturers are also ramping custom silicon footprints, attracted by the ability to fuse real-time control loops with machine-vision acceleration inside fan-less thermal envelopes. In the medical domain, wearable biosensors and imaging modalities are leveraging ultra-low-power front-ends supplied on validated 180 nm and 110 nm nodes, reaffirming that mature-node programmability remains commercially relevant. Telecom vendors continue to lean on high-throughput network processors that embed adaptive pipelines capable of future standards upgrade, reinforcing the segment’s steady mid-single-digit growth outlook.

By Application: 5G Infrastructure Dominates While AI/ML Chips Chart Fastest Curve

At 27.12% of 2025 revenue, 5G and networking hardware represents the single largest application cluster for programmable devices, reflecting the silicon-intensive nature of Massive-MIMO baseband, beam-forming and fronthaul encryption tasks. OEM differentiation is increasingly delivered in hardware, driving successive spins of structured ASIC co-processors each time the 3GPP release cadence adds new numerology or extended-reality service slices. AI/ML accelerators, however, are outpacing every other vertical with a projected 9.18% CAGR, courtesy of escalating model sizes, prompt-engineering complexity, and the steady migration of inference to on-premise and edge tiers.

Within data centers, custom load-balancing, storage-offload and smart-NIC silicon are rounding out demand as hyperscalers chase sub-microsecond latency targets. Automotive perception stacks and sensor-fusion cores add another growth vector by embedding dedicated neural-network blocks tuned for radar point-cloud interpolation and camera object classification. Smart-factory gateways employ programmable ASICs to merge fieldbus translation, time-sensitive networking and anomaly-detection inference in a single hardened design, eliminating multi-board latency penalties.

Note: Segment shares of all individual segments available upon report purchase

By Process Node: Mature Technologies Still Rule the Volume Game

Mature geometries above 28 nm held 43.05% of 2025 shipments, a testament to their proven yields, broad IP libraries, and attractive cost structures. These nodes are staple choices for power-management ICs, connectivity combos, and mixed-signal modules that dominate consumer electronics and industrial IoT rollouts. Yet the drive for higher compute density is lifting 5/4/3 nm tape-outs at a 9.76% CAGR, especially for AI inference engines and next-generation automotive domain controllers that demand aggressive watt-per-tera-operation metrics.

Intermediate nodes at 16/14 nm and 10/7 nm serve as migration stepping stones, capturing workloads that cannot absorb the cost premium of the most advanced geometries but still need meaningful performance bumps over 28 nm. Specialty variants, N6RF+ for high-efficiency radio front-ends and 22FDX for ultra-low-leakage sensor hubs, illustrate how foundries are tailoring mature processes to sustain long-term relevance. Incentives embedded in regional semiconductor acts are simultaneously nudging defense and aerospace buyers to specify nodes that can be fabbed domestically, subtly reshaping the process-node mix inside the programmable ASIC market.

Geography Analysis

North America topped 2025 revenue tables at a 38.20% programmable ASIC market share, an outcome propelled by hyperscale data-center investments, CHIPS Act incentives and long-standing design-service density clustered around Silicon Valley, Austin and Phoenix. Domestic foundry expansions, Intel’s USD 20 billion Arizona build-out among them, strengthen local supply resilience while opening advanced-node access for defense-oriented secure devices.

Asia Pacific is primed for the quickest 2026-2031 climb at a forecast 9.61% CAGR, anchored by sovereign capacity drives in China, South Korea’s vertically integrated memory-logic supercluster, and Japan’s equipment and materials depth. Capital expenditure pledges north of USD 470 billion across the region through 2028 support both mature and bleeding-edge capacity adds, lowering entry hurdles for regional fab-less startups.

Europe maintains a disciplined growth trajectory, using functional-safety regulation and carbon-neutral manufacturing goals to differentiate its automotive and industrial electronics sectors. Localized wafer fabrication initiatives in Germany and the planned TSMC Dresden joint venture are expected to add downstream packaging and test ecosystems, giving EU system houses shorter supply lines and IP-protection assurances.

Competitive Landscape

Market concentration is moderate, with the top five suppliers controlling roughly 55-60% of programmable ASIC revenue, while a long tail of fab-less specialists exploits niche workloads. Broadcom’s traction in custom inference engines underscores the strength of turnkey design-through-assembly offerings. TSMC, by virtue of 5 nm and CoWoS capacity, remains the indispensable manufacturing node for high-performance devices, yet its dominance also constitutes a systemic risk acknowledged by end customers.

Intel has re-entered the merchant silicon conversation through its Foundry Services unit, pitching a U.S.-based alternative for security-sensitive workloads and providing a convergence point for design ecosystems that straddle x86, Arm and RISC-V IP. Start-ups building on open-source ISA blocks are cutting licensing overhead and accelerating time-to-prototype, though many still rely on established houses for packaging and high-volume qualification.

Advanced packaging stands out as the new competitive battleground. Vendors that align proprietary chiplet IP with high-bandwidth memory stacks and best-in-class reticle-limit interposers are gleaning design wins that once defaulted to monolithic approaches. Regulatory currents favor suppliers that can demonstrate end-to-end chain-of-custody, radiation tolerance and zero-trust security features, subtly shifting commercial leverage toward vertically integrated or government-backed players.

Programmable ASIC Industry Leaders

Analog Devices, Inc.

Infineon Technologies AG

STMicroelectronics

Texas Instruments Inc.

NXP Semiconductors N.V.

- *Disclaimer: Major Players sorted in no particular order

.webp)

Recent Industry Developments

- May 2025: TSMC signaled record demand for its 2 nm node with multi-year capacity sold-out ahead of risk production, confirming the design community’s appetite for leading-edge programmable ASIC tape-outs.

- April 2025: Andes Technology and Imagination Technologies booted Android 15 on a quad-core RISC-V platform featuring the AX45MP and NX27V vector unit, demonstrating OS readiness for open-ISA programmable devices.

- March 2025: MediaTek fabricated the first silicon-proven RF power-amplifier and PMU combo on N6RF+, validating mixed-signal integration for 5G radio ASICs.

- February 2025: SEMI projected 18 new fab ground-breaks during 2025 with 15 slated for 300 mm, adding mature-node headroom for programmable ASIC back-end volumes.

Global Programmable ASIC Market Report Scope

An application-specific integrated circuit (ASIC) is specially built for a specific application or purpose. Compared to a logic device or a standard logic integrated circuit, an ASIC provides better speed because it is specifically designed for a specific application. It is also made smaller, and it uses less electricity.

The Programmable Application Specific Integrated Circuit (ASIC) Market is segmented by end-user (consumer electronics, automotive, telecommunications) and geography (North America [United States, Canada], Europe [United Kingdom, Germany, France, Rest of Europe], Asia Pacific [China, Japan, India, Rest of Asia Pacific], rest of the World). The market sizes and forecasts are provided in terms of value (USD) for all the above segments.

| Structured ASIC |

| Full-Custom ASIC |

| Platform / Semi-Custom ASIC |

| Mixed-Signal ASIC |

| RF ASIC |

| Consumer Electronics |

| Telecommunications and Networking |

| Automotive and Transportation |

| Industrial and Robotics |

| Aerospace and Defense |

| Healthcare |

| Others |

| AI/ML Accelerators |

| IoT / Edge Devices |

| 5G / Networking Infrastructure |

| Data Center and Cloud |

| Automotive ADAS and Electrification |

| Medical Devices |

| Industrial Control and PLCs |

| above 28 nm |

| 16/14 nm |

| 10/7 nm |

| 5/4/3 nm |

| North America | United States | |

| Canada | ||

| South America | Brazil | |

| Argentina | ||

| Rest of South America | ||

| Europe | Germany | |

| France | ||

| United Kingdom | ||

| Italy | ||

| Russia | ||

| Rest of Europe | ||

| Asia Pacific | China | |

| Japan | ||

| India | ||

| South Korea | ||

| Australia | ||

| Rest of Asia Pacific | ||

| Middle East and Africa | Middle East | Saudi Arabia |

| UAE | ||

| Turkey | ||

| Rest of Middle East | ||

| Africa | South Africa | |

| Nigeria | ||

| Kenya | ||

| Rest of Africa | ||

| By ASIC Type | Structured ASIC | ||

| Full-Custom ASIC | |||

| Platform / Semi-Custom ASIC | |||

| Mixed-Signal ASIC | |||

| RF ASIC | |||

| By End-Use Industry | Consumer Electronics | ||

| Telecommunications and Networking | |||

| Automotive and Transportation | |||

| Industrial and Robotics | |||

| Aerospace and Defense | |||

| Healthcare | |||

| Others | |||

| By Application | AI/ML Accelerators | ||

| IoT / Edge Devices | |||

| 5G / Networking Infrastructure | |||

| Data Center and Cloud | |||

| Automotive ADAS and Electrification | |||

| Medical Devices | |||

| Industrial Control and PLCs | |||

| By Process Node | above 28 nm | ||

| 16/14 nm | |||

| 10/7 nm | |||

| 5/4/3 nm | |||

| By Geography | North America | United States | |

| Canada | |||

| South America | Brazil | ||

| Argentina | |||

| Rest of South America | |||

| Europe | Germany | ||

| France | |||

| United Kingdom | |||

| Italy | |||

| Russia | |||

| Rest of Europe | |||

| Asia Pacific | China | ||

| Japan | |||

| India | |||

| South Korea | |||

| Australia | |||

| Rest of Asia Pacific | |||

| Middle East and Africa | Middle East | Saudi Arabia | |

| UAE | |||

| Turkey | |||

| Rest of Middle East | |||

| Africa | South Africa | ||

| Nigeria | |||

| Kenya | |||

| Rest of Africa | |||

Key Questions Answered in the Report

How large is the programmable ASIC market in 2026?

The programmable ASIC market size reached USD 21.99 billion in 2026.

What is the expected growth rate for programmable ASIC revenue through 2031?

Aggregate revenue is projected to climb at a 8.79% CAGR to USD 33.51 billion by 2031.

Which ASIC device class currently holds the largest revenue share?

Structured ASICs led with 38.05% share of 2025 sales.

What application area is expanding the fastest?

AI/ML inference accelerators are forecast to grow at a 9.18% CAGR through 2031.

Which region is likely to register the highest growth over the forecast horizon?

Asia Pacific is set to expand at a 9.61% CAGR, propelled by large-scale capacity investments.

.webp)