SRAM And ROM Design IP Market Size and Share

SRAM And ROM Design IP Market Analysis by Mordor Intelligence

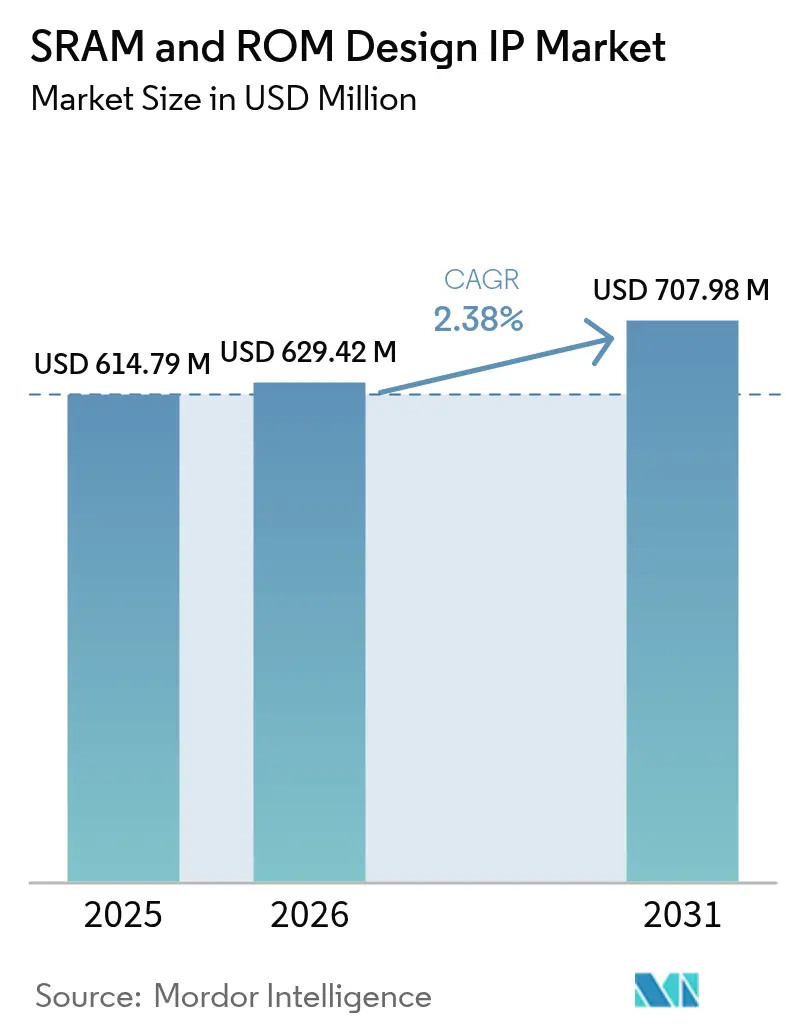

The SRAM and ROM Design IP market size was valued at USD 614.79 million in 2025 and estimated to grow from USD 629.42 million in 2026 to reach USD 707.98 million by 2031, at a CAGR of 2.38% during the forecast period (2026-2031). Continued demand for cache-dense AI accelerators, 5G edge nodes, and automotive functional-safety platforms underpins this measured expansion. Sub-14 nm processes capture disproportionate licensing fees as design houses seek bit-cell architectures that tame variability, leakage, and soft-error rates. Hard IP remains the preferred delivery format because it minimizes qualification risk and accelerates tape-out schedules, yet chiplet-ready memory tiles are now gaining momentum as heterogeneous packaging moves into volume production. Competitive intensity is rising as open-source compilers compress average selling prices, prompting established vendors to intensify their focus on verification suites and foundry partnerships. Regionally, the Asia Pacific dominates shipments due to its foundry scale and government subsidies, while North America sustains its innovation leadership through its fabless design ecosystem.

Key Report Takeaways

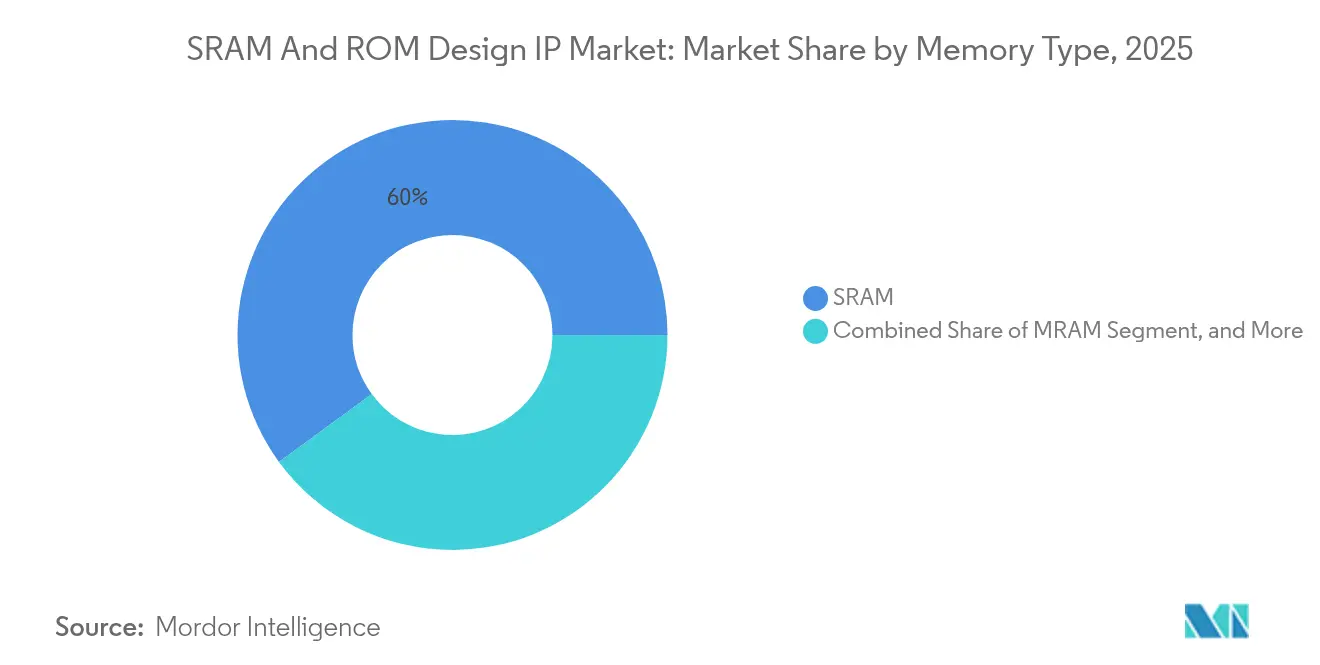

- By memory type, SRAM led with 60.05% of the SRAM and ROM Design IP market share in 2025, while embedded flash and other non-volatile options are projected to expand at a 3.72% CAGR through 2031.

- By application, consumer electronics accounted for 36.10% of the SRAM and ROM Design IP market size in 2025, whereas automotive and transportation are forecast to grow at a 4.9% CAGR during 2026-2031.

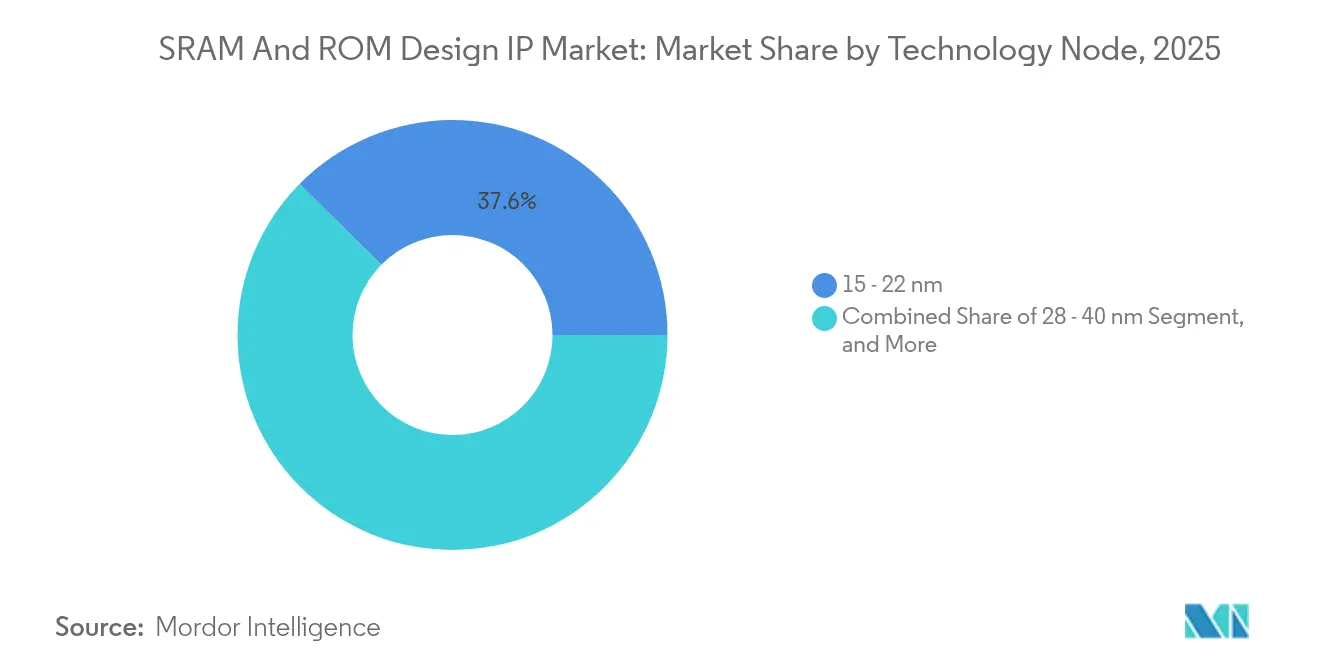

- By technology node, the 15–22 nm class held a 37.60% share of the SRAM and ROM Design IP market size in 2025, while sub-14 nm nodes are expected to advance at a 3.92% CAGR through 2031.

- By IP delivery type, hard IP captured a 47.35% share of the SRAM and ROM Design IP market in 2025; chiplet and 3D die-level IP is the fastest-rising format at a 4.22% CAGR through 2031.

- By geography, the Asia Pacific region dominated the SRAM and ROM Design IP market with 46.85% of the market revenue in 2025 and is projected to grow at a 3.82% CAGR through 2031.

Note: Market size and forecast figures in this report are generated using Mordor Intelligence’s proprietary estimation framework, updated with the latest available data and insights as of 2026.

Global SRAM And ROM Design IP Market Trends and Insights

Drivers Impact Analysis*

| Driver | (~) % Impact on CAGR Forecast | Geographic Relevance | Impact Timeline |

|---|---|---|---|

| AI-centric SoCs pushing large on-chip cache | +0.8% | North America; Asia Pacific | Medium term (2-4 years) |

| 5G and edge-computing rollout | +0.6% | Asia Pacific; North America | Short term (≤2 years) |

| Shift from eFlash to MRAM <28 nm | +0.4% | Advanced foundry regions | Long term (≥4 years) |

| Automotive Grade-1 functional-safety rules | +0.3% | Europe; North America | Medium term (2-4 years) |

| Chiplet architectures standardizing die I/O | +0.2% | North America; Asia Pacific | Long term (≥4 years) |

| Foundry turnkey memory compilers | +0.2% | Asia Pacific | Short term (≤2 years) |

| Source: Mordor Intelligence | |||

Proliferation of AI-centric SoCs demanding large on-chip cache

Inference accelerators now integrate as much as 40 MB of SRAM to store weights and feature maps, far eclipsing the 8-16 MB found in general-purpose processors.[1]Simon Segars, “Arm Announces New CPU and GPU Designs for AI Workloads,” arm.com Compute-in-memory variants place arithmetic operations directly inside the bit cell to reduce data movement energy, creating new compiler requirements. Sovereign-AI initiatives in multiple regions add volume by funding domestic chip programs that insist on locally verified memory IP. Three-dimensional stacking through-silicon vias further raises cache ceilings while preserving the footprint. Vendors capable of shipping multi-gigahertz, low-leakage SRAM macros with exhaustive timing corners are best positioned to capitalize on this upswing.

5G and edge-computing roll-outs accelerating low-power embedded SRAM adoption

Edge servers and IoT nodes require sub-1V memory blocks that retain data across a temperature range of –40 °C to 125 °C. Next-generation IP now posts leakage below one nanoampere per megabit by combining multi-threshold transistors with power-gating cells.[2]Samsung Foundry Team, “Samsung Foundry Announces 4 nm Process Technology for 5G Applications,” samsungsemiconductor.com Dynamic body-biasing allows designers to trade standby power for access speed on a minute-to-minute basis. In parallel, 5G baseband ASICs rely on dual-port SRAM that is finely tuned for burst packet buffering. These stringent power profiles raise the bar for characterization depth and corner validation, favoring suppliers with silicon-proven data across multiple foundries.

Transition from eFlash to MRAM below 28 nm unlocking new licensing revenue streams

Embedded flash struggles with high thermal budgets and gate-oxide scaling, making it uneconomical beyond 28 nm. Foundries have therefore integrated magnetic tunnel junction stacks that permit back-end-of-line insertion with minimal impact on logic. Spin-transfer torque MRAM endures >10¹⁵ writes, eliminating flash wear-leveling overhead in automotive elements. The lengthy 18-24 month qualification cycles erect barriers that smaller houses find hard to clear. IP vendors able to supply compiler flows, macro hardening, and in-system bias drivers gain an annuity-like revenue stream as each new node migrates to MRAM.

Automotive Grade-1 functional-safety rules boosting qualified memory IP demand

ISO 26262 ASIL-D flows require dual-redundant arrays, ECC, background self-tests, and single-event upset mitigation. Radiation-tolerant bit-cells and error-detection scrubbing raise area by 10-15%, yet OEMs accept the cost to meet over-the-air update and fail-operational mandates. Qualification spans 3-5 years and involves thousands of fault-injection scenarios. Once secured, sockets typically persist for a decade of vehicle production, giving incumbents a durable share.

Restraints Impact Analysis*

| Restraint | (~) % Impact on CAGR Forecast | Geographic Relevance | Impact Timeline |

|---|---|---|---|

| Open-source compilers eroding ASPs | –0.5% | Global | Short term (≤2 years) |

| ReRAM/FeRAM cannibalizing small ROM sockets | –0.3% | Consumer electronics | Medium term (2-4 years) |

| Export-control compliance hurdles for China tape-outs | –0.4% | China; global spillover | Short term (≤2 years) |

| Reliability headwinds for ≤7 nm SRAM bit-cells | –0.2% | Asia Pacific; North America | Long term (≥4 years) |

| Source: Mordor Intelligence | |||

Pricing pressure from open-source memory compilers eroding ASPs

Community projects tied to the RISC-V ecosystem now deliver free SRAM generators for mature nodes, undercutting commercial offerings in cost-sensitive wearables and toys.[3]RISC-V International, “RISC-V Memory Compiler Initiative Launches,” riscv.org Universities further seed libraries, giving fabless teams a quick path to first silicon. Vendors defend their margins by emphasizing the reduction of leakage, coverage of corners, and safety packages that open-source flows often lack. Nonetheless, entry-level revenue streams continue to compress.

Export-control compliance hurdles for Chinese tape-outs

In October 2022, U.S. rules mandated export licenses for advanced memory IP, enabling AI functions.[4]U.S. Department of Commerce, “Advanced Computing and Semiconductor Manufacturing Controls,” bis.doc.gov Approval cycles stretch deal timelines and impose documentation overhead. Some Western licensors have paused deliveries below 14 nm, prompting Chinese fabs to accelerate their in-house compiler efforts. Fragmentation reduces total addressable volume for international suppliers while raising compliance costs across the value chain.

*Our updated forecasts treat driver/restraint impacts as directional, not additive. The revised impact forecasts reflect baseline growth, mix effects, and variable interactions.

Segment Analysis

By Memory Type: SRAM dominance persists as emerging NVM gains momentum

SRAM retained 60.05% share of the SRAM and ROM Design IP market in 2025, a testament to its unmatched speed in cache and buffer roles. The segment climbs modestly in absolute dollars as AI accelerators and 5G switches request fatter on-die slices. In parallel, ROM families, including PROM, EPROM, and EEPROM, serve as boot code and calibration tables, but gradually shrink as system-on-chip consolidation removes discrete blocks. The SRAM and ROM Design IP market size associated with MRAM and other non-volatile newcomers remains modest, yet their position strengthens once eFlash reaches a capacity limit below 28 nm.

Licensing tied to embedded flash and alternative NVM grows at the fastest rate, with a 3.72% CAGR, because IoT microcontrollers and automotive ECUs require durable code storage. Multi-technology compilers that couple SRAM’s speed with MRAM’s persistence underpin hybrid arrays entering pilot production. Vendors versed in both volatility domains command a pricing premium, especially when they can map identical logical interfaces across processes, trimming firmware porting risk.

Note: Segment shares of all individual segments available upon report purchase

By Application: Consumer electronics leadership yields to automotive growth

Consumer devices held 36.10% of the SRAM and ROM Design IP market share in 2025, driven by smartphones, tablets, and consoles that demand ever-richer graphics and local AI capabilities. Design cycles remain brisk, but capacity gains plateau as vendors recycle board real estate for cameras and antennas. Telecommunications ASICs rely on dual-port SRAM tuned for <1 ns latency to maintain line-rate packet forwarding, a niche that rewards compiler flexibility.

Automotive and transportation IP bookings are projected to rise at a 4.9% CAGR to 2031, driven by the demand for advanced driver-assistance systems that require multi-gigabyte on-chip arrays paired with ASIL-D diagnostics. The SRAM and ROM Design IP market size exposed to Grade-1 functional safety, therefore, increases faster than any other vertical. Aerospace and defense requests remain small in volume, yet they yield high average selling prices because radiation-hardened libraries undergo rigorous qualification.

By Technology Node: Mature geometries dominate volume while advanced nodes set the pace

The 15–22 nm class accounted for 37.60% of revenue in 2025, as it combines performance with established yield learning. Low-risk consumer and automotive controllers sit comfortably here, and compiler IP amortizes across several foundry variants. Above 45 nm, trailing-edge libraries persist in long-tail industrial and military programs whose redesign costs outweigh power-area savings.

Sub-14 nm macros advance at 3.92% CAGR because data-center AI accelerators, flagship smartphones, and high-performance computing chips cannot meet density or power targets on larger nodes. Each geometry shrink multiplies bit-cell variation vectors, accentuating the value of vendors that supply exhaustive PVT models and reliability monitors. The SRAM and ROM Design IP market size for these bleeding-edge nodes commands premium royalties that more than offset narrower unit volumes.

Note: Segment shares of all individual segments available upon report purchase

By IP Delivery Type: Hard IP prevails while chiplet forms accelerate

Hard IP delivered 47.35% of the total 2025 billings. Customers appreciate its silicon-proven layouts, which shave weeks from sign-off and minimize die area. Compiler IP bridges flexibility and turnaround time yet concedes floor-plan efficiency, limiting uptake in cost-sensitive gadgets. Soft IP remains essential for users chasing exotic architectures or proprietary transistor options.

Chiplet and 3D die-level memory tiles present the liveliest sub-segment with a projected 4.22% CAGR. They let designers mix mature memory wafers with cutting-edge logic while meeting bandwidth goals through ultra-short interposer runs. Early adopters in data-center accelerators validate economic returns, encouraging wider field adoption.

Geography Analysis

The Asia Pacific held 46.85% of the SRAM and ROM Design IP market revenue in 2025 and is projected to grow at a 3.82% CAGR through 2031. Foundry clusters in Taiwan, South Korea, and mainland China lower tape-out costs, while national subsidy schemes bankroll indigenous compiler projects. Japan contributes safety-focused macros tailored for Tier-1 automotive suppliers and industrial robotics, reinforcing regional breadth.

North America commands the lion’s share of bleeding-edge design starts as Silicon Valley startups and hyperscale cloud vendors race to release proprietary AI silicon. The CHIPS Act funnels fresh capital into domestic fabs, catalyzing on-shore IP verification labs and opening grant channels for smaller houses. Automotive Tier-1s in Detroit partner with aerospace primes to request radiation-hard, ASIL-D compliant macros, tapping into high-margin niches.

Europe focuses on automotive and industrial automation, leveraging Germany’s OEM ecosystem and stringent enforcement of ISO 26262. Nordic countries supply ultra-low-power memories for harsh environments, while France and Italy explore sovereign computing initiatives that favor local IP. Overall, continental demand tilts toward reliability and functional safety credentials over raw density.

Competitive Landscape

The field shows moderate consolidation. A handful of suppliers cover every mainstream node from 180 nm down to 3 nm and offer bundled verification IP, scripting flows, and silicon statistics. These leaders exploit scale to pre-tape‐out macros on new processes in partnership with foundries, enabling “Day-1” availability that emerging rivals struggle to match. Pricing disciplines erode as open-source projects commoditize mature nodes, so incumbents lean into automotive and AI verticals where safety and power budgets amplify differentiation.

Strategic moves underscore this path. Arm acquired Intrinsix for USD 85 million in September 2024 to deepen its AI-tuned SRAM expertise. Synopsys added Verific Design Automation for USD 120 million the previous month, knitting formal verification engines into its compiler chain. Foundries, meanwhile, roll out in-house macro generators that pull IP vendors closer via joint PDK enablement.

White-space opportunities emerge in compute-in-memory SRAM for edge inference, UCIe-compliant chiplets for data center accelerators, and MRAM arrays for over-the-air automotive updates. Suppliers able to certify both ASIL-D flows and export-control coverage lock in long-cycle demand. Market share, nevertheless, remains fluid as new memory physics, such as ReRAM, threaten to displace entrenched bit cells.

SRAM And ROM Design IP Industry Leaders

-

Arm Ltd.

-

Synopsys Inc.

-

Cadence Design Systems Inc.

-

Siemens EDA (Mentor Graphics Corporation)

-

eMemory Technology Inc.

- *Disclaimer: Major Players sorted in no particular order

Recent Industry Developments

- September 2025: Arm Holdings completed one year of its acquisition of Intrinsix for USD 85 million, adding low-power SRAM and automotive-grade macro talent.

- August 2025: Synopsys completed its one year of USD 120 million purchase of Verific Design Automation to accelerate memory verification throughput.

- August 2024: Dolphin Design shipped an ultra-low-power SRAM compiler with sub-nanampere leakage.

- July 2024: TSMC released a 3nm memory compiler suite featuring exhaustive variability modeling.

- June 2024: Samsung Foundry partnered with Cadence on ISO 26262 ASIL-D qualified memory IP for advanced driver-assistance systems.

Global SRAM And ROM Design IP Market Report Scope

The study analyzes the overall design of IP, in terms of trends, list of IP offered, overall market scenario, and key IP vendors, specifically for SRAM and ROM technologies. Moreover, the study also analyzes the overall market scenario of MRAM technologies, in terms of accrued revenues, technological trends, latest developments, applications (standalone vs. embedded), and roadmap, in terms of technological nodes and key vendors offering MRAM products.

| SRAM |

| ROM (PROM / EPROM / EEPROM) |

| MRAM |

| Embedded Flash / Other NVM |

| Consumer Electronics |

| Telecommunications and Networking |

| Automotive and Transportation |

| Industrial and IoT |

| Aerospace and Defense |

| Other Applications |

| ≤14 nm |

| 15 – 22 nm |

| 28 – 40 nm |

| ≥45 nm |

| Hard IP |

| Soft IP |

| Parameterised Compiler IP |

| Chiplet / 3D Die-level IP |

| North America | United States |

| Canada | |

| Mexico | |

| South America | Brazil |

| Argentina | |

| Rest of South America | |

| Europe | Germany |

| United Kingdom | |

| France | |

| Italy | |

| Spain | |

| Rest of Europe | |

| Asia Pacific | China |

| Japan | |

| India | |

| South Korea | |

| South-East Asia | |

| Rest of Asia Pacific | |

| Middle East | Saudi Arabia |

| United Arab Emirates | |

| Turkey | |

| Rest of Middle East | |

| Africa | South Africa |

| Nigeria | |

| Rest of Africa |

| By Memory Type | SRAM | |

| ROM (PROM / EPROM / EEPROM) | ||

| MRAM | ||

| Embedded Flash / Other NVM | ||

| By Application | Consumer Electronics | |

| Telecommunications and Networking | ||

| Automotive and Transportation | ||

| Industrial and IoT | ||

| Aerospace and Defense | ||

| Other Applications | ||

| By Technology Node | ≤14 nm | |

| 15 – 22 nm | ||

| 28 – 40 nm | ||

| ≥45 nm | ||

| By IP Delivery Type | Hard IP | |

| Soft IP | ||

| Parameterised Compiler IP | ||

| Chiplet / 3D Die-level IP | ||

| By Geography | North America | United States |

| Canada | ||

| Mexico | ||

| South America | Brazil | |

| Argentina | ||

| Rest of South America | ||

| Europe | Germany | |

| United Kingdom | ||

| France | ||

| Italy | ||

| Spain | ||

| Rest of Europe | ||

| Asia Pacific | China | |

| Japan | ||

| India | ||

| South Korea | ||

| South-East Asia | ||

| Rest of Asia Pacific | ||

| Middle East | Saudi Arabia | |

| United Arab Emirates | ||

| Turkey | ||

| Rest of Middle East | ||

| Africa | South Africa | |

| Nigeria | ||

| Rest of Africa | ||

Key Questions Answered in the Report

How big is the SRAM and ROM Design IP market today?

The SRAM and ROM Design IP market size stands at USD 629.42 million in 2026 and is on track to reach USD 707.98 million by 2031.

Which segment is expanding the fastest?

Embedded flash and other non-volatile memory IP post the highest growth at a 3.72% CAGR through 2031 thanks to IoT and automotive demand.

Why is Asia Pacific so dominant?

Foundry scale, government subsidies, and a concentration of design houses give Asia Pacific 46.85% share and sustained 3.82% CAGR growth.

How are chiplet trends reshaping memory IP?

Chiplet-ready memory tiles paired with UCIe links are growing at a 4.22% CAGR because they let designers mix node choices while boosting bandwidth.

What keeps pricing under pressure?

Open-source SRAM compilers and university-backed libraries are eroding entry-level ASPs, forcing commercial vendors to emphasize power, safety, and verification depth.

Which regulatory issue impacts China-based designs?

U.S. export-control rules imposed in 2022 require licenses for advanced SRAM and emerging memory IP, lengthening deal cycles and motivating domestic alternatives.