Taille et part du marché de la mémoire vive dynamique (DRAM)

Analyse du marché de la mémoire vive dynamique (DRAM) par Mordor Intelligence

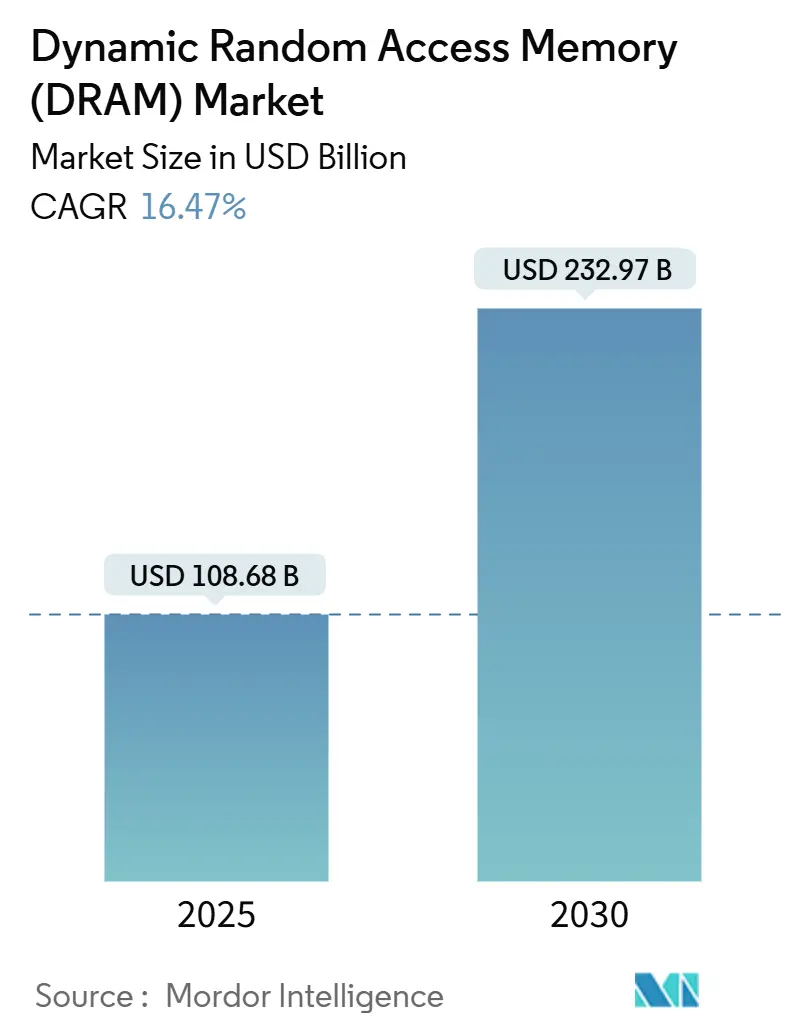

La taille du marché de la mémoire vive dynamique est évaluée à 108,68 milliards USD en 2025 et devrait atteindre 232,97 milliards USD d'ici 2030, se traduisant par un TCAC robuste de 16,47 %. L'adoption accélérée de serveurs centrés sur l'IA, la montée en puissance rapide de la mémoire à bande passante élevée, et des exigences de qualification automobile plus strictes ont modifié les critères d'achat de la capacité seule vers un focus équilibré sur la bande passante, la puissance et les performances thermiques. Les opérateurs cloud hyperscale ont commencé à renouveler les racks avec des modules DDR5 et HBM3E durant 2024, tandis que les OEM de smartphones en Asie ont migré une grande partie de leurs portfolios haut de gamme et milieu de gamme vers LPDDR5X, maintenant collectivement l'utilisation des fonderies au-dessus de 95 % jusqu'à mi-2025. Le contenu mémoire par véhicule électrique a augmenté rapidement alors que les architectures zonales remplaçaient les réseaux ECU traditionnels, poussant la demande de DRAM automobile vers le territoire multi-gigaoctet. Simultanément, les conflits d'allocation d'approvisionnement entre les lignes lucratives HBM3E et les DDR4 héritées ont déclenché des hausses de prix qui ont remodelé les compromis coût-performance pour les PC, smartphones et cartes IoT industrielles.

Points clés du rapport

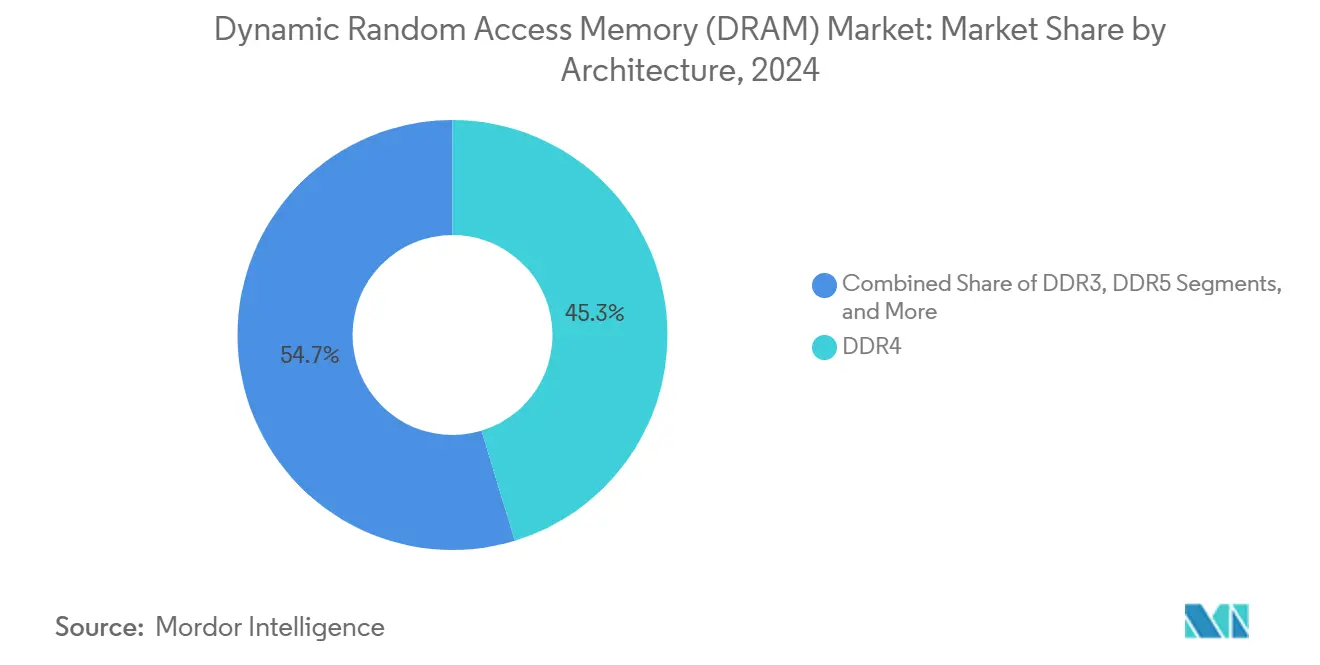

- Par architecture, la DDR4 détenait une part de marché de la mémoire vive dynamique de 45,3 % en 2024, tandis que la DDR5 devrait croître à un TCAC de 30,2 % jusqu'en 2030.

- Par nœud technologique, la catégorie 19 nm-10 nm a capturé 42,3 % de la taille du marché de la mémoire vive dynamique en 2024 et progresse à un TCAC de 25,2 % jusqu'en 2030.

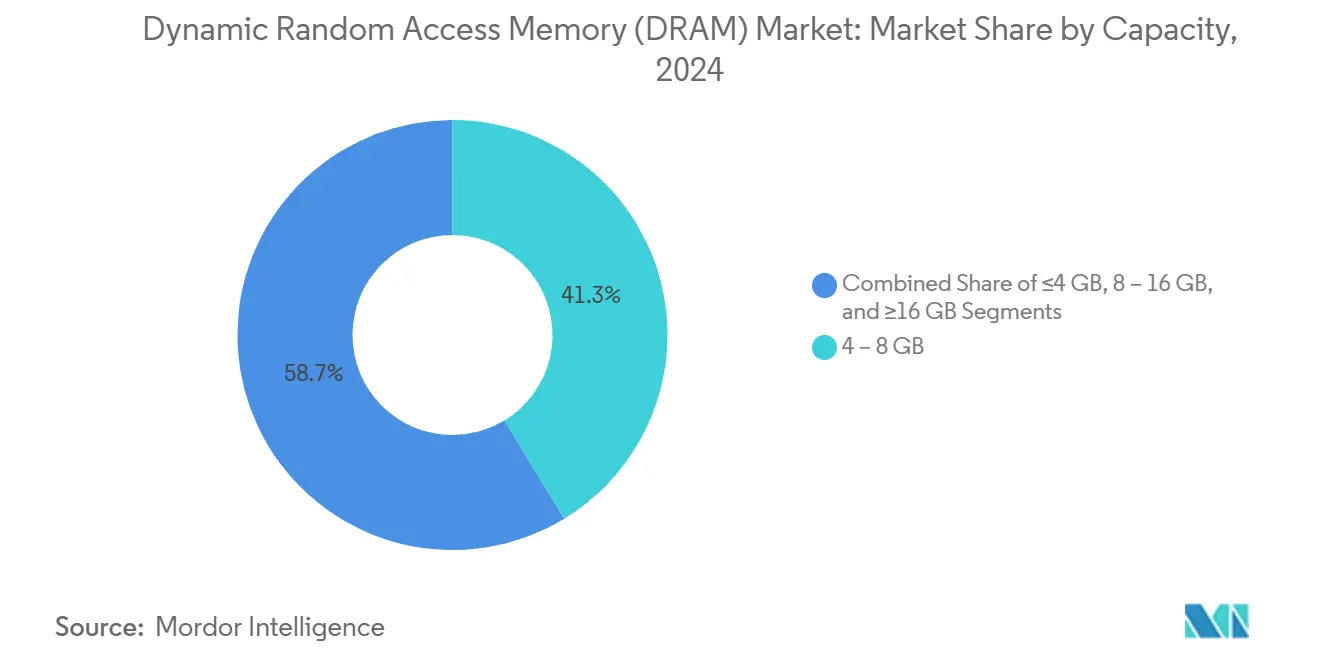

- Par capacité, les modules 4-8 Go représentaient 41,3 % de la taille du marché de la mémoire vive dynamique en 2024, tandis que les configurations ≥16 Go devraient croître à 28,2 % entre 2025 et 2030.

- Par application finale, les smartphones et tablettes menaient avec 35,2 % de part de revenus en 2024 ; l'électronique automobile devrait grimper à un TCAC de 31,2 % jusqu'en 2030.

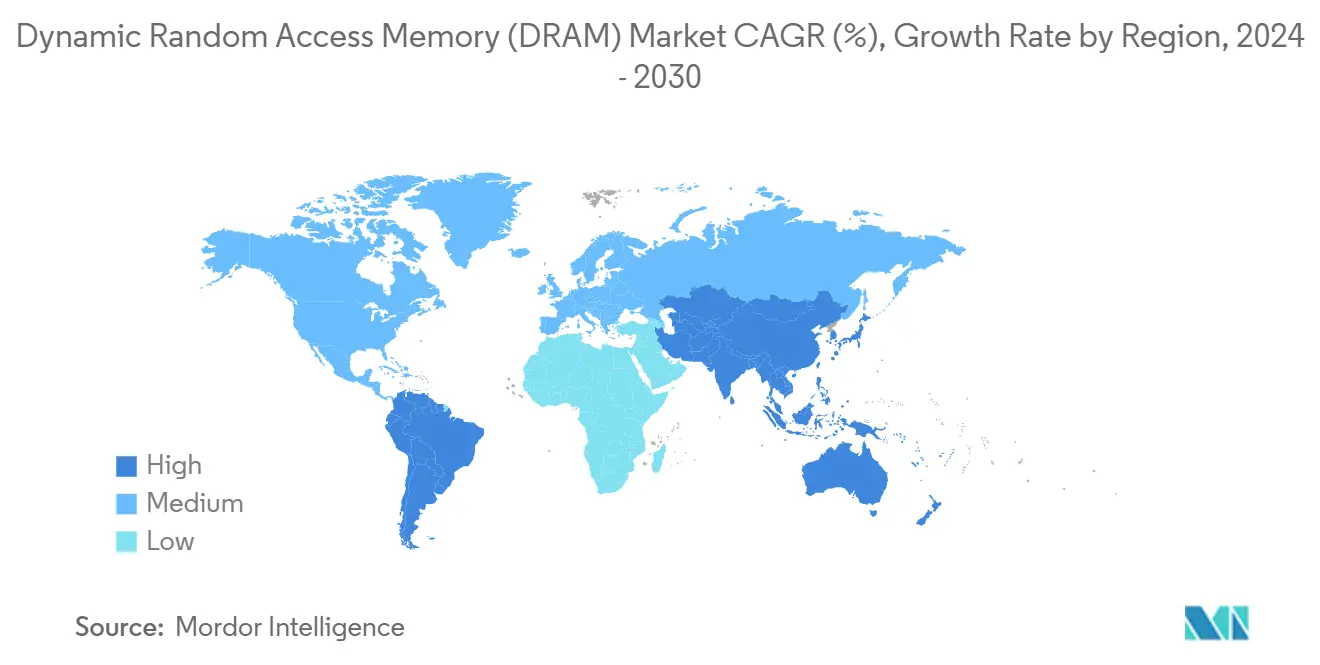

- Par géographie, l'Asie-Pacifique représentait 31,2 % des ventes de 2024, tandis que l'Amérique du Sud devrait afficher un TCAC de 22,2 % sur la période de prévision.

Tendances et insights du marché mondial de la mémoire vive dynamique (DRAM)

Analyse d'impact des moteurs

| Moteur | (~) % Impact sur les prévisions TCAC | Pertinence géographique | Calendrier d'impact |

|---|---|---|---|

| Empreinte de contenu croissante des charges de travail IA et IA générative dans les centres de données hyperscale | +4.2% | Mondiale, avec concentration en Amérique du Nord et APAC | Moyen terme (2-4 ans) |

| Adoption montante de LPDDR dans les smartphones 5G haut de gamme et milieu de gamme à travers l'APAC | +3.8% | Noyau APAC, débordement vers les marchés mondiaux | Court terme (≤ 2 ans) |

| Contrôleurs zonaux/de domaine automobiles migrant du NOR vers la DRAM haute température | +2.9% | Mondiale, adoption précoce en Europe et Amérique du Nord | Long terme (≥ 4 ans) |

| Cartes Edge-AI et IoT industriel nécessitant des modules DRAM à température étendue | +2.1% | Mondiale, avec hubs de fabrication en APAC | Moyen terme (2-4 ans) |

| Transition des fournisseurs de services cloud vers les pools mémoire attachés CXL | +1.8% | Amérique du Nord et UE, expansion vers APAC | Long terme (≥ 4 ans) |

| Source: Mordor Intelligence | |||

Empreinte de contenu croissante des charges de travail IA et IA générative dans les centres de données hyperscale

Les plateformes GP-AI Blackwell 2025 de NVIDIA ont établi des références de bande passante qui ont éclipsé les architectures DDR conventionnelles, élevant la mémoire serveur moyenne de 256 Go en 2024 vers des déploiements multi-téraoctets d'ici mi-2025. Avec chaque pile HBM3E délivrant plus de 1 To/s, les opérateurs cloud ont réarchitecturé les racks autour de topologies centrées sur la mémoire. Samsung a livré de la DRAM CXL 2.0 prête pour la production qui a permis à Azure et autres fournisseurs de mettre en commun la mémoire entre les hôtes, améliorant l'utilisation tout en différant les dépenses d'investissement sur des nœuds de calcul supplémentaires.[1]Samsung Electronics, "CXL DRAM Enables New Data-Center Memory Architecture," semiconductor.samsung.com Les fournisseurs ont par conséquent déplacé les démarrages de wafers de DDR4 vers HBM, déclenchant une tension dans les grades hérités mais accélérant la croissance des profits dans le segment premium.

Adoption montante de LPDDR dans les smartphones 5G haut de gamme et milieu de gamme à travers l'APAC

Les échantillons LPDDR5X 1γ de Micron fonctionnant à 9 200 MT/s ont atteint les fabricants de smartphones au T1 2025, réduisant la consommation de 20 % et élevant les configurations de base dans les modèles chinois et indiens de 8 Go à 12 Go de RAM. Xiaomi, OPPO et les marques émergentes telles que Transsion sont bloqués dans des contrats à terme qui consomment une part croissante de la capacité des fonderies APAC, forçant les fournisseurs à jongler entre les engagements mobiles et de centres de données. Le changement a donné à LPDDR une courbe de croissance plus raide que toute autre mémoire mobile depuis que LPDDR4 est entrée en production de masse en 2015.

Contrôleurs zonaux et de domaine automobiles migrant du NOR vers la DRAM haute température

Les véhicules électriques construits sur des plateformes définies par logiciel nécessitaient des pools mémoire qui éclipsaient les empreintes d'infodivertissement héritées. Plusieurs OEM européens ont validé 16 Go de DRAM qualifiée AEC-Q100 en 2024 et ont par la suite élevé les cibles de plateforme vers 90 Go par véhicule dans les calendriers 2025. Samsung et SK Hynix ont investi dans des ajustements de processus à large température pour sécuriser la conformité ISO 26262, créant des barrières pour les nouveaux entrants et améliorant la discipline de prix dans le coin de grade automobile du marché de la mémoire vive dynamique.

Cartes Edge-AI et IoT industriel nécessitant des modules DRAM à température étendue

Les fournisseurs d'automatisation d'usine ont mis à niveau les contrôleurs logiques programmables et les systèmes de vision avec DDR4-3200 à des classifications de -40 °C à 85 °C, permettant l'inférence IA locale qui réduit la latence aller-retour cloud. ATP et Innodisk ont capitalisé sur la niche en offrant des DIMM revêtus conformes avec gestion de rafraîchissement agressive, que les OEM industriels ont acceptés à des primes de 30 % par rapport aux pièces de grade commercial. L'amélioration de marge résultante a incité les majeurs DRAM à licencier les processus de durcissement, élargissant l'approvisionnement jusqu'en 2026.

Analyse d'impact des freins

| Frein | (~) % Impact sur les prévisions TCAC | Pertinence géographique | Calendrier d'impact |

|---|---|---|---|

| Cyclicité offre-demande entraînant une volatilité ASP extrême | -2.8% | Mondiale, avec effets amplifiés sur les marchés au comptant | Court terme (≤ 2 ans) |

| Défis d'érosion de rendement sous les nœuds EUV 10 nm | -1.9% | Mondiale, concentrée dans les fonderies avancées | Moyen terme (2-4 ans) |

| Contrôles d'exportation géopolitiques sur la Chine limitant les expéditions DRAM serveur haute densité | -1.4% | Axé sur la Chine, avec impacts chaîne d'approvisionnement mondiale | Long terme (≥ 4 ans) |

| Source: Mordor Intelligence | |||

Cyclicité offre-demande entraînant une volatilité ASP extrême

Les tirages HBM à marge élevée ont persuadé les fonderies de reporter les runs DDR4 début 2025, enflammant un bond de prix au comptant de 50 % pour les modules mainstream en mai. Les contrats DDR5 ont aussi grimpé de 15-20 %, incitant les OEM à re-concevoir les nomenclatures produit ou sur-commander pour se couvrir contre d'autres pics. La boucle de rétroaction a amplifié la volatilité et réduit la visibilité pour la planification de production, retranchant deux points et plus du TCAC prévisionnel du marché de la mémoire vive dynamique.

Défis d'érosion de rendement sous les nœuds EUV 10 nm

Les premières runs des nœuds 1β et 1γ ont souffert de défectuosité de masque et rugosité stochastique de bord de ligne, traînant les rendements dans la gamme basse 70 % dans certaines fonderies. Samsung et Micron ont alloué des budgets R&D considérables aux améliorations de résistance et nouvelle technologie de pellicule, pourtant les courbes d'apprentissage ont allongé les calendriers de montée. Les rendements serrés ont réduit la sortie de puces durant une fenêtre de demande de pointe, ajoutant une pression coût qui a cascadé à travers les segments consommateur et entreprise.[2]TrendForce, "Samsung Targets 1c DRAM Yield Improvement by Mid-2025," trendforce.com

Analyse par segment

Par architecture : l'accélération DDR5 remodèle les hiérarchies mémoire

La DDR5 représentait une part minimale du marché de la mémoire vive dynamique en 2024, mais portait le TCAC prévisionnel le plus rapide de 30,2 %, soutenu par la mise à jour JESD79-5C de JEDEC qui a élevé les plafonds de performance à 8 800 Mbps. Ce bond technique a permis aux constructeurs cloud de niveau 1 de faire tourner des configurations mixtes DDR5-HBM3E qui ont doublé la bande passante effective par socket. La DDR5 1γ de Micron a atteint 9 200 MT/s en février 2025, un jalon qui a poussé les OEM serveur à avancer les rafraîchissements de plateforme. Pendant ce temps, la DDR4 a conservé une part de marché de la mémoire vive dynamique de 45,3 % en 2024 car les budgets IT d'entreprise favorisaient encore les configurations optimisées en coût. Les empreintes DDR3 et DDR2 héritées ont continué à rétrécir alors que les design-ins industriels et automobiles migraient vers les standards plus récents.

Les fournisseurs ont fait face à un acte d'équilibre : chaque wafer réassigné à DDR5 signifiait moins de puces DDR4 pour les PC, entraînant des pics de coût qui ont coulé en aval vers les assembleurs de portables en Chine. Les détenteurs d'inventaires de longue traîne ont exploité le trading d'arbitrage, déchargeant la DDR4 stockée à des primes inédites depuis 2017. Le nouveau facteur de forme CAMM2 de JEDEC a supprimé les contraintes de hauteur des SO-DIMM, permettant aux ordinateurs portables et serveurs edge d'adopter des piles simple face plus denses. Ces gains d'emballage ont alimenté l'élan du marché de la mémoire vive dynamique vers des normes de bande passante plus élevées à travers les appareils consommateur et entreprise.

Note: Parts de segments de tous les segments individuels disponibles à l'achat du rapport

Par nœud technologique : les processus avancés stimulent la différenciation concurrentielle

La tranche 19 nm-10 nm détenait 42,3 % de la taille du marché de la mémoire vive dynamique en 2024 et devrait croître de 25,2 % jusqu'en 2030 alors que les fournisseurs pressent des puces supplémentaires par wafer sans plonger dans le gouffre de risque de rendement du sub-10 nm. La production 1γ activée EUV a commencé à expédier des unités de revenus au T1 2025, mais les rendements de ligne sont restés au moins huit points sous les lignes 1z matures. Par conséquent, de nombreux fabricants d'appareils ont renouvelé les accords pour les grades 1z et 1y pour tamponner le risque coût, donnant aux processus mi-nœud un boost de volume.

SK Hynix a établi une feuille de route DRAM à porte verticale qui promet l'empilement au niveau wafer au-delà de 2027, signalant le pivot à long terme du scaling latéral vers les architectures 3D. Chaque rétrécissement planaire successif livre moins de 12 % de réduction de coût après factorisation des jeux de masques, matériaux et dépréciation, poussant les fonderies à chercher des reconceptions structurelles plutôt que le seul rétrécissement géométrique. La sensibilité coût dans l'électronique mobile et grand public a maintenu les nœuds ≥20 nm vivants pour les SKU axés prix, assurant un mix de production stratifié qui a diversifié la sortie des fonderies et soutenu la résilience globale des revenus.

Par capacité : les configurations haute densité accélèrent à travers les applications

Les modules ≥16 Go devraient afficher un TCAC de 28,2 % et passer du statut de niche en 2024 à l'adoption mainstream dans l'automobile et les smartphones premium d'ici 2030. Le contenu par véhicule électrique a augmenté de gigaoctets à un chiffre début 2024 à environ 40 Go dans les builds pilotes fin 2025, et les discussions de feuille de route parmi les OEM européens référencent des cibles de 4 To pour l'autonomie Niveau-4 d'ici fin de décennie. Les leaders smartphones ont adopté des niveaux 16 Go pour les lancements flagship centrés IA en H1 2025, élargissant le parapluie de prix pour les appareils milieu de gamme 12 Go. La catégorie 4-8 Go, bien qu'encore 41,3 % de la taille du marché de la mémoire vive dynamique en 2024, a commencé à céder des parts alors que les téléphones d'entrée de gamme traversaient la ligne de base 6 Go.

Les fournisseurs ont bénéficié d'ASP plus riches sur les puces haute densité mais ont fait face aux contraintes de démarrages wafer, spécialement en équilibrant les engagements HBM3E. L'apprentissage de rendement sur les nœuds 1γ et futurs 1δ dictera si les mix de capacité peuvent basculer davantage vers le haut sans déclencher de chocs de prix indus. Les distributeurs de canal à Shenzhen ont rapporté un inventaire plus serré de puces 8 Go durant le T2 2025 alors que les fonderies priorisaient les correspondances de puces 16 Go pour sécuriser les commandes de centres de données, exemplifiant la compétition entre les vecteurs de demande consommateur et entreprise.

Par application finale : l'électronique automobile émerge comme leader de croissance

L'électronique automobile devrait grimper à un TCAC de 31,2 %, éclipsant les tablettes et PC comme le vertical du marché de la mémoire vive dynamique à mouvement le plus rapide. Les architectures de calcul zonal ont mandaté de la DRAM haute température, haute fiabilité qui opère sur -40 °C à 125 °C, et les victoires de design sur les plateformes année-modèle 2026 ont verrouillé des engagements d'achat s'étendant au-delà de 2029. Les pools mémoire ont approché 90 Go dans les prototypes EV premium durant 2025, équipant les véhicules pour les mises à jour over-the-air continues et l'assistance conducteur basée IA. Les expéditions smartphones et tablettes ont encore livré une part de revenus de 35,2 % en 2024, mais la saturation dans les régions matures a tempéré leur trajectoire de croissance.

La demande datacenter est restée robuste, conduite par les clusters d'inférence et d'entraînement IA dont les cycles d'expansion se mesurent maintenant en trimestres plutôt qu'en années. Les rafraîchissements graphiques et consoles de jeu programmés pour fin 2026 fourniront un uplift cyclique pour les variantes GDDR et DDR6. L'IoT industriel et les passerelles edge ont pris des parts incrémentales en adoptant des modules 8-16 Go durcis température, bien que leur nature fragmentée ait dilué le pouvoir de négociation de tout OEM unique. Le paysage d'applications hétérogène renforce les complexités d'allocation d'approvisionnement, contraignant les vendeurs à jongler entre différentes certifications qualité, facteurs de forme et cycles de vie en parallèle.

Analyse géographique

L'Asie-Pacifique a conservé une position de revenus de 31,2 % en 2024 sur la force des fonderies regroupées à travers la Corée du Sud, Taïwan et la Chine continentale. Les fournisseurs sud-coréens ont promis 120 000 milliards KRW (84 milliards USD) pour les expansions de capacité jusqu'en 2028, un chiffre destiné à sauvegarder le leadership dans la production HBM et DRAM traditionnelle.[3]SK Hynix, "SEDEX 2024: Showcasing AI Memory Leadership," news.skhynix.com Les maisons d'assemblage sous contrat de Taïwan ont, entre-temps, élargi les lignes d'emballage avancé pour servir la demande HBM4 montante, tirant parti du savoir-faire front-end des nœuds logiques pour introduire des innovations Through-Silicon-Via qui réduisent la résistance thermique.

L'Amérique du Nord a formé le plus grand marché de consommation alors que les constructeurs hyperscale accéléraient les rafraîchissements de racks et les constructeurs automobiles aux États-Unis intégraient les contrôleurs zonaux. Micron a sécurisé 6,1 milliards USD de financement CHIPS Act pour construire une nouvelle mégafonderie, un mouvement visant à dé-risquer l'exposition géopolitique et raccourcir les délais pour les clients domestiques. L'Europe a maintenu un focus technologique sur les applications automobiles et industrielles, avec les OEM allemands insistant sur des garanties de température étendue et longévité qui rapportaient des prix premium.

L'Amérique du Sud devrait croître à un TCAC de 22,2 % alors que le Brésil, l'Argentine et le Mexique nourrissent des écosystèmes d'assemblage électronique pour localiser l'approvisionnement. Les incitations politiques ont réduit les tarifs d'importation sur les composants mémoire assemblés domestiquement, créant des changements modestes mais significatifs dans les stratégies d'approvisionnement. Le Moyen-Orient et l'Afrique ont affiché une croissance à un chiffre moyen ancrée par les expansions de centres de données dans les États du Conseil de coopération du Golfe et la pénétration smartphone croissante au Nigeria et Kenya, pourtant l'instabilité politique a continué à tempérer l'adoption plus large. Combinés, ces narratifs régionaux soulignent comment le marché de la mémoire vive dynamique diversifie les flux de revenus même alors que la fabrication reste concentrée en Asie de l'Est.

Paysage concurrentiel

Le marché de la mémoire vive dynamique fonctionnait comme un oligopole en 2025, avec Samsung, SK Hynix et Micron détenant conjointement environ 95 % de la capacité wafer. SK Hynix a pris de l'avance à 36 % de part au T1 2025 après avoir été le premier à produire en volume des piles HBM3E de 1,15 To/s pour les programmes d'accélérateurs IA de pointe. Samsung a conservé le leadership dans les lignes de grade automobile et sécurisé un accord d'approvisionnement de 3 milliards USD avec AMD pour les futurs nœuds HBM3E. Micron a comblé l'écart technologique en expédiant DDR5 et LPDDR5X 1γ six mois avant sa feuille de route originale, restaurant l'équilibre concurrentiel dans les catégories DIMM mainstream.

La différenciation technologique tournait autour de l'adoption EUV, chaque couche de masque retirée se traduisant par des économies de coût de puce appréciables. Pourtant l'intensité capital abrupte a créé des barrières pour les joueurs de second rang tels que Nanya et Winbond, qui ont choisi de se spécialiser dans des segments industriels ou basse puissance de niche plutôt que de chasser les nœuds de pointe. Les firmes chinoises CXMT et JHICC ont élargi la production DDR5 utilisant des processus 1x matures, approvisionnant les assembleurs smartphones domestiques qui cherchaient à atténuer les restrictions d'exportation américaines.

Des alliances écosystème ont aussi émergé autour des standards d'interconnexion comme CXL. Marvell s'est associé avec multiples fournisseurs DRAM pour déployer des contrôleurs d'expansion mémoire qui élèvent les taux d'attachement pour DDR4 et DDR5 en mettant en commun les ressources à travers les lames serveur. La spécification HBM4 de JEDEC, publiée en avril 2025, a déclenché de frais accords de développement conjoint entre fabricants d'appareils et fonderies pour s'aligner sur le pas TSV, budgets thermiques et fiabilité d'emballage.[4]JEDEC, "JEDEC Publishes HBM4 Standard," jedec.org Dans ce contexte, les startups explorant MRAM, ReRAM et 3D X-AI visaient des déchargements de charges de travail de niche, bien qu'aucune n'ait encore démontré la parité coût avec la DRAM commodity d'ici mi-2025.

Leaders de l'industrie de la mémoire vive dynamique (DRAM)

-

Samsung Electronics Co. Ltd.

-

Micron Technology Inc.

-

SK Hynix Inc.

-

Nanya Technology Corporation

-

Winbond Electronics Corporation

- *Avis de non-responsabilité : les principaux acteurs sont triés sans ordre particulier

Développements récents de l'industrie

- Avril 2025 : JEDEC a publié le standard HBM4 (JESD270-4), doublant le nombre de canaux à 32 et élevant la bande passante de pointe à 2 To/s.

- Mars 2025 : SMART Modular a introduit un module mémoire CXL non volatile au facteur de forme EDSFF pour serveurs intensifs en données.

- Mars 2025 : KIOXIA a dévoilé un SSD NVMe de 122,88 To basé sur FLASH BiCS huitième génération, visant les jeux de données IA.

- Février 2025 : Micron Technology a annoncé l'expédition en volume de DDR5 1γ fonctionnant à 9 200 MT/s avec 20 % de puissance en moins, marquant la première DRAM sixième génération basée EUV sur le marché.

Portée du rapport global du marché de la mémoire vive dynamique (DRAM)

La mémoire vive dynamique, appelée DRAM, est utilisée dans divers appareils informatiques et électroniques comme les PC, smartphones, lecteurs de musique, ordinateurs portables, netbooks et tablettes. La portée de l'étude se concentre sur l'analyse de marché des semi-conducteurs DRAM vendus à travers le globe, et le dimensionnement de marché englobe les revenus générés par la DRAM vendue par divers acteurs du marché aux industries utilisatrices finales. L'étude suit aussi les paramètres de marché clés, les influenceurs de croissance sous-jacents et les principaux vendeurs opérant dans l'industrie, qui soutiendront les estimations de marché et taux de croissance durant la période de prévision. L'étude analyse davantage l'impact global du COVID-19 sur l'écosystème.

Le marché DRAM est segmenté par architecture (DDR3, DDR4, DDR5 et DDR2), applications (smartphones/tablettes, PC/ordinateurs portables, centres de données, graphiques, produits de consommation et automobile), et géographie (États-Unis, Europe, Corée, Chine, Taïwan, reste de l'Asie-Pacifique et reste du monde). Le rapport offre des prévisions de marché et tailles en valeur (USD) pour tous les segments ci-dessus.

| DDR2 et antérieure |

| DDR3 |

| DDR4 |

| DDR5 |

| LPDDR |

| GDDR |

| ≥20 nm |

| 19 nm - 10 nm |

| <10 nm (EUV) |

| ≤4 Go |

| 4 - 8 Go |

| 8 - 16 Go |

| ≥16 Go |

| Smartphones et tablettes |

| PC et ordinateurs portables |

| Serveurs et centres de données hyperscale |

| Graphiques et consoles de jeu |

| Électronique automobile |

| Électronique grand public (décodeurs, TV intelligente, VR/AR) |

| Appareils industriels et IoT |

| Autres |

| Amérique du Nord | États-Unis | |

| Canada | ||

| Mexique | ||

| Europe | Allemagne | |

| France | ||

| Royaume-Uni | ||

| Nordiques | ||

| Reste de l'Europe | ||

| Asie-Pacifique | Chine | |

| Taïwan | ||

| Corée du Sud | ||

| Japon | ||

| Inde | ||

| Reste de l'Asie-Pacifique | ||

| Amérique du Sud | Brésil | |

| Chili | ||

| Argentine | ||

| Reste de l'Amérique du Sud | ||

| Moyen-Orient et Afrique | Moyen-Orient | Arabie Saoudite |

| Émirats Arabes Unis | ||

| Turquie | ||

| Reste du Moyen-Orient | ||

| Afrique | Afrique du Sud | |

| Reste de l'Afrique | ||

| Par architecture | DDR2 et antérieure | ||

| DDR3 | |||

| DDR4 | |||

| DDR5 | |||

| LPDDR | |||

| GDDR | |||

| Par nœud technologique | ≥20 nm | ||

| 19 nm - 10 nm | |||

| <10 nm (EUV) | |||

| Par capacité | ≤4 Go | ||

| 4 - 8 Go | |||

| 8 - 16 Go | |||

| ≥16 Go | |||

| Par application finale | Smartphones et tablettes | ||

| PC et ordinateurs portables | |||

| Serveurs et centres de données hyperscale | |||

| Graphiques et consoles de jeu | |||

| Électronique automobile | |||

| Électronique grand public (décodeurs, TV intelligente, VR/AR) | |||

| Appareils industriels et IoT | |||

| Autres | |||

| Par géographie | Amérique du Nord | États-Unis | |

| Canada | |||

| Mexique | |||

| Europe | Allemagne | ||

| France | |||

| Royaume-Uni | |||

| Nordiques | |||

| Reste de l'Europe | |||

| Asie-Pacifique | Chine | ||

| Taïwan | |||

| Corée du Sud | |||

| Japon | |||

| Inde | |||

| Reste de l'Asie-Pacifique | |||

| Amérique du Sud | Brésil | ||

| Chili | |||

| Argentine | |||

| Reste de l'Amérique du Sud | |||

| Moyen-Orient et Afrique | Moyen-Orient | Arabie Saoudite | |

| Émirats Arabes Unis | |||

| Turquie | |||

| Reste du Moyen-Orient | |||

| Afrique | Afrique du Sud | ||

| Reste de l'Afrique | |||

Questions clés auxquelles répond le rapport

Quelle est la valeur actuelle du marché de la mémoire vive dynamique ?

Le marché est évalué à 108,68 milliards USD en 2025 et devrait atteindre 232,97 milliards USD d'ici 2030.

Quelle architecture DRAM croît le plus rapidement ?

La DDR5 devrait augmenter à un TCAC de 30,2 %, conduite par les serveurs IA et PC de nouvelle génération.

Pourquoi les prix DRAM sont-ils si volatils en 2025 ?

Les fonderies ont détourné la capacité vers HBM3E à marge plus élevée, menant à un pic de prix au comptant de 50 % pour DDR4 et des augmentations de 15-20 % pour DDR5 en mai 2025.

Comment le secteur automobile influence-t-il la demande DRAM ?

Les véhicules définis par logiciel nécessitent de la DRAM haute température, poussant le contenu mémoire de gigaoctets à un chiffre en 2024 à environ 90 Go dans les prototypes 2025 et bien plus haut dans les futures plateformes EV.

Quelle région devrait croître le plus rapidement jusqu'en 2030 ?

L'Amérique du Sud devrait s'étendre à un TCAC de 22,2 % alors que les incitations d'assemblage local attirent la production électronique.

Qui dirige le segment HBM aujourd'hui ?

SK Hynix a pris de l'avance en étant le premier à fabriquer des piles HBM3E 16 couches, sécurisant une part de 36 % des expéditions DRAM globales au T1 2025.

Dernière mise à jour de la page le: