Taille et part du marché de la mémoire vive statique (SRAM)

Analyse du marché de la mémoire vive statique (SRAM) par Mordor Intelligence

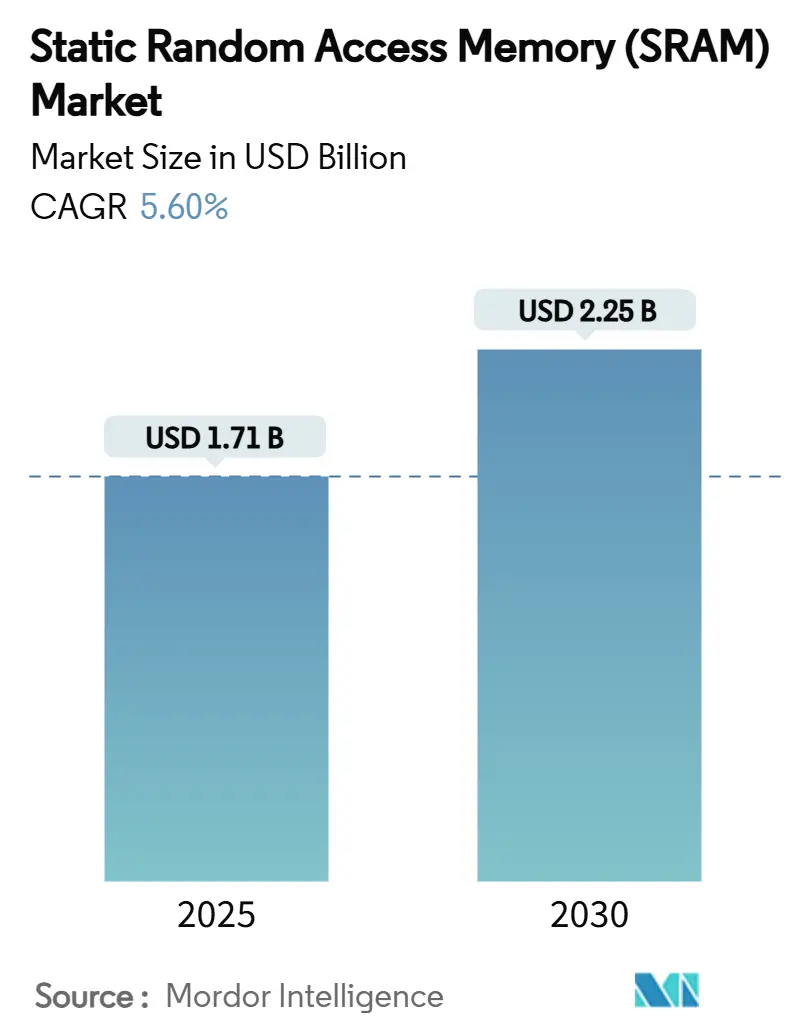

La taille du marché mondial de la mémoire vive statique s'élevait à 1,71 milliard USD en 2025 et devrait progresser à un TCAC de 5,60 % pour atteindre 2,25 milliards USD d'ici 2030. La croissance reflétait la transition vers le calcul centré sur l'IA, les déploiements 5G et le traitement edge en temps réel, qui reposent tous sur la latence ultra-faible de la SRAM pour les hiérarchies de cache. Les fournisseurs de semi-conducteurs ont priorisé la réduction des cellules SRAM à 2 nm pour prendre en charge de plus grands caches L2/L3 tout en maîtrisant les budgets énergétiques. La modernisation des centres de données a stimulé la demande de tampons haute vitesse dans les commutateurs et accélérateurs, tandis que les cycles de renouvellement des appareils grand public ont maintenu une base stable. La résilience de la chaîne d'approvisionnement est devenue cruciale après le séisme de Taiwan de 2024 qui a perturbé la production des fonderies, incitant aux initiatives de diversification géographique. Parallèlement, les mémoires non volatiles émergentes telles que la MRAM ont intensifié la pression concurrentielle sur la SRAM conventionnelle dans les conceptions sauvegardées par batterie.[1]Everspin Technologies, "MRAM Replaces nvSRAM," everspin.com

Principaux points clés du rapport

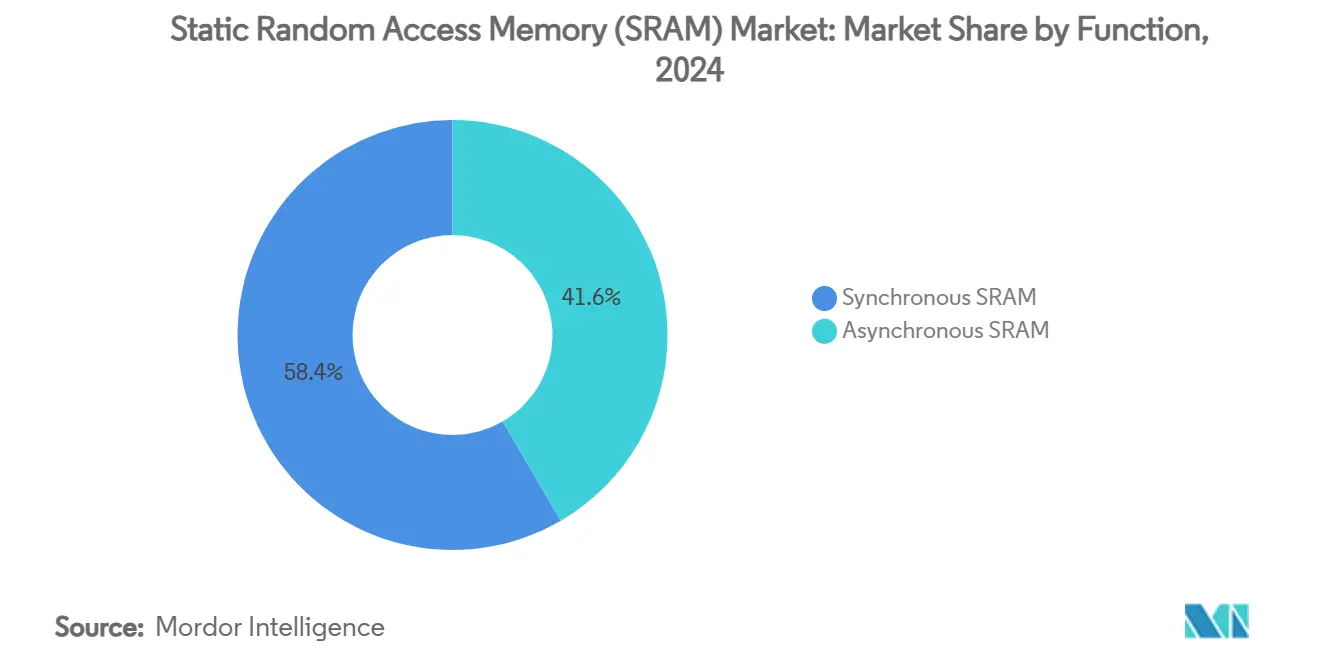

Par fonction, la SRAM synchrone détenait 58,4 % de la part du marché de la mémoire vive statique en 2024 ; la SRAM asynchrone a affiché le TCAC le plus rapide de 6,4 % jusqu'en 2030.

Par type de produit, la pseudo-SRAM menait avec 54,4 % de part de revenus en 2024, tandis que la SRAM non volatile devrait s'étendre à un TCAC de 8,7 %.

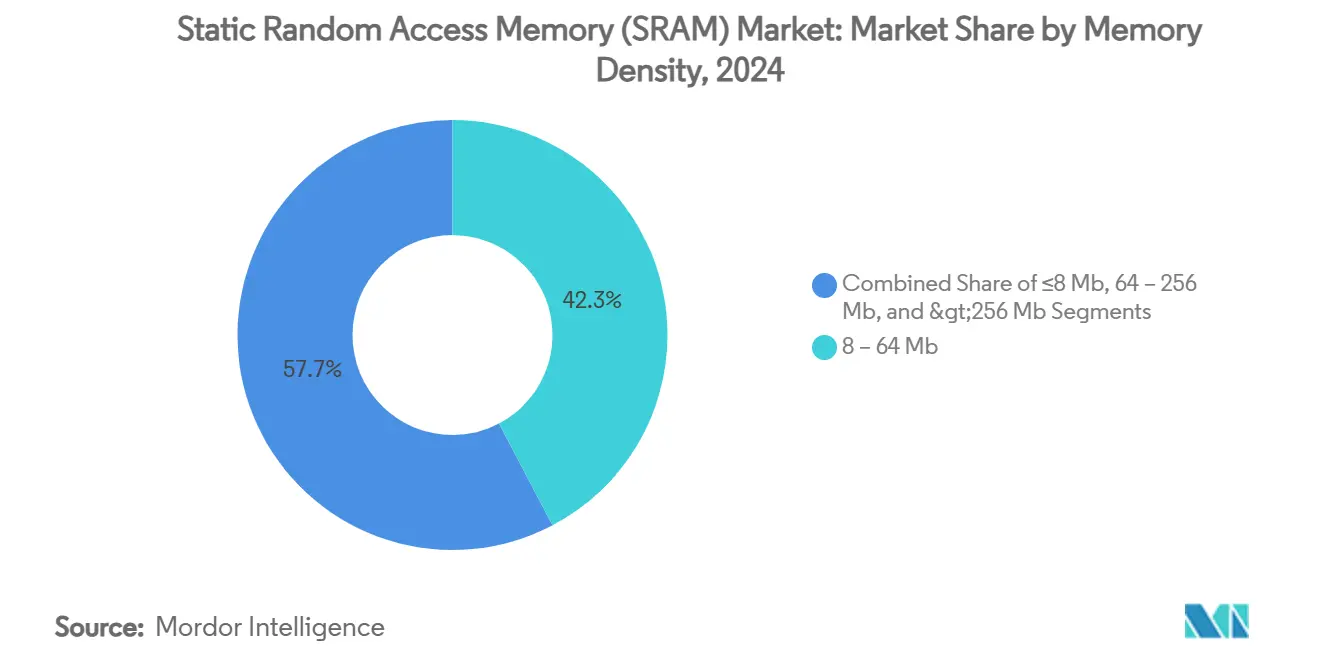

Par densité mémoire, le niveau 8-64 Mb représentait 42,3 % de la taille du marché de la mémoire vive statique en 2024 ; les densités supérieures à 256 Mb sont prêtes à croître à un TCAC de 7,5 %.

Par utilisateur final, l'électronique grand public a capturé 46,3 % des revenus en 2024 ; l'automobile et l'aérospatiale progressent à un TCAC de 9,1 %.

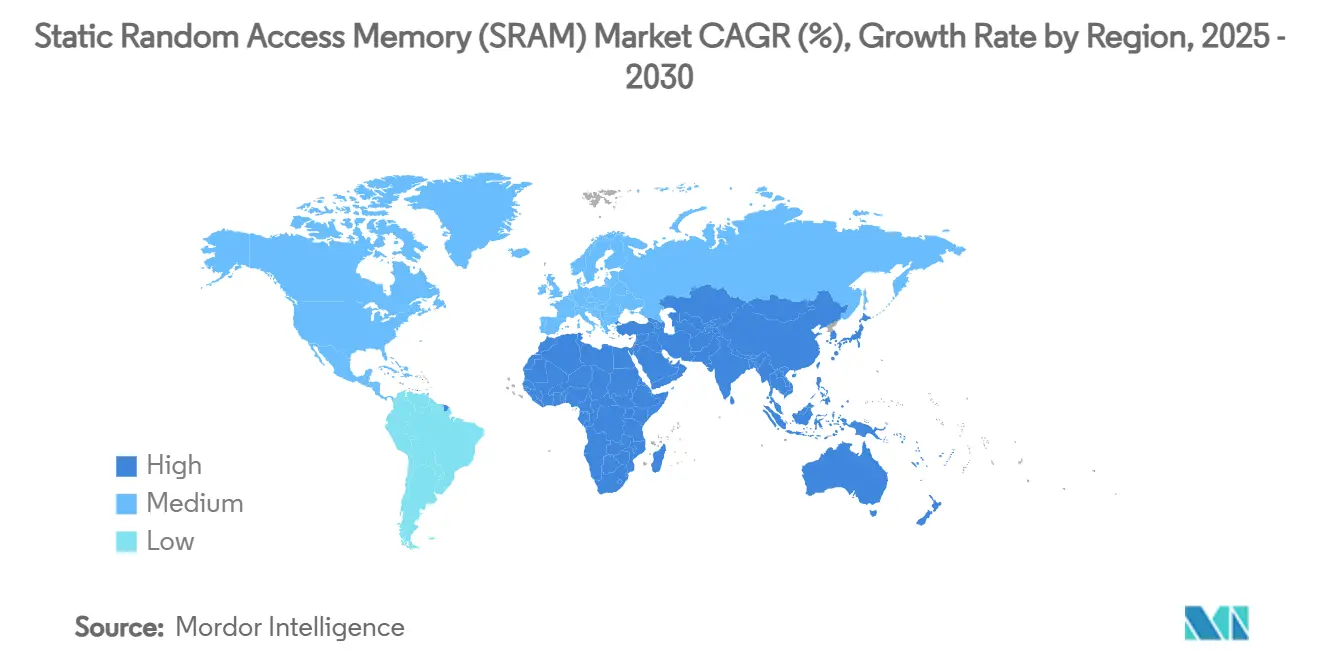

Par géographie, l'Asie-Pacifique commandait 61,4 % de part du marché de la mémoire vive statique en 2024, tandis que le Moyen-Orient et l'Afrique sont les régions à croissance la plus rapide avec un TCAC de 7,5 %.

Tendances et aperçus du marché mondial de la mémoire vive statique (SRAM)

Analyse d'impact des moteurs

| Moteur | (~) % d'impact sur les prévisions de TCAC | Pertinence géographique | Calendrier d'impact |

|---|---|---|---|

| Demande croissante de mémoires cache plus rapides | +1.2% | Mondial, concentré en Amérique du Nord et Asie-Pacifique | Moyen terme (2-4 ans) |

| Construction de centres de données et réseaux 5G | +1.0% | Mondial, avec accent sur l'Asie-Pacifique et l'Amérique du Nord | Court terme (≤ 2 ans) |

| Prolifération des appareils IoT et portables | +0.8% | Mondial, mené par les centres de fabrication d'Asie-Pacifique | Moyen terme (2-4 ans) |

| SRAM intégrée 3D pour chiplets | +0.6% | Founderies avancées d'Amérique du Nord et d'Asie-Pacifique | Long terme (≥ 4 ans) |

| SRAM durcie aux radiations pour satellites LEO | +0.4% | Mondial, concentré en Amérique du Nord et Europe | Long terme (≥ 4 ans) |

| Adoption d'accélérateurs IA en mémoire | +0.7% | Mondial, avec leadership de l'Amérique du Nord et l'Asie-Pacifique | Moyen terme (2-4 ans) |

| Source: Mordor Intelligence | |||

Demande croissante de mémoires cache plus rapides

Les CPU et GPU avancés livrés en 2025 comportaient des caches on-chip plus grands pour réduire la latence d'inférence, avec le Xeon 6 d'Intel montrant une amélioration des performances de 1,4× liée à l'optimisation du cache. La plateforme 2 nm de TSMC offrait une densité de cellules SRAM plus élevée que les nœuds 18A concurrents, donnant aux clients hyperscale plus de cache L3 par watt. Marvell a dévoilé une SRAM personnalisée 2 nm qui embarque 6 Gb de mémoire basse consommation, réduisant l'usage énergétique de 66 % par rapport aux nœuds précédents. Ces innovations ont permis aux accélérateurs IA de maintenir les paramètres de modèle plus près des unités de calcul, soutenant le débit tout en contenant le trafic DRAM. Par conséquent, le marché de la mémoire vive statique a bénéficié des mises à niveau récurrentes de capacité à travers le silicium de centre de données et edge.

Construction de centres de données et réseaux 5G

Les opérateurs cloud ont doublé les densités de rack pour héberger les serveurs IA, incitant à une utilisation plus large des tampons de paquets basés sur SRAM dans les commutateurs top-of-rack. Microsoft a testé des backplanes sans fil 246-275 GHz dans les halls de serveurs, où la mise en tampon à l'échelle de la microseconde reposait sur la SRAM haute vitesse. Le transport 5G convergé de Cisco a promu une latence déterministe, nécessitant des files d'attente SRAM profondes dans les routeurs. Corning prévoit un bond de 18× dans la demande de fibre par rack IA, reflétant la montée en charge des tampons de commutateurs construits sur SRAM synchrone. Cette vague d'infrastructure a renforcé la visibilité des revenus à court terme pour le marché de la mémoire vive statique.

Prolifération des appareils IoT et portables

Les puces edge ultra-basse consommation alimentant les objets connectés de santé ont adopté des blocs SRAM personnalisés qui conservent les données à quelques microwatts ; les processeurs neuraux de Syntiant illustraient cette tendance. Les passerelles Edge2LoRa ont intégré une SRAM modeste pour prétraiter les données de capteurs, réduisant la bande passante de liaison de retour de 90 %. Les MCU automobiles comme le R-Car de Renesas intègrent une SRAM déterministe pour les mises à jour over-the-air et les charges de travail ADAS. Collectivement, ces déploiements ont élargi la base client pour les produits SRAM asynchrones et pseudo-SRAM adaptés aux contraintes énergétiques.

Adoption d'accélérateurs IA en mémoire

Les prototypes de recherche ont démontré une SRAM photonique avec logique XOR intégrée s'exécutant à >10 GHz tout en consommant 13,2 fJ par bit, pointant vers de futures architectures compute-in-memory. Une SRAM compute-in-memory de 28 nm 36 Kb a réduit l'énergie de mise à jour des poids, ouvrant la voie aux moteurs d'inférence IA intégrés. Le PERSYST d'Everspin a positionné la mémoire persistante pour les charges de travail IA critiques pour la sécurité où la rétention des données est requise après une perte d'alimentation. Ces avancées ont accru l'intérêt pour la SRAM spécialisée qui mélange vitesse et programmabilité, élargissant davantage le marché de la mémoire vive statique.

Analyse d'impact des contraintes

| Contrainte | (~) % d'impact sur les prévisions de TCAC | Pertinence géographique | Calendrier d'impact |

|---|---|---|---|

| Coût élevé par bit vs. DRAM/NAND | -0.9% | Mondial, impactant particulièrement les applications sensibles au coût | Court terme (≤ 2 ans) |

| Escalade de puissance aux nœuds ≤5 nm | -0.7% | Founderies avancées en Asie-Pacifique et Amérique du Nord | Moyen terme (2-4 ans) |

| Déplacement par NVM émergentes (MRAM/ReRAM) | -0.5% | Mondial, avec adoption précoce dans l'automobile et l'industrie | Long terme (≥ 4 ans) |

| Perte de rendement due à la variabilité lithographique | -0.4% | Nœuds de processus avancés mondialement | Moyen terme (2-4 ans) |

| Source: Mordor Intelligence | |||

Coût élevé par bit vs. DRAM/NAND

La SRAM restait plusieurs fois plus chère par bit que la DRAM de commodité, mettant la pression sur les concepteurs pour réduire l'usage dans les gadgets grand marché. Les prix des modules DDR4 ont grimpé d'environ 50 % au S1 2025, illustrant la volatilité à travers la pile mémoire. Samsung a tiré parti du resserrement de l'offre pour relever les prix LPDDR4, mais cette tactique risquait d'accélérer l'intérêt des OEM pour les architectures hybrides SRAM-DRAM afin de freiner les nomenclatures. Par conséquent, le marché de la mémoire vive statique a fait face à une résistance dans les segments grand public d'entrée de gamme jusqu'à ce que les compromis densité-versus-coût s'améliorent.

Déplacement par NVM émergentes (MRAM/ReRAM)

Les jonctions tunnel magnétiques CoFeB/MgO à nanomètre unique ont atteint une commutation sub-10 ns et une rétention de dix ans, permettant à la MRAM de remplacer la nvSRAM dans les systèmes robustes. Everspin commercialisait la MRAM comme substitut plug-in pour la SRAM sauvegardée par batterie, offrant la non-volatilité sans condensateurs externes. Les fournisseurs FPGA automobiles comme Lattice sont passés de la flash à la mémoire de configuration MRAM, démontrant une adoption réelle.[2]Jim Tavacoli, "From Flash to MRAM," Lattice Semiconductor, latticesemi.com Si les coûts de production baissent davantage, une partie du marché de la mémoire vive statique pourrait migrer vers des alternatives persistantes.

Analyse de segment

Par fonction : Les performances dépendent des architectures synchrones

La SRAM synchrone a capturé 58,4 % de la part du marché de la mémoire vive statique en 2024, soulignant son caractère indispensable pour le fonctionnement déterministe du cache dans les CPU, GPU et ASIC réseau. Les MCU automobiles ont utilisé des matrices synchrones pour satisfaire les exigences temps réel strictes des charges de travail d'assistance au conducteur. Le segment maintiendra son leadership alors que les nœuds avancés étendent les enveloppes de fréquence et réduisent les tensions de cœur.

La SRAM asynchrone s'est étendue à un TCAC de 6,4 % et a de plus en plus servi les objets connectés portables et passerelles edge où les budgets énergétiques priment sur les objectifs de latence. Les conceptions économes en énergie ont éliminé les arbres d'horloge et simplifié les layouts de cartes, un atout pour les appareils de santé fonctionnant sur batterie employant les coprocesseurs neuraux de Syntiant. Cette divergence a souligné la tendance du marché de la mémoire vive statique vers l'optimisation spécifique aux applications plutôt que la poursuite de performances universelles.

Note: Parts de segment de tous les segments individuels disponibles à l'achat du rapport

Par type de produit : La pseudo-SRAM optimisée en coût prévaut

La pseudo-SRAM détenait une part de 54,4 % en 2024 en intégrant des cellules DRAM derrière une interface de style SRAM, atteignant une densité plus élevée sans gestion de rafraîchissement au niveau système. RAAAM Memory Technologies et NXP revendiquaient 50 % d'économie de surface et 10× d'économie de puissance versus la SRAM haute densité classique, séduisant les microcontrôleurs grand marché.

La SRAM non volatile a cru le plus rapidement à un TCAC de 8,7 % alors que les usines et véhicules exigeaient l'intégrité des données pendant les chutes de tension. Les acteurs de l'automatisation industrielle ont sélectionné des modules nvSRAM pour protéger les variables de processus, évitant les temps d'arrêt coûteux. Bien que niche, cette cohorte a enrichi le paysage du marché de la mémoire vive statique avec des fonctionnalités de résilience à valeur ajoutée.

Par densité mémoire : Le milieu de gamme reste le point optimal

Le niveau 8-64 Mb représentait 42,3 % de la taille du marché de la mémoire vive statique en 2024, correspondant aux empreintes de cache L2/L3 typiques à travers les CPU mainstream. La SRAM rapide 32 Mb d'Alliance Memory en package FBGA illustrait le raffinement continu dans cette zone.

Les dispositifs >256 Mb ont affiché un TCAC robuste de 7,5 % alors que les accélérateurs IA cherchaient des caches on-chip plus grands pour minimiser les accès DRAM. Micron projetait que les automobiles transporteraient bientôt 90 GB de mémoire totale, suggérant une demande croissante de SRAM haute densité dans les contrôleurs zonaux. L'évolution de la densité reflétait donc la croissance des charges de travail compute-intensives soutenant le marché de la mémoire vive statique.

Par utilisateur final : Volume grand public vs. vélocité automobile

L'électronique grand public a généré 46,3 % des revenus 2024 grâce à l'échelle vaste des smartphones, tablettes et PC. Micron et Samsung ont intégré LPDDR5X et SRAM embarquée dans le Galaxy S24, élevant la réactivité IA mobile.

Les segments automobile et aérospatial ont enregistré un TCAC de 9,1 % alors que les véhicules définis par logiciel nécessitaient un cache déterministe pour la fusion de capteurs et la reconfiguration over-the-air. Le MCU S32K5 de NXP avec RAM magnétique intégrée écrit 15× plus vite que la flash, démontrant l'appétit pour la mémoire haute fiabilité.[3]NXP Semiconductors, "S32K5 MCU," stocktitan.net Cette dynamique a élargi le marché de la mémoire vive statique au-delà des cycles de renouvellement grand public traditionnels.

Analyse géographique

L'Asie-Pacifique a conservé 61,4 % de part du marché de la mémoire vive statique en 2024, alimentée par la domination des fonderies de Taiwan, l'innovation mémoire de la Corée du Sud et les efforts de montée en échelle de la Chine. L'ascension de SK Hynix à 36 % de la production DRAM mondiale a souligné la profondeur technologique de la région. Pourtant, le séisme de Taiwan 2024 a exposé le risque de concentration, incitant aux fonderies de contingence au Japon et Singapour. Le Japon projetait des ventes d'équipement semi-conducteur de 5,51 trillions JPY (38,35 milliards USD) en AF26, soulignant la construction continue de capacité.

Le Moyen-Orient et l'Afrique ont tracé le TCAC le plus rapide de 7,5 %, ancré par les dépenses de fonds souverains pour positionner le Golfe comme hub de données tri-continental. L'automatisation d'entrepôts dans la région était programmée pour une croissance annuelle de 17,5 % jusqu'à 1,6 milliard USD d'ici 2025, stimulant la demande de caches embarqués fiables. Les projets énergétiques africains ont alloué 730 milliards USD en nouvelles dépenses d'investissement jusqu'en 2030, nécessitant des systèmes de contrôle industriel qui s'appuient sur la SRAM pour une réponse déterministe.

L'Amérique du Nord s'est concentrée sur les déploiements de centres de données IA, tandis que l'Europe a misé sur la souveraineté à travers la Loi sur les puces de 43 milliards EUR. STMicroelectronics a sécurisé 5 milliards EUR (5,4 milliards USD) pour un campus de carbure de silicium en Italie, élargissant la compétence régionale en électronique de puissance qui consomme aussi de la SRAM spécialisée. Les pénuries de talents menacent cependant l'expansion, ASML avertissant qu'elle pourrait déplacer ses opérations si l'immigration se resserrait. Ces contrastes soulignent les leviers régionaux divers façonnant le marché de la mémoire vive statique.

Paysage concurrentiel

Le marché a affiché une consolidation modérée autour des fabricants de dispositifs intégrés et challengers alignés sur les fonderies. Samsung, SK Hynix et Micron ont fortifié leurs positions en échelonnant les roadmaps HBM ; Samsung a accéléré sa fab de wafers de Pyeongtaek pour saisir les affaires HBM4. SK Hynix s'est associé avec TSMC sur l'emballage avancé pour maintenir le leadership en bande passante.[4]SK hynix, "Partners with TSMC to Strengthen HBM Leadership," skhynix.com

Au niveau IP et spécialisé, GSI Technology et Cypress ont ciblé les équipements réseau basse latence, tandis que les nouveaux venus comme Numem planifiaient des chiplets MRAM promettant un débit de classe HBM d'ici 2025. Imec, TSMC et Samsung-IBM ont chacun démontré des prototypes SRAM CFET avec 40 % de réduction de surface de cellule, anticipant les hybrides logique-mémoire empilés 3D.

Les niches émergentes incluaient les cellules 18T durcies aux radiations pour satellites LEO qui amélioraient la stabilité de lecture tout en réduisant la puissance de veille. Le financement du Conseil européen de l'innovation a permis à RAAAM d'avancer sur la pseudo-SRAM on-chip pour les marchés MCU, illustrant comment la politique régionale a catalysé les nouveaux entrants. L'avantage concurrentiel a ainsi pivoté sur l'innovation d'emballage, le savoir-faire de processus spécialisé et l'étendue de propriété intellectuelle, tous façonnant le positionnement futur du marché de la mémoire vive statique.

Leaders de l'industrie de la mémoire vive statique (SRAM)

-

Renesas Electronics Corporation

-

STMicroelectronics N.V.

-

Toshiba Corporation

-

Cypress Semiconductor

-

Integrated Silicon Solution, Inc. (ISSI)

- *Avis de non-responsabilité : les principaux acteurs sont triés sans ordre particulier

Développements récents de l'industrie

- Juillet 2025 : Samsung a accéléré l'usine de wafers de Pyeongtaek pour sécuriser la capacité HBM4.

- Juin 2025 : Marvell a introduit une SRAM personnalisée 2 nm offrant une capacité de 6 Gb à 66 % de puissance en moins.

- Juin 2025 : SK Hynix a affiché une hausse de bénéfice de 9 trillions KRW sur la demande HBM.

- Mai 2025 : Samsung et SK Hynix ont avancé le collage hybride pour la prochaine génération HBM.

Portée du rapport sur le marché mondial de la mémoire vive statique (SRAM)

La SRAM (RAM statique) est une mémoire vive (RAM) qui conserve les bits de données dans sa mémoire tant que l'alimentation est fournie. Contrairement à la RAM dynamique (DRAM), qui stocke les bits dans des cellules constituées d'un condensateur et d'un transistor, la SRAM n'a pas besoin d'être rafraîchie périodiquement. La RAM statique fournit un accès plus rapide aux données et est plus chère que la DRAM.

| SRAM asynchrone |

| SRAM synchrone |

| Pseudo SRAM (PSRAM) |

| SRAM non volatile (nvSRAM) |

| Autres types de produits |

| ≤8 Mb |

| 8 - 64 Mb |

| 64 - 256 Mb |

| >256 Mb |

| Électronique grand public |

| Industriel |

| Infrastructure de communication |

| Automobile et aérospatial |

| Autres utilisateurs finaux |

| Amérique du Nord | États-Unis | |

| Canada | ||

| Mexique | ||

| Amérique du Sud | Brésil | |

| Argentine | ||

| Reste de l'Amérique du Sud | ||

| Europe | Allemagne | |

| Royaume-Uni | ||

| France | ||

| Italie | ||

| Russie | ||

| Reste de l'Europe | ||

| Asie-Pacifique | Chine | |

| Japon | ||

| Corée du Sud | ||

| Inde | ||

| Taïwan | ||

| Reste de l'Asie-Pacifique | ||

| Moyen-Orient et Afrique | Moyen-Orient | Turquie |

| Israël | ||

| Pays du CCG | ||

| Reste du Moyen-Orient | ||

| Afrique | Afrique du Sud | |

| Nigeria | ||

| Reste de l'Afrique | ||

| Par fonction | SRAM asynchrone | ||

| SRAM synchrone | |||

| Par type de produit | Pseudo SRAM (PSRAM) | ||

| SRAM non volatile (nvSRAM) | |||

| Autres types de produits | |||

| Par densité mémoire | ≤8 Mb | ||

| 8 - 64 Mb | |||

| 64 - 256 Mb | |||

| >256 Mb | |||

| Par utilisateur final | Électronique grand public | ||

| Industriel | |||

| Infrastructure de communication | |||

| Automobile et aérospatial | |||

| Autres utilisateurs finaux | |||

| Par géographie | Amérique du Nord | États-Unis | |

| Canada | |||

| Mexique | |||

| Amérique du Sud | Brésil | ||

| Argentine | |||

| Reste de l'Amérique du Sud | |||

| Europe | Allemagne | ||

| Royaume-Uni | |||

| France | |||

| Italie | |||

| Russie | |||

| Reste de l'Europe | |||

| Asie-Pacifique | Chine | ||

| Japon | |||

| Corée du Sud | |||

| Inde | |||

| Taïwan | |||

| Reste de l'Asie-Pacifique | |||

| Moyen-Orient et Afrique | Moyen-Orient | Turquie | |

| Israël | |||

| Pays du CCG | |||

| Reste du Moyen-Orient | |||

| Afrique | Afrique du Sud | ||

| Nigeria | |||

| Reste de l'Afrique | |||

Questions clés répondues dans le rapport

Quelle est la valeur actuelle du marché de la mémoire vive statique ?

Le marché a atteint 1,71 milliard USD en 2025 et devrait grimper à 2,25 milliards USD d'ici 2030.

Quelle région domine les revenus du marché de la mémoire vive statique ?

L'Asie-Pacifique représentait 61,4 % des revenus mondiaux en 2024, ancrée par les écosystèmes de fabrication de Taiwan et de la Corée du Sud.

Quel segment du marché de la mémoire vive statique croît le plus rapidement ?

Les applications automobile et aérospatiales s'étendent à un TCAC de 9,1 % alors que les véhicules adoptent des architectures définies par logiciel nécessitant des caches basse latence.

Comment la technologie MRAM émergente impacte-t-elle la demande SRAM ?

La MRAM offre la non-volatilité et une puissance de veille plus faible, défiant la SRAM dans les systèmes sauvegardés par batterie et robustes, détournant potentiellement la part à long terme.

Quelle classe de densité est la plus commune dans les puces SRAM actuelles ?

La plage 8-64 Mb a capturé 42,3 % des ventes 2024 car elle s'aligne avec les tailles de cache de processeur mainstream.

Pourquoi la SRAM synchrone a-t-elle dépassé les types asynchrones en part de revenus ?

Les conceptions synchronisées par horloge fournissent un timing déterministe essentiel pour les CPU, GPU et ASIC réseau haute performance, sécurisant 58,4 % de part de marché en 2024.

Dernière mise à jour de la page le: