Taille et part du marché de la mémoire de nouvelle génération

Analyse du marché de la mémoire de nouvelle génération par Mordor Intelligence

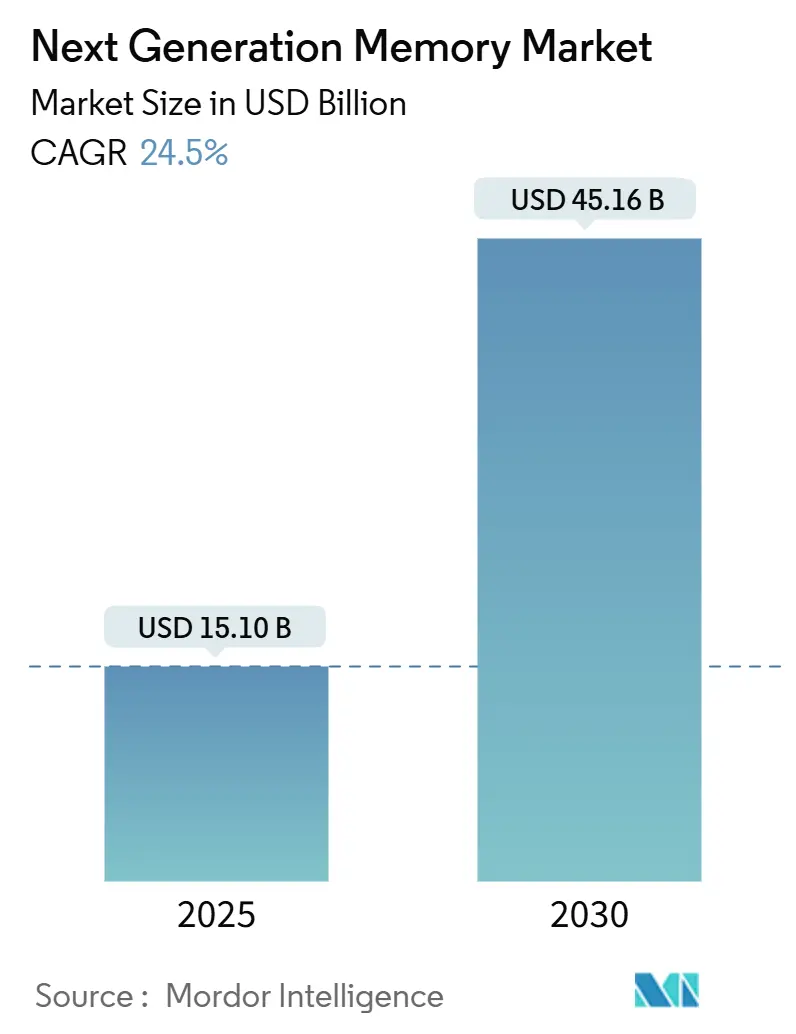

La taille du marché de la mémoire de nouvelle génération était évaluée à 15,10 milliards USD en 2025 et devrait atteindre 45,16 milliards USD d'ici 2030, reflétant un TCAC vigoureux de 24,5 %. La demande s'est accélérée alors que les clusters de formation IA, les serveurs de périphérie et les véhicules autonomes se sont tous confrontés au mur de latence des hiérarchies DRAM-NAND conventionnelles. Les fournisseurs ont priorisé les architectures à large bande passante, les dispositifs de classe de stockage persistant et l'emballage avancé pour combler l'écart grandissant entre calcul et mémoire. L'Asie-Pacifique est restée la centrale de production, tandis que les incitations aux usines nord-américaines ont favorisé une capacité parallèle. Les innovations d'interface telles que Compute Express Link (CXL) et Universal Chiplet Interconnect Express (UCIe) ont commencé à redessiner les philosophies de conception système, encourageant des pools de mémoire désagrégés qui évoluent presque linéairement avec le nombre d'accélérateurs. Les contraintes d'approvisionnement pour les nœuds premium et les wafers ont cependant continué à façonner les stratégies de prix et d'allocation sur le marché de la mémoire de nouvelle génération.

Points clés du rapport

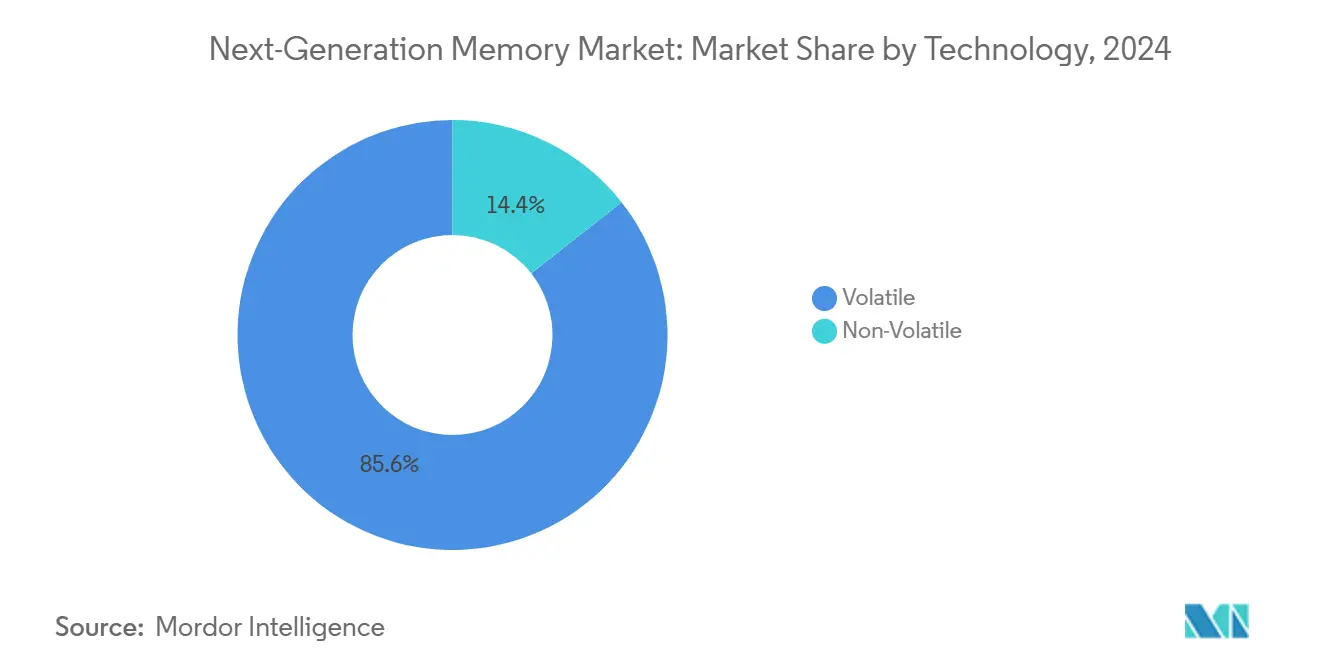

- Par technologie, les dispositifs volatiles (HBM, HMC, LPDDR5X) ont dominé avec 85,6 % de part de revenus en 2024, tandis que la ReRAM devrait croître à un TCAC de 38,3 % jusqu'en 2030.

- Par interface mémoire, DDR/LPDDR détenait 38,3 % de la part de marché de la mémoire de nouvelle génération en 2024 ; CXL / UCIe croît à 48,3 % de TCAC jusqu'en 2030.

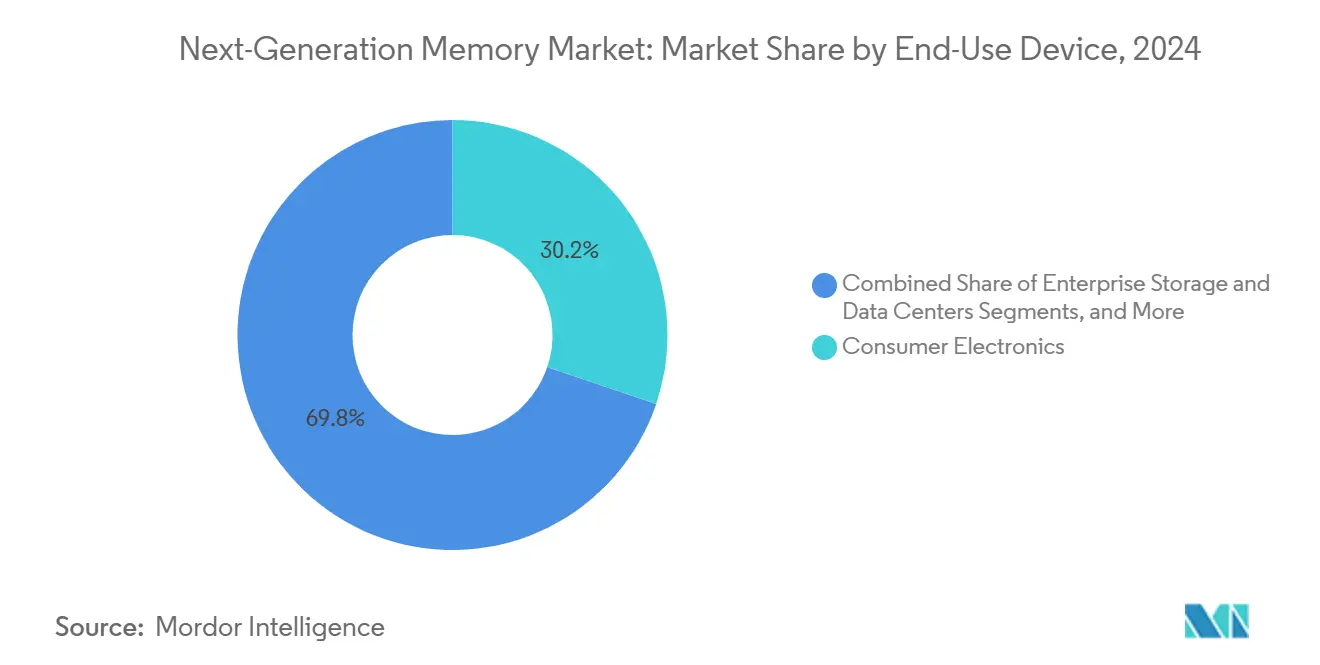

- Par dispositif d'utilisation finale, l'électronique grand public commandait 30,2 % de la taille du marché de la mémoire de nouvelle génération en 2024 ; l'électronique automobile devrait croître à 37,3 % de TCAC jusqu'en 2030.

- Par taille de wafer, 300 mm occupait 72,5 % de la production en 2024, tandis que les wafers de 450 mm devraient grimper à 42,3 % de TCAC.

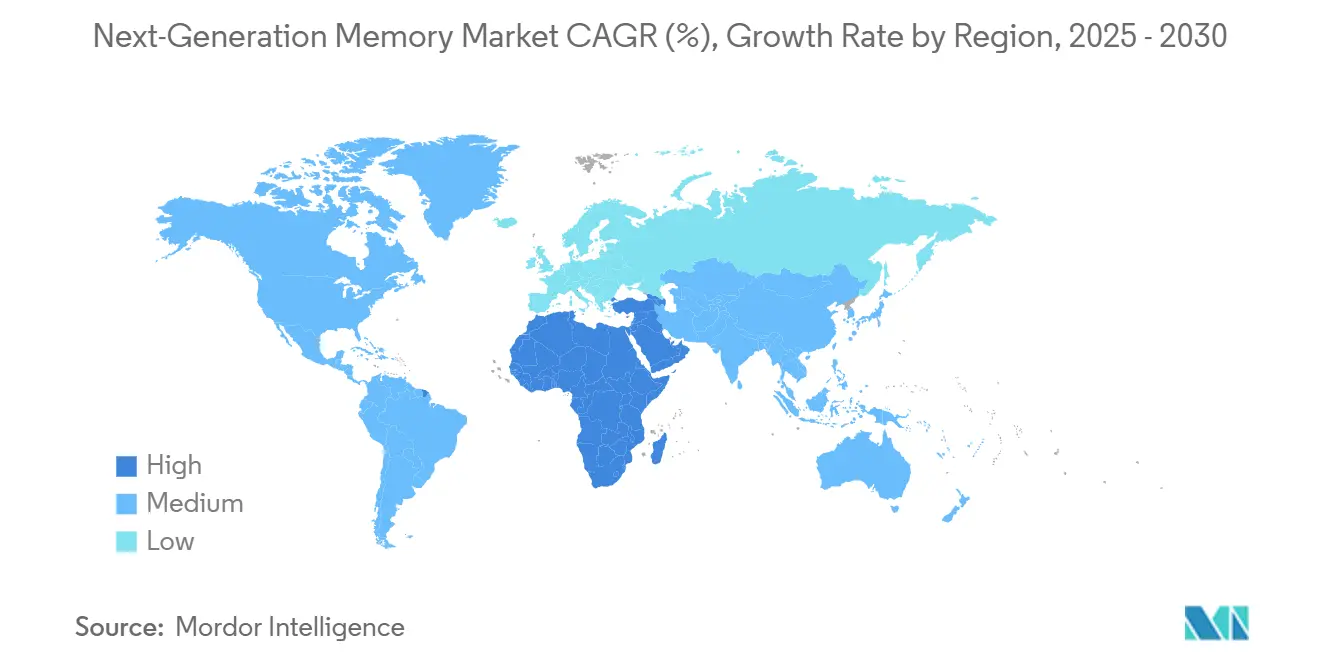

- Par géographie, l'Asie-Pacifique détenait 47,3 % des revenus en 2024 ; la région Moyen-Orient et Afrique est positionnée pour un TCAC de 31,2 % sur 2025-2030.

Tendances et perspectives du marché mondial de la mémoire de nouvelle génération

Analyse de l'impact des moteurs

| Moteur | (~) % d'impact sur les prévisions TCAC | Pertinence géographique | Échéancier d'impact |

|---|---|---|---|

| Demande axée sur l'IA pour HBM dans les centres de données hyperscale | 7.0% | Amérique du Nord, Asie-Pacifique, Europe | Moyen terme (2-4 ans) |

| Besoin ADAS L4 automobile pour mémoire persistante instantanée | 4.5% | Amérique du Nord, Europe, Asie-Pacifique | Long terme (≥ 4 ans) |

| Migration smartphone vers LPDDR5X et ReRAM embarquée | 3.8% | Mondial, avec impact le plus fort en Asie-Pacifique | Court terme (≤ 2 ans) |

| Programmes nationaux de localisation mémoire | 2.5% | Moyen-Orient et Afrique, Europe, Asie-Pacifique | Moyen terme (2-4 ans) |

| Edge-IoT industriel nécessitant FRAM ultra-basse consommation | 1.7% | Amérique du Nord, Europe, Asie-Pacifique | Moyen terme (2-4 ans) |

| Bases de données en mémoire persistantes axées confidentialité utilisant 3D XPoint | 1.2% | Amérique du Nord, Europe | Court terme (≤ 2 ans) |

| Source: Mordor Intelligence | |||

| Source: Mordor Intelligence | |||

Demande axée sur l'IA pour HBM dans les centres de données hyperscale

Les tailles croissantes des modèles de transformateur ont forcé les opérateurs cloud à doubler les budgets DRAM et stockage solide au niveau serveur, faisant de la bande passante plutôt que de la capacité le principal goulot d'étranglement. La mémoire à large bande passante a multiplié le débit de liaison au-delà de 1,5 To/s et a livré des économies d'énergie dramatiques par bit déplacé.[1]SK hynix, "SK hynix Sold Out of HBM for 2025," tweaktown.com L'allocation mondiale s'est resserrée lorsque SK Hynix a rapporté que toute sa production HBM 2025 était vendue à l'avance, ce qui a incité à des réservations de volume à long terme pour 2026. Micron a observé qu'un serveur IA déploie près de deux fois la DRAM d'un nœud x86 classique. Le marché de la mémoire de nouvelle génération a donc pivoté du leadership coût-bit vers le leadership bande passante, créant des niveaux de prix premium et des opportunités d'expansion de marge.

L'ADAS L4 automobile nécessite une mémoire persistante instantanée

L'autonomie de niveau 4 exige une récupération déterministe après les événements d'alimentation et des températures de fonctionnement difficiles au-delà de 150 °C. Les dispositifs RAM ferroélectriques résistent à 10¹⁴ cycles tout en conservant les données sans alimentation de veille, assurant la disponibilité de démarrage à froid pour les piles de fusion de capteurs qui génèrent jusqu'à 100 Go/s. Les constructeurs automobiles évaluent maintenant des hybrides persistants-volatiles asymétriques combinant FRAM avec des tampons de travail LPDDR5X. Ces architectures protègent les journaux de mission, facilitent les mises à jour par voie hertzienne et soutiennent les objectifs de sécurité fonctionnelle sous ISO 26262, renforçant la croissance du marché de la mémoire de nouvelle génération à travers la chaîne de valeur de la mobilité.

Migration smartphone vers LPDDR5X et ReRAM embarquée

Les combinés phares lancés après T3 2025 ont été expédiés exclusivement avec LPDDR5X capable de 9,6 GT/s, réduisant l'énergie dynamique par bit de 30 % par rapport à LPDDR5. Simultanément, les OEM mondiaux ont intégré des blocs ReRAM pour stocker les modèles IA et les identifiants biométriques, supprimant la latence des accès Flash externes. L'annonce de Samsung de cesser la production DDR4 d'ici juin 2025 a cristallisé l'inflexion. Les modules LPDDR+ReRAM intégrés équilibrent performance et endurance de veille, élargissant les revenus totaux adressables par combiné et faisant progresser le marché de la mémoire de nouvelle génération.

Programmes nationaux de localisation mémoire

Les tensions géopolitiques et les pénuries de l'ère pandémique ont poussé les gouvernements à réduire les risques des chaînes d'approvisionnement. La loi américaine CHIPS de 52,7 milliards USD a incité les usines DRAM et HBM domestiques, tandis que la Malaisie est devenue le hub d'assemblage HBM secondaire de Micron. La République tchèque a tracé un plan pour tripler son secteur des semi-conducteurs d'ici 2029 pour renforcer la souveraineté technologique. En parallèle, les champions locaux chinois ont porté leur part de zéro à 5 % d'ici 2024 et visent 10 % d'ici 2025. De tels programmes rééquilibrent les empreintes de capacité mondiale, favorisant les clusters régionaux et élargissant la participation au marché de la mémoire de nouvelle génération.

Analyse de l'impact des contraintes

| Contrainte | (~) % d'impact sur les prévisions TCAC | Pertinence géographique | Échéancier d'impact |

|---|---|---|---|

| Retard wafer 450 mm contraignant la montée en puissance ReRAM | -1.7% | Mondial, avec impact le plus fort en Asie-Pacifique | Moyen terme (2-4 ans) |

| Coût élevé par bit MRAM versus NAND | -1.2% | Mondial | Court terme (≤ 2 ans) |

| Échecs de stabilité thermique de PCM de qualité automobile | -2.5% | Amérique du Nord, Europe, Asie-Pacifique | Moyen terme (2-4 ans) |

| Concentration de fonderie pour STT-MRAM sub-28 nm | -3.8% | Mondial, avec impact le plus fort en Asie-Pacifique | Long terme (≥ 4 ans) |

| Source: Mordor Intelligence | |||

| Source: Mordor Intelligence | |||

Échecs de stabilité thermique de PCM de qualité automobile

Les alliages à changement de phase ont eu du mal à conserver les données au-dessus de 150 °C, mettant en péril l'intégrité de l'enregistreur d'événements dans les déploiements désertiques et sous le capot. L'ingénierie des matériaux a exploré GeSbTe riche en Ge et des paires de cellules PCM en série qui poussent les fenêtres d'endurance à 153 °C mais ajoutent des étapes de lithographie et des coûts. Les cycles de qualification OEM ont donc ralenti l'adoption PCM, déplaçant les victoires de conception à court terme vers FRAM et ReRAM jusqu'à ce que les objectifs de fiabilité soient atteints. La contrainte a comprimé la croissance globale, particulièrement dans le sous-ensemble automobile du marché de la mémoire de nouvelle génération.

Concentration de fonderie pour STT-MRAM sub-28 nm

L'intégration MRAM à transfert de spin à 16 nm nécessite des jonctions tunnel magnétiques perpendiculaires, des chimies de gravure rares et des contrôles de processus serrés. Seulement deux fonderies logiques supportent actuellement le STT-MRAM en volume, provoquant des guerres d'enchères de capacité et laissant les fournisseurs fab-less émergents exposés aux chocs de délais. Les problèmes de fiabilité, tels que la perturbation de lecture et la variabilité induite par le processus, prolongent encore les cycles produit. Ce goulot d'étranglement amplifie l'intensité capitalistique et freine l'élan de scalabilité autrement attendu dans le marché de la mémoire de nouvelle génération.

Analyse par segment

Par technologie : domination volatile avec disruption non-volatile

Les dispositifs volatiles ont livré 85,6 % des revenus 2024, ancrés par les primes de capacité abruptes d'HBM. Cette domination a persisté parce que les accélérateurs IA saturent tout ce qui est en dessous de 1 To/s, assurant que les engagements d'achat HBM s'étendent sur plusieurs exercices fiscaux. La taille du marché de la mémoire de nouvelle génération pour les solutions volatiles devrait continuer à s'étendre en termes absolus même si la part glisse, alors que ReRAM, PCM et MRAM gagnent en crédibilité dans les charges de travail de périphérie et d'instrumentation. ReRAM mène l'élan non-volatile, croissant à 38,3 % de TCAC grâce à de simples piles d'oxyde métallique qui co-fabriquent sur des nœuds 28 nm sans masques supplémentaires.[2]"Advances of Embedded Resistive Random Access Memory," IOPscience, iopscience.iop.org Les gains graduels de stabilité thermique de PCM devraient débloquer l'attachement automobile une fois que le référentiel de rétention 10 ans, 150 °C est certifié. Les avancées MRAM restent liées à la capacité EUV future et à la simplification de processus qui réduit la prime par bit versus NAND.

Structurellement, les fabricants volatiles explorent maintenant les topologies de chiplet empilées, réduisant la zone de puce et répartissant le risque de rendement. Les challengers non-volatiles répondent avec des matrices cross-point et des conceptions sans sélecteur qui éliminent les transistors consommateurs de zone. Sur la période de perspectives, l'accélération d'approvisionnement pour ReRAM et PCM devrait éroder la part volatile d'environ 10 points de pourcentage, bien que les revenus volatiles absolus augmentent encore parce que le TAM des serveurs IA double. Les concepteurs continueront à co-emballer des puces volatiles et non-volatiles, cultivant des piles hybrides qui échangent l'endurance contre la persistance. Ces dynamiques assurent une feuille de route multi-nœuds, élargissant la diversité de solutions au sein du marché de la mémoire de nouvelle génération.

Note: Parts de segment de tous les segments individuels disponibles à l'achat du rapport

Par interface mémoire : ré-architectures CXL / UCIe

Les interfaces se sont adaptées aux accélérateurs affamés de bande passante bien avant que le silicium monolithique puisse suivre le rythme. En 2024, les canaux DDR et LPDDR ont conservé une part de 38,3 %, mais des plafonds d'adoption ont émergé à quatre canaux par socket. L'attachement cohérent de cache de CXL via PCIe 5.0 a assoupli cette limite, regroupant des téraoctets de mémoire derrière des commutateurs partagés et réduisant drastiquement la capacité échouée. L'arrivée de la spécification UCIe 2.0 en août 2024 a livré des chiplets empilés en 3D avec 75 × la bande passante inter-puce précédente, permettant aux hyperscalers de carreler des dizaines de puces de calcul contre une seule pile HBM.

En regardant vers l'avenir, 50 % des nouveaux tape-outs HPC en 2025 intégreront des liens puce-à-puce 2,5D ou 3D, élevant CXL ou UCIe d'optionnel à éléments de conception obligatoires. Les hubs de retiming et les retimers émergent comme des pools de profit auxiliaires. Synchrone à ces changements, PCIe/NVMe continue les mouvements générationnels incrémentaux, mais SATA s'estompe vers des niches d'archivage. Collectivement, les interfaces nouvelles propulsent des déploiements modulaires qui découplent la planification de capacité des cycles de mise à niveau CPU, agrandissant les options de diversification au sein du marché de la mémoire de nouvelle génération.

Par dispositif d'utilisation finale : accélération ADAS automobile

L'électronique grand public a conservé une tranche de revenus de 30,2 % en 2024, avec les smartphones premium intégrant LPDDR5X et des caches toujours actifs soutenus par ReRAM système-dans-paquet. Pourtant, les domaines de calcul véhiculaire sont remarquables. Les piles de conduite assistée s'étendent du niveau 2+ au niveau 4, nécessitant des journaux persistants, des tampons de point de contrôle de capteur et des microcontrôleurs de sécurité qui doivent faire un cycle d'alimentation en millisecondes. Par conséquent, les revenus de mémoire automobile devraient augmenter à 37,3 % de TCAC, surpassant les mises à niveau de combinés.

Le stockage d'entreprise a maintenu un approvisionnement stable pour les matrices de formation IA, mais les installations industrielles de périphérie ont adopté FRAM basse consommation pour atténuer les contraintes de batterie. Les implants médicaux ont exploité la tolérance aux radiations de MRAM, et l'aérospatial a utilisé ReRAM durci aux radiations pour les ordinateurs de guidage. Chaque cas d'usage a ajouté une diversité de volume, élargissant les profils de risque, mais améliorant la résilience totale du marché de la mémoire de nouvelle génération.

Note: Parts de segment de tous les segments individuels disponibles à l'achat du rapport

Par taille de wafer : évolutivité vers 450 mm

En 2024, les substrats de 300 mm ont généré 72,5 % du total des démarrages de wafer, ancrés par les usines DRAM et 3D NAND optimisées pour un débit élevé. Les lignes 200 mm ont persisté pour les mémoires spécialisées matures, en particulier FRAM industriel, où l'outillage est entièrement déprécié. L'économie de migration se déplace maintenant vers 450 mm, promettant 2,5 × la sortie de puce par cycle. Les essais pilotes ont affiché des perspectives de TCAC de 42,3 % même si les obstacles capex ont grimpé à 20 milliards USD par usine. Les fournisseurs de lithographie et de métrologie font la course pour adapter les scanners et l'inspection de défauts au champ plus large.

Cependant, l'adoption ReRAM et MRAM sur 450 mm reste contrainte par la préparation d'outil retardée, faisant écho à l'une des contraintes clés ci-dessus. Néanmoins, l'avantage du premier arrivé peut permettre aux méga-usines de gagner des courbes d'apprentissage favorables, comprimant les structures de coûts et élargissant finalement les applications adressables à travers le marché de la mémoire de nouvelle génération.

Analyse géographique

L'Asie-Pacifique a maintenu son leadership avec 47,3 % des revenus en 2024, soutenue par Samsung, SK Hynix et TSMC, dont les plans capitaux combinés ont dépassé 85 milliards USD pour les nœuds de nouvelle génération. La Chine a avancé sa capacité DRAM indigène à une part globale de 5 % et vise 10 % d'ici 2025, guidée par des subventions d'État et des conditions de prêt préférentielles. Les subventions renouvelées du Japon ont préservé la production NAND locale et les clusters d'équipement spécialisé. L'Inde a lancé des programmes d'incitation à la fabrication qui ont attiré des coentreprises orientées vers l'assemblage, les tests et éventuellement le découpage 3D NAND. Cette profondeur régionale a ancré la sécurité d'approvisionnement et favorisé l'effet de levier de volume pour le marché de la mémoire de nouvelle génération.

L'incitation CHIPS de l'Amérique du Nord a catalysé l'usine HBM de Micron dans l'Idaho et les centres d'assemblage mémoire du Texas, assurant la capacité domestique pour l'approvisionnement défense et hyperscale.[3]Emily G. Blevins et al., "Semiconductors and the CHIPS Act: The Global Context," Congressional Research Service, congress.gov Le Mexique a capturé les flux d'assemblage backend, complétant les démarrages de wafer front-end des États-Unis. Les instituts canadiens ont contribué aux percées de science des matériaux visant les non-volatiles ultra-basse consommation, élargissant le halo recherche et développement du continent.

L'Europe a poursuivi l'autonomie stratégique sous sa loi semi-conducteur, visant une part globale de 20 % d'ici 2030. L'Allemagne a canalisé les subventions vers les consortiums mémoire de qualité automobile, tandis que la France a investi dans les lignes pilotes ReRAM. Le Royaume-Uni a priorisé l'IP agnostique de fonderie pour les tissus puce-à-puce de chiplet. Collectivement, le bloc a cherché une intégration plus serrée entre les OEM automobiles et les maisons mémoire locales, renforçant la demande régionale dans le marché de la mémoire de nouvelle génération.

Le Moyen-Orient et l'Afrique ont exhibé la trajectoire la plus rapide, avec des perspectives de TCAC de 31,2 % soutenues par des usines soutenues par des fonds souverains en Arabie Saoudite et aux EAU. La Turquie s'est commercialisée comme un hub d'emballage eurasien, et l'Afrique du Sud a tiré parti de la densification des télécoms pour stimuler l'adoption de mémoire grand public. Bien que la base soit modeste, les allocations de capital agressives et la montée en compétences de la main-d'œuvre suggèrent un avantage durable pour la part de la région du marché de la mémoire de nouvelle génération.

Paysage concurrentiel

Le champ concurrentiel est resté oligopolistique. Samsung, SK Hynix et Micron ont conjointement contrôlé environ 60 % des revenus agrégés, avec une domination encore plus élevée dans les niveaux HBM. Les accords d'approvisionnement à long terme, les brevets d'emballage avancé et les créneaux de volume pré-tarifés ont consolidé leurs positions. Pourtant, les nouveaux entrants chinois tels que CXMT et YMTC ont appliqué des stratégies de réduction des coûts, offrant 20-30 % de prix inférieur par gigaoctet pour la DRAM grand public, s'infiltrant ainsi dans les contrats d'ordinateurs portables et IoT. Leur part combinée devrait doubler d'ici 2025, diluant progressivement le leadership en marge des titulaires.

Dans le coin spécialisé non-volatile, Everspin et Weebit Nano se sont différenciés par des approches centrées sur la conception plutôt que par l'échelle de wafer. Weebit Nano a sécurisé de nouveaux brevets couvrant les matrices de cellules sans sélecteur, adressant la dérive d'endurance en dessous de 40 nm. Everspin a expédié des modules STT-MRAM pour la robotique industrielle nécessitant une latence d'écriture déterministe. Un tel positionnement de niche a permis l'agilité malgré l'accès fonderie restreint, favorisant des couches d'innovation qui enrichissent le marché de la mémoire de nouvelle génération.

Tous les acteurs ont de plus en plus exploré la collaboration. Marvell s'est associé avec les trois principales maisons DRAM pour co-définir SOCAMM, une spécification de module regroupant les puces DRAM et logique pour les ordinateurs portables IA. Synopsys a enregistré l'IP PHY UCIe sur TSMC N3E, offrant des flux d'outils clés en main aux entreprises fab-less.[4]Farhana Goriawalla and Yervant Zorian, "Multi-Die Health and Reliability Advances," Synopsys, synopsys.com Ces alliances suggèrent un écosystème où l'interface, l'emballage et la co-optimisation logicielle produisent un nouveau levier au-delà du volume de wafer seul.

Leaders de l'industrie de la mémoire de nouvelle génération

-

Samsung Electronics Co., Ltd.

-

SK Hynix Inc.

-

Micron Technology, Inc.

-

Kioxia Holdings Corporation

-

Intel Corporation

- *Avis de non-responsabilité : les principaux acteurs sont triés sans ordre particulier

Développements récents de l'industrie

- Mai 2025 : Samsung a divulgué un jalon 3D NAND 400 couches livrant 5,6 Gb/s par broche, visant les smartphones phares et les blocs et fichiers de serveur de périphérie.

- Avril 2025 : Weebit Nano a obtenu trois brevets supplémentaires pour la technologie de cellule et sélecteur ReRAM, renforçant son portefeuille spécialisé.

- Avril 2025 : SK Hynix a débuté le dispositif HBM4 12 couches, 48 Go, expédiant fin 2025 pour les accélérateurs IA.

- Mars 2025 : Micron a échantillonné la DDR5 1γ avec des étapes EUV réduites, diminuant l'exposition aux coûts futurs tout en maintenant le leadership de vitesse.

Portée du rapport sur le marché mondial de la mémoire de nouvelle génération

La mémoire de nouvelle génération peut être définie comme une étiquette standard appliquée à une mise à niveau significative du matériel ou du logiciel. Le marché de la mémoire de nouvelle génération a grandi au cours des dernières années en raison de la demande croissante pour des solutions mémoire plus rapides, plus efficaces et plus rentables. Les applications Big Data et intelligence artificielle (IA) stimulent l'innovation dans de nombreuses industries, y compris l'apprentissage automatique.

Le marché de la mémoire de nouvelle génération est segmenté par technologie [non-volatile (mémoire à accès aléatoire magnéto-résistive, RAM ferroélectrique, mémoire à accès aléatoire résistive, 3D Xpoint, nano RAM, et autres technologies non-volatiles) et volatile (cube mémoire hybride, mémoire à large bande passante)], par application (BFSI, électronique grand public, gouvernement, télécommunications, technologie de l'information, et autres applications), et par géographie (Amérique du nord, Europe, Asie-pacifique, Amérique latine, et Moyen-orient et Afrique). Les tailles de marché et prévisions sont fournies en termes de valeur (USD) pour tous les segments ci-dessus.

| Non-volatile | Mémoire à changement de phase (PCM) |

| MRAM à transfert de spin (STT-MRAM) | |

| MRAM à bascule | |

| RAM résistive (ReRAM) | |

| 3D XPoint / Optane | |

| RAM ferroélectrique (FeRAM) | |

| NanoRAM | |

| Volatile | Mémoire à large bande passante (HBM) |

| Cube mémoire hybride (HMC) | |

| DDR5 basse consommation / LPDDR5X |

| DDR / LPDDR |

| PCIe / NVMe |

| SATA |

| Autres (CXL, UCIe) |

| Électronique grand public |

| Stockage d'entreprise et centres de données |

| Électronique automobile et ADAS |

| Automatisation IoT et manufacturière industrielle |

| Aérospatial et défense |

| Soins de santé et dispositifs médicaux |

| Autres (cartes intelligentes, wearables) |

| ≤ 200 mm |

| 300 mm |

| 450 mm |

| Amérique du Nord | États-Unis | |

| Canada | ||

| Mexique | ||

| Amérique du Sud | Brésil | |

| Argentine | ||

| Reste de l'Amérique du Sud | ||

| Europe | Allemagne | |

| Royaume-Uni | ||

| France | ||

| Reste de l'Europe | ||

| Asie-Pacifique | Chine | |

| Japon | ||

| Corée du Sud | ||

| Inde | ||

| Reste de l'Asie-Pacifique | ||

| Moyen-Orient et Afrique | Moyen-Orient | Arabie Saoudite |

| Émirats Arabes Unis | ||

| Turquie | ||

| Reste du Moyen-Orient | ||

| Afrique | Afrique du Sud | |

| Nigeria | ||

| Reste de l'Afrique | ||

| Par technologie | Non-volatile | Mémoire à changement de phase (PCM) | |

| MRAM à transfert de spin (STT-MRAM) | |||

| MRAM à bascule | |||

| RAM résistive (ReRAM) | |||

| 3D XPoint / Optane | |||

| RAM ferroélectrique (FeRAM) | |||

| NanoRAM | |||

| Volatile | Mémoire à large bande passante (HBM) | ||

| Cube mémoire hybride (HMC) | |||

| DDR5 basse consommation / LPDDR5X | |||

| Par interface mémoire | DDR / LPDDR | ||

| PCIe / NVMe | |||

| SATA | |||

| Autres (CXL, UCIe) | |||

| Par dispositif d'utilisation finale | Électronique grand public | ||

| Stockage d'entreprise et centres de données | |||

| Électronique automobile et ADAS | |||

| Automatisation IoT et manufacturière industrielle | |||

| Aérospatial et défense | |||

| Soins de santé et dispositifs médicaux | |||

| Autres (cartes intelligentes, wearables) | |||

| Par taille de wafer | ≤ 200 mm | ||

| 300 mm | |||

| 450 mm | |||

| Par géographie | Amérique du Nord | États-Unis | |

| Canada | |||

| Mexique | |||

| Amérique du Sud | Brésil | ||

| Argentine | |||

| Reste de l'Amérique du Sud | |||

| Europe | Allemagne | ||

| Royaume-Uni | |||

| France | |||

| Reste de l'Europe | |||

| Asie-Pacifique | Chine | ||

| Japon | |||

| Corée du Sud | |||

| Inde | |||

| Reste de l'Asie-Pacifique | |||

| Moyen-Orient et Afrique | Moyen-Orient | Arabie Saoudite | |

| Émirats Arabes Unis | |||

| Turquie | |||

| Reste du Moyen-Orient | |||

| Afrique | Afrique du Sud | ||

| Nigeria | |||

| Reste de l'Afrique | |||

Questions clés répondues dans le rapport

Quelle est la taille actuelle du marché de la mémoire de nouvelle génération ?

La taille du marché de la mémoire de nouvelle génération a atteint 15,10 milliards USD en 2025 et devrait atteindre 45,16 milliards USD d'ici 2030.

Quelle région mène la production mondiale ?

L'Asie-Pacifique a représenté 47,3 % des revenus en 2024, stimulée par les expansions de capacité de Samsung, SK Hynix et TSMC.

Pourquoi HBM est-elle critique pour les charges de travail IA ?

Les grands modèles de langage saturent la bande passante DRAM traditionnelle ; HBM livre un débit multi-téraoctet par seconde, supprimant le goulot d'étranglement de formation.

À quelle vitesse la demande de mémoire automobile croît-elle ?

Les revenus de l'électronique automobile devraient croître à un TCAC de 37,3 % alors que les systèmes ADAS de niveau 4 nécessitent une mémoire instantanée et haute endurance.

Quel rôle CXL et UCIe joueront-elles dans les systèmes futurs ?

Les deux interfaces permettent des architectures désagrégées, basées sur chiplet qui regroupent de grands blocs mémoire, améliorant l'utilisation et la scalabilité.

Dernière mise à jour de la page le: