Monolithic DrMOS Market Size and Share

Monolithic DrMOS Market Analysis by Mordor Intelligence

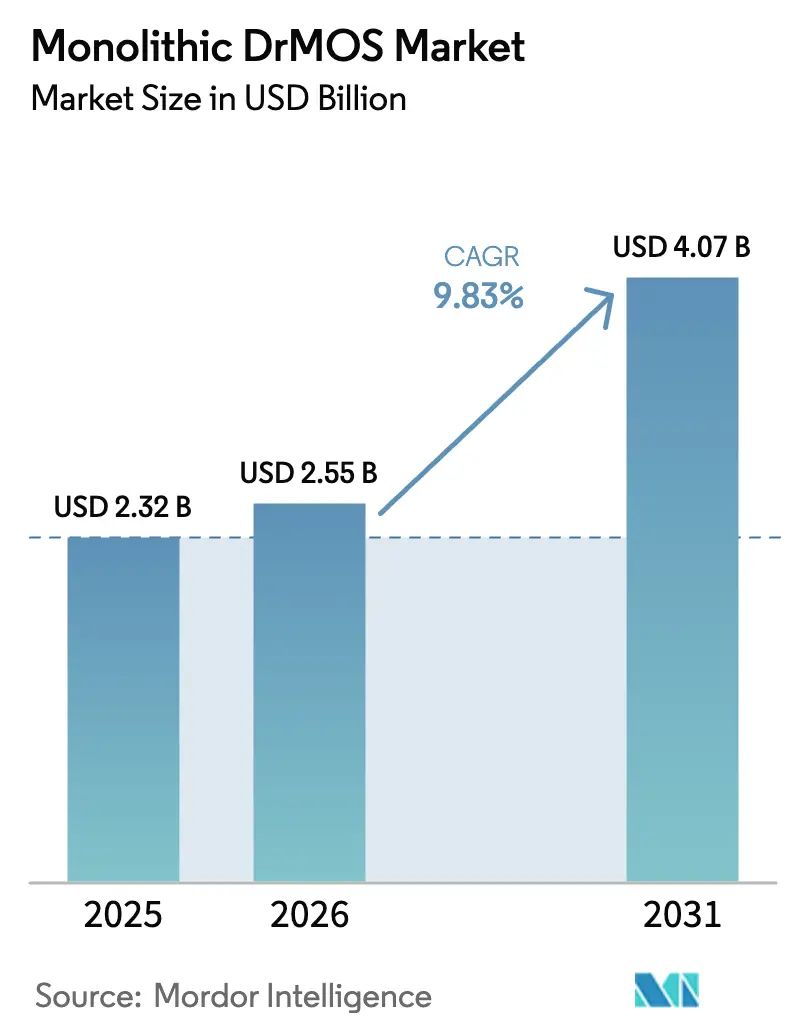

Monolithic DrMOS market size in 2026 is estimated at USD 2.55 billion, growing from 2025 value of USD 2.32 billion with 2031 projections showing USD 4.07 billion, growing at 9.83% CAGR over 2026-2031. This growth reflects the convergence of AI-centric server demand, the transition to 48 V bus architectures in hyperscale data centers, and rising adoption of integrated power stages in electric vehicles and industrial automation. Chipmakers are consolidating driver and MOSFET elements in a single package to improve power density, reduce parasitics, and simplify board layouts for servers, ultrabooks, and automotive powertrains. Monolithic integration is also moving beyond conventional silicon as GaN and SiC options mature, allowing higher voltage operation without compromising efficiency. Geographically, Asia Pacific retains leadership on the back of its semiconductor manufacturing depth and policy incentives, while the Middle East and wider Pacific region is emerging as a high-growth hub thanks to national industrialization programs and renewable-energy investments.

Key Report Takeaways

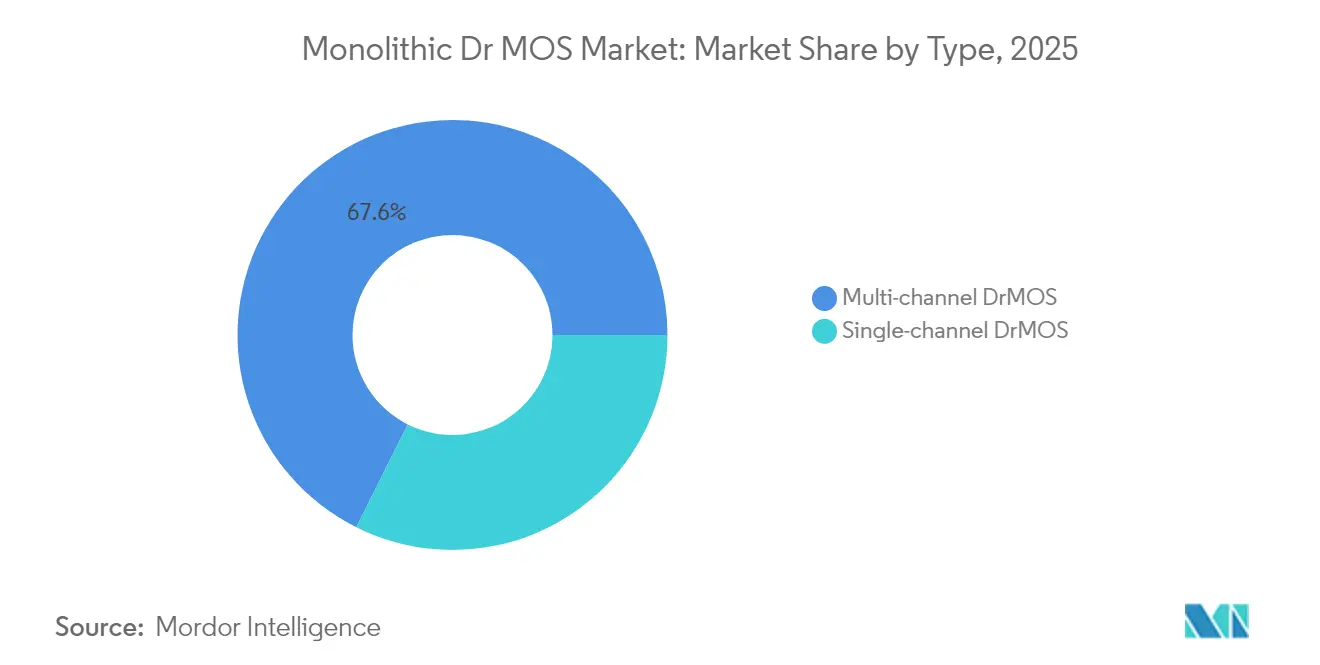

- By type, multi-channel devices led with 67.62% of Monolithic DrMOS market share in 2025; single-channel solutions are forecast to expand at a 9.66% CAGR through 2031.

- By package type, QFN captured 44.55% revenue share in 2025; BGA packages are projected to grow at an 10.82% CAGR to 2031.

- By voltage range, mid-voltage (20-40 V) devices accounted for 56.60% of 2025 sales; >40 V products are advancing at a 11.95% CAGR through 2031.

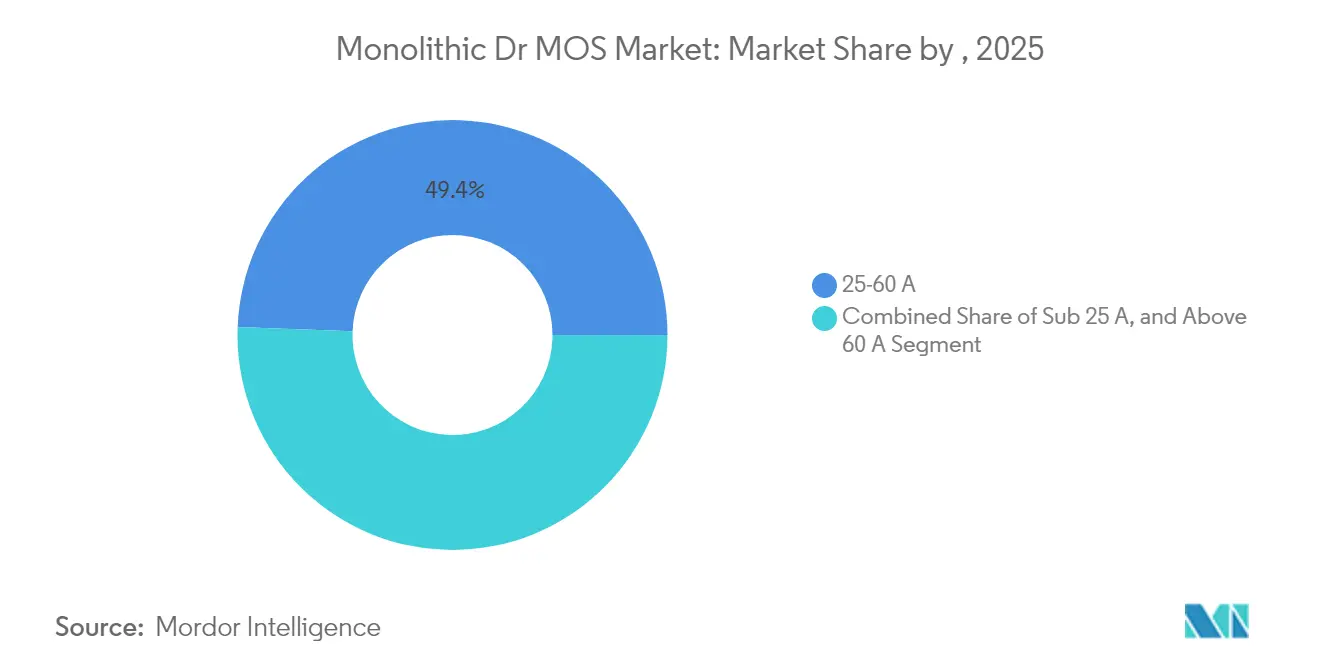

- By current rating, the 25-60 A band commanded 49.40% of revenue in 2025; above-60 A devices are rising at a 12.34% CAGR.

- By end-user, data centers held 31.55% of 2025 revenue, while automotive applications are set to grow at a 13.05% CAGR to 2031.

- Infineon, Onsemi, and Monolithic Power Systems collectively held more than 40% of 2024 revenue, underlining a moderately concentrated supplier base.

Note: Market size and forecast figures in this report are generated using Mordor Intelligence’s proprietary estimation framework, updated with the latest available data and insights as of 2026.

Global Monolithic DrMOS Market Trends and Insights

Drivers Impact Analysis*

| Driver | (~) % Impact on CAGR Forecast | Geographic Relevance | Impact Timeline |

|---|---|---|---|

| Surge in AI-centric server deployments | +3.2% | North America, Asia Pacific | Short term (≤ 2 years) |

| Shift to 48 V bus architecture in hyperscale data centers | +2.8% | Global | Medium term (2-4 years) |

| EV on-board chargers adopting integrated DrMOS | +1.5% | Europe, North America, Asia Pacific | Medium term (2-4 years) |

| Thermal-footprint limits in ultrabooks and gaming laptops | +0.9% | Global | Short term (≤ 2 years) |

| Government incentives for power-efficient industrial automation | +0.7% | Asia Pacific, Middle East | Medium term (2-4 years) |

| Energy-efficiency KPIs for 5 G macro-radio units | +0.6% | Global | Long term (≥ 4 years) |

| Source: Mordor Intelligence | |||

Surge in AI-centric Server Deployments Driving High-Current Adoption

AI servers now feature GPU accelerators that draw up to 1,200 W each, creating a structural need for multi-phase, high-current power stages that maintain tight voltage regulation and reliable thermal performance. Alpha & Omega’s 16-phase AOZ73016QI, designed around NVIDIA OpenVReg16 guidelines, enables scalable configurations up to 48 phases and embeds fine-grained telemetry for transient control.[1]Alpha & Omega Semiconductor, “16-Phase Controller Supports AI Server Innovation,” Alpha & Omega Semiconductor, aosmd.comSuch architectures are driving rapid design-wins in cloud facilities, with system designers valuing granular current sharing, low RDS(on), and package-level thermal optimization that reduce hotspot formation on dense server motherboards.

Rapid Embrace of 48 V Bus Architecture in Hyperscale Data Centres

Migrating from 12 V to 48 V distribution improves rack-level efficiency as server payloads climb past 30 kW. Efficient step-down conversion and tighter dynamic regulation are essential, prompting OEMs to specify DrMOS devices with higher input-voltage tolerance, low switching losses, and advanced packaging that minimizes loop inductance. Implementations such as Infineon’s collaboration on 800 V centralized power schemes show the roadmap toward even higher bus voltages, placing additional emphasis on thermal robustness and overload protection in integrated power modules.[2] Infineon Technologies, “CoolGaN Power Solutions,” Infineon Technologies, infineon.com

EV On-board Chargers Shifting from Discrete MOSFETs to Integrated DrMOS

Automotive OEMs are replacing discrete topologies with integrated stages to boost power density, shorten routings, and cut EMI. SiC-based DrMOS variants enable higher switching frequencies, allowing smaller magnetics and lighter systems-key to extending vehicle range.[3]ROHM Semiconductor, “PMICs Adopted in Telechips Reference Designs,” ROHM Semiconductor, rohm.comPackages qualified to AEC-Q101 withstand wide temperature swings and mechanical stress, positioning integrated power stages as critical building blocks in the next generation of 800 V EV architectures and bidirectional charging systems.

Thermal-Footprint Constraints in Ultrabooks & Gaming Laptops

Thinner chassis leave less airflow, forcing power regulators to operate efficiently under higher temperature gradients. DrMOS products featuring copper lead-frames, optimized gate drivers, and embedded thermal monitoring limit self-heating, enabling processors to sustain Turbo frequencies longer. Designs like Vishay’s SiC639 reach 93% efficiency at 1 V / 40 A outputs, translating into 3 °C-15 °C lower package temperatures compared with earlier discrete stages, thereby supporting slimmer heatsink options.[4]Monolithic Power Systems, “Investor Day 2025 Presentation,” Monolithic Power Systems, monolithicpower.com

Restraints Impact Analysis*

| Restraint | (~) % Impact on CAGR Forecast | Geographic Relevance | Impact Timeline |

|---|---|---|---|

| Yield-loss sensitivity in wafer-level packaging | −0.8% | Global | Medium term (2-4 years) |

| Limited automotive AEC-Q101 qualification > 40 V | −0.5% | Global | Short term (≤ 2 years) |

| IP litigation risk around driver topologies | −0.3% | North America, Europe | Medium term (2-4 years) |

| Vendor lock-in concerns among Tier-1 server OEMs | −0.2% | Global | Long term (≥ 4 years) |

| Source: Mordor Intelligence | |||

Yield-loss Sensitivity in Wafer-Level Packaging for High-Current Devices

Integrating multiple dice for >60 A ratings elevates defect risk at solder-ball and redistribution-layer interfaces. Heterogeneous Integration Roadmap data underscore how parasitic resistance rises sharply when alignment tolerances slip, eroding efficiency and raising junction temperatures. GaN-on-Si or SiC-on-Si stacks compound complexity, pushing fabs to adopt new under-fill resins and copper clip designs to stabilize yield. Resulting cost premiums may deter adoption in price-sensitive consumer segments until processes mature.

Limited Automotive AEC-Q101 Qualification at > 40 V Ranges

High-voltage, integrated stages still face extended validation cycles to meet automotive reliability demands. Scarcity of fully qualified options above 40 V slows deployment in traction inverters and 48 V mild-hybrid subsystems. Suppliers are expanding thermal cycle testing, humidity bias stress, and high-temperature reverse-bias screening to shorten qualification timelines, yet design-win conversions remain gated by conservative automotive approval processes.

*Our updated forecasts treat driver/restraint impacts as directional, not additive. The revised impact forecasts reflect baseline growth, mix effects, and variable interactions.

Segment Analysis

By Type: Multi-channel Integration Drives Efficiency

Multi-channel devices generated 67.62% of 2025 revenue, cementing their role as the default building block for high-current VRMs in data-center and graphics workloads. The Monolithic DrMOS market size for multi-channel implementations is set to expand at a sturdy pace as GPU clusters move to 48-phase topologies that demand synchronized control and current balancing. Engineers favor these solutions because shared drivers and tightly coupled power FETs lower loop inductance and improve transient response by up to 30% versus discrete configurations.

Single-channel variants captured the remaining share yet show 9.66% CAGR momentum. Lower cost, compact footprints, and simpler layout make them attractive for portable devices, Wi-Fi routers, and IoT gateways. Continued enhancements-zero-current detection, adjustable dead-time, and adaptive voltage positioning-are narrowing the efficiency delta with larger devices, enabling designers to use a single power stage across multiple boards and shorten qualification efforts.

By Package Type: BGA Advances Thermal Management

QFN packages maintained a 44.55% slice of 2025 revenue due to their balanced cost–performance profile. Embedded exposed pads conduct heat into multilayer PCBs, supporting continuous currents up to 60 A without external heatsinks. The Monolithic DrMOS market benefits from this mature format because contract assemblers globally have optimized reflow windows and inspection routines around QFN footprints.

BGA and LGA packages are rising at an 10.82% CAGR, addressing higher current density and higher frequency demands. Their arrayed solder joints slash loop inductance and distribute heat into the board more evenly, letting stages push beyond 100 A per phase in AI accelerators. Device makers are integrating copper pillars, sintered silver die attach, and direct-top-side cooling lids to further boost thermal capability, opening doors for >1 kW board-level converters.

By Voltage Range: Mid-Voltage Versatility Dominates

Devices rated 20-40 V delivered 56.60% of 2025 sales, reflecting the sweet spot for industrial controls, telecom boards, and VRMs on client PCs. This segment of the Monolithic DrMOS market size is expected to grow steadily as 24 V factory automation systems proliferate. Optimized silicon FOM and tighter gate drives yield efficiency above 94% at typical 12 V-in to 1.8 V-out conversions, keeping regulators cool even in sealed enclosures.

The >40 V tier records the highest 11.95% CAGR through 2031. Data-center operators upgrading to 48 V backplanes and EV charging networks adding 800 V platforms require integrated stages that tolerate higher transients while minimizing conduction losses. Combining wider-bandgap FETs with CMOS drivers inside one enclosure curbs switching losses and shrinks magnetic components, making these devices competitive with discrete SiC modules in tight spaces.

By Current Rating: Mid-Range Powers Computing Surge

The 25-60 A category held 49.40% of 2025 shipments. Well-proven silicon, careful gate-charge tuning, and advanced copper lead-frames give these stages a solid balance of efficiency and cost for CPUs, DIMMs, and storage controllers. The Monolithic DrMOS market share for this band remains secure as motherboard makers standardize around dual- and tri-phase groupings, producing predictable thermal patterns that simplify airflow design.

Above-60 A stages show a brisk 12.34% CAGR. AI cards and top-tier GPUs frequently draw >600 A across multiple phases, encouraging designers to parallel several 90 A-capable modules. Suppliers are leveraging thicker copper clip bonds, top-side cooling lids, and lower RDS(on) GaN dies to achieve <1 mΩ conduction paths, ensuring voltage droop stays within ±2 %. Firmware-driven active balancing now enables finer current sharing without external amplifiers, supporting future 120 A single-package options.

By End-user Industry: Data Centers Lead AI Power Revolution

Data-center and high-performance computing customers commanded 31.55% of 2025 revenue. Hyperscale operators are aggressively replacing discrete stages with integrated options to cut board space, reduce distribution losses, and boost rack-level power density. The segment’s double-digit outlay growth sustains robust volumes for 25-60 A and >60 A modules alike, underpinning the wider Monolithic DrMOS market.

Automotive demand, posting a 13.05% CAGR, reflects electrified powertrains’ rising voltage and current requirements. Integrated stages simplify charger, DC-DC, and auxiliary domain designs while meeting ISO 26262 and AEC-Q101 criteria. Consumer electronics continues to absorb large unit volumes in smartphones and tablets, where single-channel stages preserve battery life and screen real estate. Industrial automation demand is also rising as incentive programs in Asia support energy-efficient machinery, amplifying consumption of 20-40 V products.

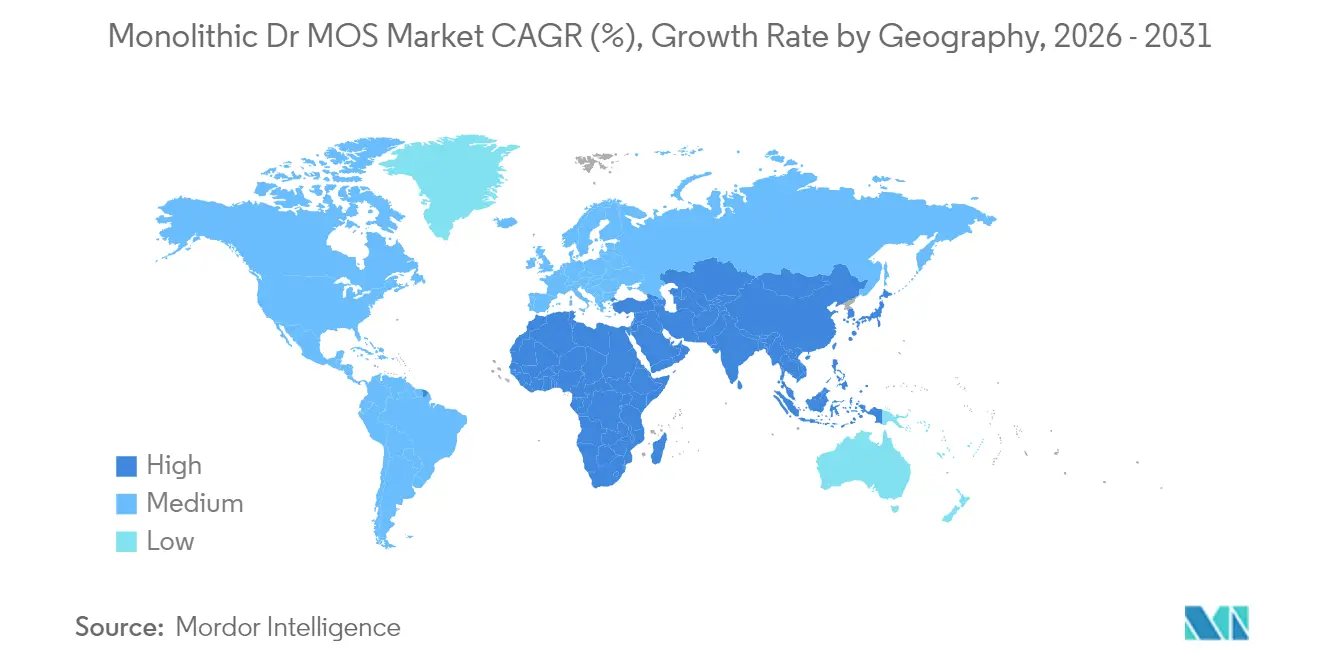

Geography Analysis

Asia Pacific retained a commanding 54.55% of 2025 shipments, leveraging deep foundry capacity, established OSAT partners, and state-backed incentives for smart-factory upgrades. China, Taiwan, and South Korea host extensive backend facilities that enable cost-competitive supply of high-current devices. Domestic initiatives that subsidize 300 mm power fabs and promote wide-bandgap R&D further reinforce the regional pole position. OEM proximity lets suppliers iterate quickly on custom pin-outs and package outlines tailored to local server and notebook brands.

North America continues as the second-largest buyer, anchored by cloud giants expanding GPU clusters and 48 V power shelves. Federal incentives to reshore advanced chip fabrication are prompting investments into wafer, epitaxy, and substrate production that will improve long-term supply resilience for the Monolithic DrMOS market. Europe combines a robust EV ecosystem with strong industrial automation heritage, sustaining demand for automotive-qualified and 24 V factory-control modules.

The Middle East and Pacific grouping is the fastest-growing region at an 10.72% CAGR. Saudi Arabia’s Alat program and related semiconductor hubs have earmarked multi-billion-dollar budgets to localize power-device assembly and leverage renewable-powered sites, creating new customer bases for integrated power stages within power-electronics clusters. South America and Africa remain emerging markets where telecom upgrades and solar mini-grids gradually lift consumption of mid-voltage DrMOS devices.

Competitive Landscape

The Monolithic DrMOS market is moderately concentrated. Infineon, Onsemi, and Monolithic Power Systems leverage end-to-end silicon, packaging, and module assembly to secure around 40% of global revenue. Their vertical integration enables rapid transition to copper clip, BGA, and hybrid GaN processes while protecting supply against wafer shortages. Alpha & Omega Semiconductor and ROHM gain share through focus on high-voltage SiC and automotive-grade portfolios. Packaging specialists are now partnering with controller vendors to co-design pin-outs that maximize current density without exceeding PCB layer budgets.

Material innovation is an emerging battleground. Infineon’s CoolGaN topology and Intel’s DrGaN proof-of-concept demonstrate how GaN-on-Si stacks can deliver higher switching frequencies with lower charging currents, shrinking magnetic footprints in VRMs. Patent filings tied to driver circuitry, shoot-through avoidance, and integrated telemetry illustrate rising IP stakes. At the same time, hyperscale customers push for multi-sourcing strategies to avoid vendor lock-in, compelling suppliers to open datasheets and align on pin-compatible footprints to facilitate second-source qualifications.

Monolithic DrMOS Industry Leaders

-

Analog Devices, Inc.

-

Vishay Intertechnology Inc.

-

Infineon Technologies AG

-

ON Semiconductor Corporation (Onsemi)

-

Monolithic Power Systems, Inc.

- *Disclaimer: Major Players sorted in no particular order

Recent Industry Developments

- May 2025: Alpha & Omega Semiconductor rolled out the AOZ98252QI dual-output 8-phase controller for AMD AM5 desktops and Navi44/48 graphics cards, adding transient modulation and low quiescent power.

- April 2025: Alpha & Omega Semiconductor secured USD 100 million to expand SiC capacity and acquired SiCure Technologies, broadening its ≥650 V portfolio for EV and energy systems.

- March 2025: Monolithic Power Systems’ Investor Day disclosed 24.9% average annual revenue growth from 2018-2024 and a target to outpace the Monolithic DrMOS market by 10-15 % annually through diversified R&D.

- January 2025: Alpha & Omega Semiconductor introduced the AOZ73016QI 16-phase controller tested against NVIDIA OpenVReg16 requirements, enabling 48-phase VRMs without external add-ons.

- December 2024: ROHM’s power-management ICs, including automotive-grade DrMOS, were selected for Telechips Dolphin3 and Dolphin5 cockpit SoCs, with mass production slated for 2025.

Research Methodology Framework and Report Scope

Market Definitions and Key Coverage

Our study defines the monolithic DrMOS market as global sales revenue from single-package power stages in which the low-side MOSFET, high-side MOSFET, and gate driver are co-fabricated or co-packaged, enabling high-density, low-loss power delivery in servers, notebooks, EV on-board chargers, and industrial controllers.

Scope Exclusion: Solutions that house discrete MOSFETs and external drivers or act only as GaN/SiC half-bridges were left outside our sizing universe.

Segmentation Overview

-

By Type

- Single-channel DrMOS

- Multi-channel DrMOS

-

By Package Type

- BGA

- QFN

- DFN

- LGA

-

By Voltage Range

- Less Than 20 V (Low)

- 20-40 V (Mid)

- Above 40 V (High)

-

By Current Rating

- Up to 25 A

- 25-60 A

- Above 60 A

-

By End-user Industry

- Consumer Electronics

- Data Centres and HPC

- Automotive

- Industrial Automation

- Telecommunications (5 G and Networking)

- Others

-

By Geography

- North America

- Europe

- Asia-Pacific

- South America

- Middle East

- Africa

Detailed Research Methodology and Data Validation

Primary Research

Mordor analysts held structured calls with power-stage designers in the United States, Taiwan, Germany, and Israel, along with procurement leads at notebook ODMs and EV charger integrators. The conversations verified mid-current ASP progression, 48 V platform penetration, and expected wafer-level yield shifts that were unclear in public filings.

Desk Research

We began by mining open datasets issued by bodies such as JEDEC, IPC, and the International Energy Agency, which track package standards, board shipments, and electrification trends. Customs trade tables, chip import logs on Volza, and quarterly sales reported in SEC 10-Ks supplied baseline unit flows. Patent families pulled through Questel and design-win news compiled via Dow Jones Factiva helped us map emerging voltage classes. Company presentations, trade journals, and association papers from IPC and OCP provided typical ASPs. These sources illustrate the evidence trail; many more public and paid references supported data validation throughout the build.

Market-Sizing & Forecasting

We applied a top-down construct that converts motherboard, server, and EV charger production into DrMOS attachable sockets, which are then multiplied by verified penetration rates and calibrated ASPs. Supplier roll-ups and channel checks offered bottom-up reference points, letting us adjust totals where attach rates over or under shot real shipments. Key variables in our model include: server shipment growth, 48 V bus adoption ratio, notebook thickness road maps, average wafer yield loss, typical ASP drift, and regional EV charger installs. A multivariate regression blended with three-scenario analysis projects each driver through 2030, with gap filling for sparse segments guided by weighted regional proxies.

Data Validation & Update Cycle

Outputs pass variance scans versus independent indicators and are peer-reviewed twice. Reports refresh every year, while any material event, such as a new substrate plant ramp, triggers an interim revisit so clients receive our latest view.

Why Mordor's Monolithic DrMOS Baseline Numbers Inspire Confidence

Published figures often diverge because firms pick different device mixes, forecast cadences, and currency bases. We flag these factors upfront so buyers know exactly what sits inside our basket.

Key gaps arise when other publishers fold discrete modules into totals, apply flat ASP curves, or freeze attach-rate assumptions for five years. Our model updates socket counts quarterly, layers region-specific ASP erosion, and excludes non-integrated power stages, which explains most variance.

Benchmark comparison

| Market Size | Anonymized source | Primary gap driver |

|---|---|---|

| USD 2.32 B (2025) | Mordor Intelligence | - |

| USD 2.85 B (2024) | Global Consultancy A | Bundles discrete DrMOS and monolithic devices, no attach-rate refresh |

| USD 2.10 B (2024) | Trade Journal B | Uses uniform ASPs across current ranges, limited primary validation |

| USD 0.189 B (2023) | Regional Association C | Covers only <50 A segments sold through distributors |

The comparison shows how scope breadth, ASP handling, and update cadence drive headline gaps. By grounding each lever in openly traceable variables and fresh expert input, Mordor delivers a balanced baseline decision-makers can trust.

Key Questions Answered in the Report

What is driving the rapid growth of the Monolithic DrMOS market?

Efficient power delivery for AI servers, adoption of 48 V architectures in data centers, and the shift to integrated power stages in electric vehicles collectively fuel a 9.83% CAGR over 2026-2031.

Which segment currently dominates the Monolithic DrMOS market size?

Multi-channel devices dominate with 67.62% revenue share in 2025, owing to their suitability for high-current, multi-phase VRMs in servers and graphics cards.

How are GaN and SiC devices influencing the Monolithic DrMOS industry?

Wider-bandgap materials enable higher switching frequencies and voltage ratings, allowing integrated stages to serve 48 V racks and 800 V EV systems more efficiently than traditional silicon designs.

Why is Asia Pacific the leading region for Monolithic DrMOS market growth?

The region hosts extensive wafer fabrication and advanced packaging capacity, benefits from government incentives, and supplies a large domestic demand base across data-center, automotive, and consumer sectors.

What packaging trend is most important for next-generation DrMOS devices?

BGA and LGA formats are gaining prominence because their 3-D interconnects cut inductance and spread heat, enabling >100 A power stages needed for high-performance computing and AI accelerators.

Page last updated on: