Taille et parts du marché de la technologie basculer chip

Analyse du marché de la technologie basculer chip par Mordor Intelligence

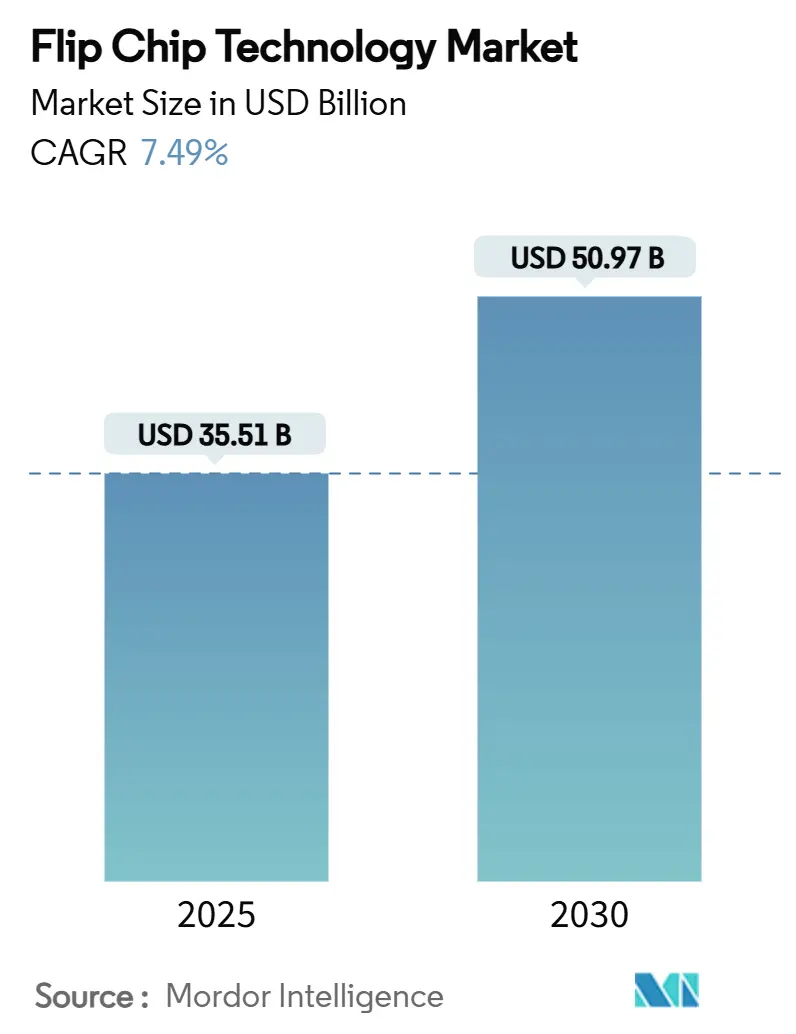

La taille du marché de la technologie basculer chip s'élevait à 35,51 milliards USD en 2025 et est en voie d'atteindre 50,97 milliards USD d'ici 2030, reflétant un TCAC de 7,49 %. La croissance un reflété la transition de l'industrie des semi-conducteurs vers les architectures basées sur les chiplets qui nécessitaient des interconnexions denses et thermiquement efficaces. Les déploiements de centres de données IA ont mis au premier plan l'emballage de mémoire à haute bande passante, tandis que les lignes de pilliers de cuivre et de liaison hybride ont répondu aux besoins de pas fins que les bumps de soudure traditionnels ne pouvaient pas satisfaire. Les fonderies sont entrées dans l'arène de l'emballage, accélérant l'intégration verticale et apportant de nouvelles pressions concurrentielles sur les fournisseurs d'assemblage et de test externalisés. L'Asie-Pacifique un conservé des avantages d'échelle, mais les programmes de réduction des risques de chaîne d'approvisionnement en Amérique du Nord et en Europe ont déclenché de gros investissements dans de nouvelles installations d'emballage avancé.

Points clés du rapport

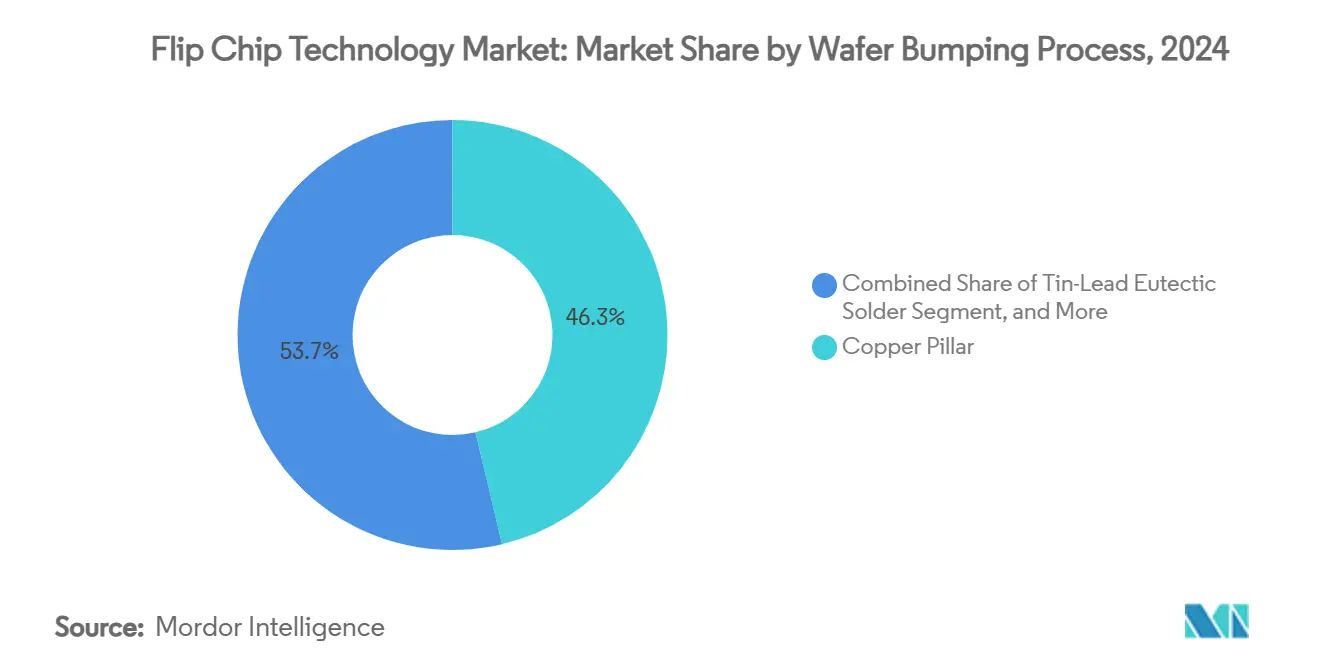

- Par processus de bumping de wafer, le pilier de cuivre détenait 46,3 % des parts de revenus en 2024, tandis que la liaison hybride Cu-to-Cu devrait croître à un TCAC de 9,8 % jusqu'en 2030.

- Par technologie d'emballage, FC-BGA menait avec 38,1 % de parts en 2024, tandis que les solutions fan-out WLP/panel-level devraient croître à un TCAC de 10,1 % jusqu'en 2030.

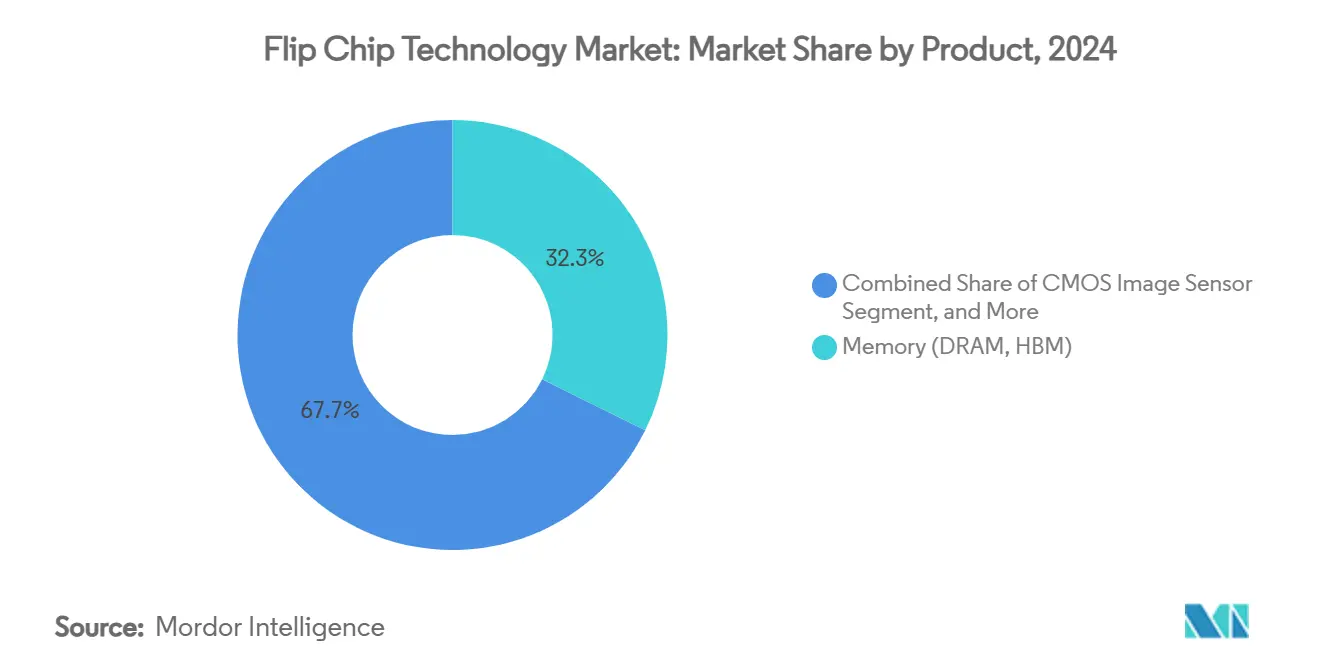

- Par produit, la mémoire représentait 32,3 % des parts du marché de la technologie basculer chip en 2024, tandis que le segment GPU/accélérateur IA devrait progresser à un TCAC de 12,9 % jusqu'en 2030.

- Par industrie d'utilisation finale, l'électronique grand public et les objets connectés détenaient une part de 29,4 % en 2024, tandis que les applications de centres de données et cloud devraient enregistrer un TCAC de 9,1 % jusqu'en 2030.

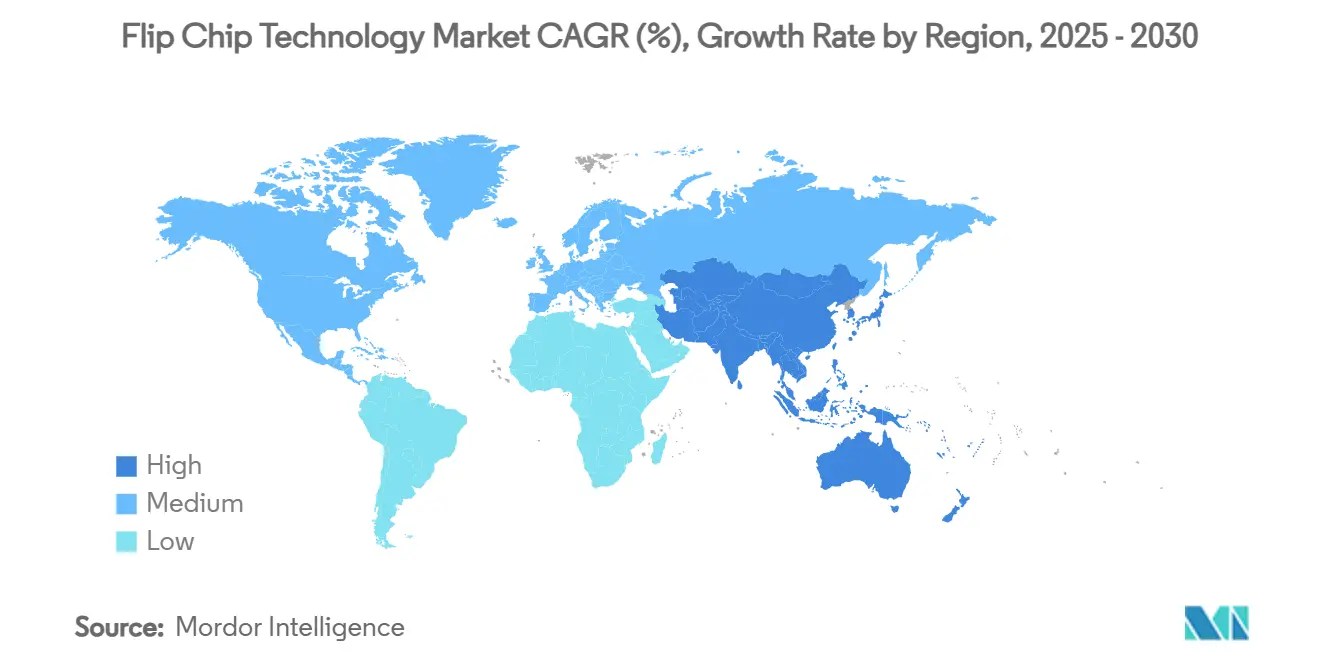

- Par géographie, l'Asie-Pacifique un capturé 54,5 % des revenus de 2024 et devrait afficher un TCAC de 9,5 % jusqu'en 2030.

Tendances et perspectives du marché mondial de la technologie basculer chip

Analyse d'impact des moteurs

| Moteur | (~) % Impact sur les prévisions TCAC | Pertinence géographique | Calendrier d'impact |

|---|---|---|---|

| Montée de la demande d'intégration hétérogène (IA/HPC) | +2.1% | Mondial, concentré en Amérique du Nord et Asie-Pacifique | Moyen terme (2-4 ans) |

| Adoption croissante des interconnexions pilier de cuivre et micro-bump | +1.8% | Noyau Asie-Pacifique, s'étendant à l'Amérique du Nord et l'Europe | Court terme (≤ 2 ans) |

| Poussée de miniaturisation des objets connectés et IoT | +1.2% | Mondial, avec adoption précoce en Asie-Pacifique et Amérique du Nord | Long terme (≥ 4 ans) |

| Exigences de fiabilité ADAS/VE automobile | +1.0% | Mondial, mené par l'Europe et l'Amérique du Nord | Moyen terme (2-4 ans) |

| Essais commerciaux de substrat à noyau de verre | +0.9% | Amérique du Nord et Asie-Pacifique, programmes pilotes en Europe | Long terme (≥ 4 ans) |

| Demande de liaison hybride Cu-to-Cu prête pour les chiplets | +0.8% | Noyau Asie-Pacifique, expansion mondiale | Moyen terme (2-4 ans) |

| Source: Mordor Intelligence | |||

Montée de la demande d'intégration hétérogène (IA/HPC)

Les fabricants de puces ont pivoté de la mise à l'échelle 2D vers l'intégration hétérogène qui joint plusieurs chiplets dans un seul package, augmentant la demande pour des interconnexions Cu-to-Cu à pas fin.[1]Applied Matériaux, "Hybrid Bonding," appliedmaterials.com Le plan de TSMC d'augmenter la capacité CoWoS à 1,31 million d'unités d'ici 2026 un illustré comment les fournisseurs de GPU tels que Nvidia ont façonné le marché de la technologie basculer chip. L'approche un amélioré la bande passante tout en réduisant la consommation par rapport aux bumps hérités, soutenant la feuille de route de performance pour les accélérateurs IA.

Adoption croissante des interconnexions pilier de cuivre et micro-bump

Les bumps pilier de cuivre ont fourni une résistance électrique et une fiabilité supérieures, expliquant leurs 46,3 % de parts de revenus en 2024. Les chimies de placage haute vitesse de DuPont ont fourni un contrôle d'uniformité d'épaisseur essentiel pour les pas sub-40 µm. Le changement un érodé la dominance de l'étain-plomb et un ouvert la voie aux schémas d'intégration 3D qui sous-tendent le marché de la technologie basculer chip.

Poussée de miniaturisation des objets connectés et IoT

Les méthodes system-in-package et wafer-level chip-scale sont devenues des incontournables pour les montres intelligentes et les trackers de santé qui exigeaient des profils minces sans sacrifier la durée de vie de la batterie. Les avancées PCB ultra-HDI utilisant le traitement semi-additif modifié et l'imagerie directe laser ont offert des largeurs de traces inférieures à 40 µm, permettant des modules de capteurs compacts.

Exigences de fiabilité ADAS/VE automobile

La conduite autonome et l'électrification du groupe motopropulseur nécessitent des packages qui survivent à des températures supérieures à 200 °C. Les lignes basculer chip de qualité automobile ont employé des underfills haute température et des joints pilier de cuivre qualifiés pour AEC-Q100 Grade 0. Le chiffre d'affaires électronique automobile de JCET s'est développé à plus de 50 % TCAC entre 2019 et 2023, signalant une adoption rapide de ces processus robustes.

Analyse d'impact des contraintes

| Contrainte | (~) % Impact sur les prévisions TCAC | Pertinence géographique | Calendrier d'impact |

|---|---|---|---|

| Haute intensité capitalistique des lignes de bumping avancées | -1.4% | Mondial, plus prononcé en Amérique du Nord et Europe | Court terme (≤ 2 ans) |

| Défis de fiabilité et de gauchissement sans plomb | -0.9% | Mondial, pression réglementaire plus forte en Europe | Moyen terme (2-4 ans) |

| Pertes de rendement d'alignement sub-10 µm | -0.7% | Noyau Asie-Pacifique, s'étendant aux fabs avancées mondiales | Court terme (≤ 2 ans) |

| Exposition de la chaîne d'approvisionnement aux produits chimiques métalliques critiques | -0.5% | Mondial, risque concentré en Amérique du Nord et Asie-Pacifique | Moyen terme (2-4 ans) |

| Source: Mordor Intelligence | |||

Haute intensité capitalistique des lignes de bumping avancées

La mise à l'échelle vers des pas sub-10 µm un nécessité des steppers de lithographie, des outils de pulvérisation avancés et des nettoyeurs plasma qui ont poussé le coût des lignes au-dessus de 250 millions USD par module. TSMC un alloué 90 milliards USD pour des usines d'emballage dédiées, soulignant l'obstacle d'entrée pour les petits concurrents. Les programmes de R&D collaboratifs tels que la participation de 3M au consortium US-JOINT visaient à répartir les risques à travers la chaîne d'approvisionnement.

Défis de fiabilité et de gauchissement sans plomb

Les mandats RoHS ont accéléré l'adoption du SnAgCu, mais l'expansion thermique différentielle un introduit le gauchissement et la fatigue de soudure dans les piles basculer chip. Les études ont montré que les joints Sn-Bi eutectiques ont prolongé la durée de vie du cyclage thermique mais ont souffert de fragilité qui un limité les applications haute contrainte. Le reflux basse température à 175 °C un réduit les défauts head-on-pillow mais un nécessité des alliages à base de bismuth qui ont compliqué l'assemblage gros volume.

Analyse par segment

Par processus de bumping de wafer : la dominance du cuivre stimule l'innovation

La technologie pilier de cuivre détenait 46,3 % des revenus en 2024 au sein du marché de la technologie basculer chip. Le segment un bénéficié de la résistance réduite et de la capacité de transport de courant renforcée. La taille du marché de la technologie basculer chip pour la liaison hybride Cu-to-Cu devrait croître à un TCAC de 9,8 % avec l'adoption des chiplets. La méthode hybride un abaissé l'espacement inter-puces à 0,8 µm, bien au-delà des limites physiques de la soudure.[2]IBM Research, "Hybrid Bonding for emballage puces," research.ibm.com Les solutions étain-plomb servaient encore les nœuds hérités, tandis que les bumps gold-stud restaient confinés à l'unérospatiale.

Les avancées dans les chimies électroplaquées ont maintenu l'uniformité de hauteur des pilliers en dessous de 2 %, un prérequis pour les piles 3D. La recherche IEEE un validé la liaison Cu-Cu sans soudure à 260 °C comme une voie manufacturable pour l'intégration hétérogène. Les innovations ont positionné les formats cuivre pour absorber les parts des alternatives sans plomb et métaux précieux.

Note: Parts de segments de tous les segments individuels disponibles à l'achat du rapport

Par technologie d'emballage : les architectures avancées redessinent la dynamique du marché

FC-BGA commandait 38,1 % des revenus de 2024 grâce à la fiabilité prouvée dans les serveurs. Les formats fan-out WLP et panel-level devraient enregistrer un TCAC de 10,1 %, catalysés par les accélérateurs IA exigeant de grandes tailles de corps. ASE un alloué 200 millions USD aux panneaux 310 mm × 310 mm qui promettent une zone utilisable sept fois supérieure aux wafers, une percée de coût. La taille du marché de la technologie basculer chip pour les packages panel-level grimpera avec l'amélioration des rendements des lignes.

Les flux spécialisés tels que CoWoS et EMIB permettent l'empilement HBM essentiel pour les unités d'entraînement IA. IBM et Intel ont poursuivi des feuilles de route de substrat de verre qui offrent un gauchissement plus faible et des ratios ligne-espace plus élevés que les laminés organiques. La 3D IC avec TSV est restée une niche pour les dispositifs de classe bande passante extrême en raison du coût élevé et de la complexité de processus, mais un fixé le plafond sur les performances atteignables.

Par produit : la mémoire et les accélérateurs IA mènent la croissance

La mémoire détenait une part de 32,3 % en 2024 avec l'envolée de l'adoption HBM. Applied Matériaux un estimé une croissance six fois supérieure des revenus d'emballage HBM, portée par 19 étapes de processus supplémentaires versus la DRAM conventionnelle. Les GPU/accélérateurs IA afficheront un TCAC de 12,9 % jusqu'en 2030. Le marché de la technologie basculer chip s'est rapidement adapté pour combiner plusieurs piles HBM avec des nœuds logiques à travers des interposeurs, créant des densités de puissance de package dépassant 1 kW.

Les capteurs d'image CMOS ont maintenu leur élan sur le dos des smartphones multi-caméras, tandis que les dies micro-LED ont nécessité un bumping sub-20 µm qui s'accordait avec les capacités pilier de cuivre. La ligne italienne de 3,5 milliards USD de Silicon Box ciblant les solutions chiplet un illustré l'investissement régional dans les synergies inter-produits.

Note: Parts de segments de tous les segments individuels disponibles à l'achat du rapport

Par industrie d'utilisation finale : les centres de données stimulent la transformation

L'électronique grand public un conservé une part de 29,4 % mais un ralenti avec la stagnation des volumes de combinés. La demande de centres de données et cloud croîtra à un TCAC de 9,1 % car les nœuds d'inférence IA déploient des chiplets haute bande passante en volume. La taille du marché de la technologie basculer chip pour les applications de centres de données devrait s'élargir rapidement avec l'adoption par les serveurs de configurations quatre et huit HBM.

L'électronique automobile un tiré parti des joints pilier de cuivre moulés avec des underfills haute transition vitreuse pour répondre aux oscillations de température Grade 0. Les implants médicaux ont bénéficié de packages wafer-level biocompatibles qui intégraient la télémétrie sans fil tout en gardant la taille d'enveloppe minimale.[3]Emerald, "Miniature Electronic Modules for Advanced Health Care," emerald.comLes télécommunications ont déployé des radios 5G millimètriques qui nécessitaient des interconnexions faible perte compatibles avec les bumps Cu-pillar.

Analyse géographique

L'Asie-Pacifique détenait 54,5 % des revenus de 2024. La région abritait la majeure partie des fabs de wafer et conservait des avantages de coût, maintenant la plus grande tranche du marché de la technologie basculer chip. Les incitations gouvernementales ont soutenu la R&D des nœuds suivants, mais les actions de contrôle à l'exportation ont incité les entreprises leaders à construire une capacité parallèle à l'étranger. L'Amérique du Nord un accéléré les startups de fonderie et d'emballage sous le puces Act, ajoutant de la résilience et créant une attraction de demande locale. La part du marché de la technologie basculer chip pour l'Amérique du Nord devrait augmenter modestement avec la mise en ligne des campus d'Arizona et du Texas.

L'Europe un poursuivi la souveraineté technologique à travers le European puces Act et un dirigé le capital vers les lignes panel-level et substrat noyau de verre. L'installation de Novara de Silicon Box est prévue pour traiter 10 000 panneaux hebdomadaires d'ici 2028, ancrant un écosystème régional. Le Moyen-Orient et l'Afrique sont restés au stade précoce mais ont bénéficié des hubs d'assemblage final électronique qui alimentent les chaînes d'approvisionnement mondiales.

La diversification de la chaîne d'approvisionnement un dispersé les futurs investissements sur au moins trois continents, atténuant la dominance d'une seule région. Cependant, l'Asie-Pacifique possédait encore une profondeur d'ingénierie inégalée, la maintenant comme centre de référence pour la fabrication gros volume.

Paysage concurrentiel

L'intégration verticale des fonderies un remodelé la rivalité. TSMC un combiné la production de wafer avec les services back-end CoWoS, raccourcissant le temps de cycle client. ASE un répondu avec des constructions panel-level et des qualifications auto-grade pour sauvegarder la part. Intel est sorti de la R&D interne de substrat de verre et s'est associé avec des fournisseurs spécialisés, validant l'obstacle de complexité pour les nouveaux entrants.[4]TechPowerUp, "Intel Abandons In-House Glass Substrate R&D," techpowerup.com

Les brevets de liaison hybride ont créé des fossés défendables. IBM un réduit l'espacement inter-puces à 0,8 µm, permettant des gains de bande passante dramatiques. Les fournisseurs de matériaux tels que DuPont et 3M font progresser les chimies pour le placage de pilier et les films diélectriques faible gauchissement, s'intégrant plus profondément dans la chaîne de valeur. Les OSAT chinois ont étendu la capacité avec des usines multi-milliardaires, mais la parité technologique avec les nœuds leaders est restée une cible mouvante.

Les leaders du marché sont de plus en plus différenciés par la préparation aux nœuds avancés plutôt que par le nombre total de bumps. Le changement un accentué la pression de consolidation sur les acteurs de niveau intermédiaire manquant de capital pour upgrader les lignes sub-10 µm, catalysant les fusions visant à mutualiser la R&D et les bases clients.

Leaders de l'industrie de la technologie basculer chip

-

Amkor Technology Inc.

-

UTAC Holdings Ltd

-

Taiwan Semiconductor Manufacturing Co. (TSMC)

-

Chipbond Technology Corporation

-

TF-AMD Microlectronics Sdn Bhd.

- *Avis de non-responsabilité : les principaux acteurs sont triés sans ordre particulier

Développements récents de l'industrie

- Juillet 2025 : TSMC un réorganisé son projet de 65 milliards USD en Arizona pour traiter les dépassements de coûts tout en conservant les modules d'emballage avancé.

- Mai 2025 : TSMC un exposé 42 milliards USD en dépenses d'investissement 2025 couvrant huit fabs de wafer et une usine d'emballage.

- Avril 2025 : TSMC un annoncé une expansion de NT$1,5 trillion (45,2 milliards USD) à Kaohsiung axée sur la capacité de wafer 2 nm et d'emballage avancé.

- Février 2025 : 3M un rejoint le consortium US-JOINT, ouvrant un laboratoire Silicon Valley pour co-développer les matériaux d'emballage avancé.

Portée du rapport mondial du marché de la technologie basculer chip

La technologie basculer-chip est l'une des techniques les plus anciennes et les plus largement utilisées pour l'emballage de semi-conducteurs. Le basculer-chip un été initialement introduit par IBM il y un 30 ans. Néanmoins, elle suit l'époque et développe de nouvelles solutions de bumping pour servir les technologies avancées telles que 2.5D et 3D. Le basculer chip est utilisé pour les applications traditionnelles, telles que les ordinateurs portables, les ordinateurs de bureau, CPU, GPU, chipsets, etc.

| Pilier de cuivre |

| Soudure eutectique étain-plomb |

| Soudure sans plomb (SnAg, SAC, etc.) |

| Bumping gold-stud |

| Hybride Cu-to-Cu / Liaison directe |

| FC-BGA (2D/2.1D/2.5D/3D) |

| FCCSP / CSP |

| CoWoS / InFO / EMIB |

| Fan-Out WLP / PLP |

| 3D IC avec TSV |

| Mémoire (DRAM, HBM) |

| Capteur d'image CMOS |

| LED et Mini/Micro-LED |

| SoC / Processeur d'application |

| GPU / Accélérateur IA |

| CPU / Processeur serveur |

| Électronique grand public et objets connectés |

| Automobile et transport |

| Industriel et robotique |

| Télécommunications et infrastructure 5G |

| Centre de données et cloud |

| Militaire et aérospatiale |

| Dispositifs médicaux et de santé |

| Amérique du Nord | États-Unis | |

| Canada | ||

| Mexique | ||

| Amérique du Sud | Brésil | |

| Reste de l'Amérique du Sud | ||

| Europe | Allemagne | |

| France | ||

| Royaume-Uni | ||

| Russie | ||

| Reste de l'Europe | ||

| Asie-Pacifique | Chine | |

| Taïwan | ||

| Corée du Sud | ||

| Japon | ||

| Malaisie | ||

| Singapour | ||

| Reste de l'Asie-Pacifique | ||

| Moyen-Orient et Afrique | Moyen-Orient | Turquie |

| Reste du Moyen-Orient | ||

| Afrique | Afrique du Sud | |

| Reste de l'Afrique | ||

| Par processus de bumping de wafer | Pilier de cuivre | ||

| Soudure eutectique étain-plomb | |||

| Soudure sans plomb (SnAg, SAC, etc.) | |||

| Bumping gold-stud | |||

| Hybride Cu-to-Cu / Liaison directe | |||

| Par technologie d'emballage | FC-BGA (2D/2.1D/2.5D/3D) | ||

| FCCSP / CSP | |||

| CoWoS / InFO / EMIB | |||

| Fan-Out WLP / PLP | |||

| 3D IC avec TSV | |||

| Par produit | Mémoire (DRAM, HBM) | ||

| Capteur d'image CMOS | |||

| LED et Mini/Micro-LED | |||

| SoC / Processeur d'application | |||

| GPU / Accélérateur IA | |||

| CPU / Processeur serveur | |||

| Par industrie d'utilisation finale | Électronique grand public et objets connectés | ||

| Automobile et transport | |||

| Industriel et robotique | |||

| Télécommunications et infrastructure 5G | |||

| Centre de données et cloud | |||

| Militaire et aérospatiale | |||

| Dispositifs médicaux et de santé | |||

| Par géographie | Amérique du Nord | États-Unis | |

| Canada | |||

| Mexique | |||

| Amérique du Sud | Brésil | ||

| Reste de l'Amérique du Sud | |||

| Europe | Allemagne | ||

| France | |||

| Royaume-Uni | |||

| Russie | |||

| Reste de l'Europe | |||

| Asie-Pacifique | Chine | ||

| Taïwan | |||

| Corée du Sud | |||

| Japon | |||

| Malaisie | |||

| Singapour | |||

| Reste de l'Asie-Pacifique | |||

| Moyen-Orient et Afrique | Moyen-Orient | Turquie | |

| Reste du Moyen-Orient | |||

| Afrique | Afrique du Sud | ||

| Reste de l'Afrique | |||

Questions clés répondues dans le rapport

Quelle est la valeur actuelle du marché de la technologie basculer chip ?

Le marché mondial de la technologie basculer chip était valorisé à 35,51 milliards USD en 2025.

À quelle vitesse le marché de la technologie basculer chip devrait-il croître ?

Entre 2025 et 2030, le marché devrait enregistrer un TCAC de 7,49 %.

Quel processus de bumping de wafer mène le marché ?

Le bumping pilier de cuivre détenait 46,3 % des parts de revenus en 2024, reflétant sa performance électrique supérieure.

Pourquoi l'IA stimule-t-elle la demande d'emballage avancé ?

Les accélérateurs IA nécessitent des piles de mémoire haute bande passante et des interconnexions à pas fin que seuls les packages basculer chip avancés peuvent fournir.

Quelle région domine le marché de la technologie basculer chip ?

L'Asie-Pacifique un capturé 54,5 % des revenus de 2024, soutenue par une capacité extensive de fabrication de wafer et d'emballage.

Quelle est l'industrie d'utilisation finale à croissance la plus rapide ?

Les applications de centres de données et cloud devraient croître à un TCAC de 9,1 % jusqu'en 2030 avec l'expansion des charges de travail IA.

Dernière mise à jour de la page le: