Tamaño y participación del mercado de memoria dinámica de acceso aleatorio (DRAM)

Análisis del mercado de memoria dinámica de acceso aleatorio (DRAM) por Mordor Intelligence

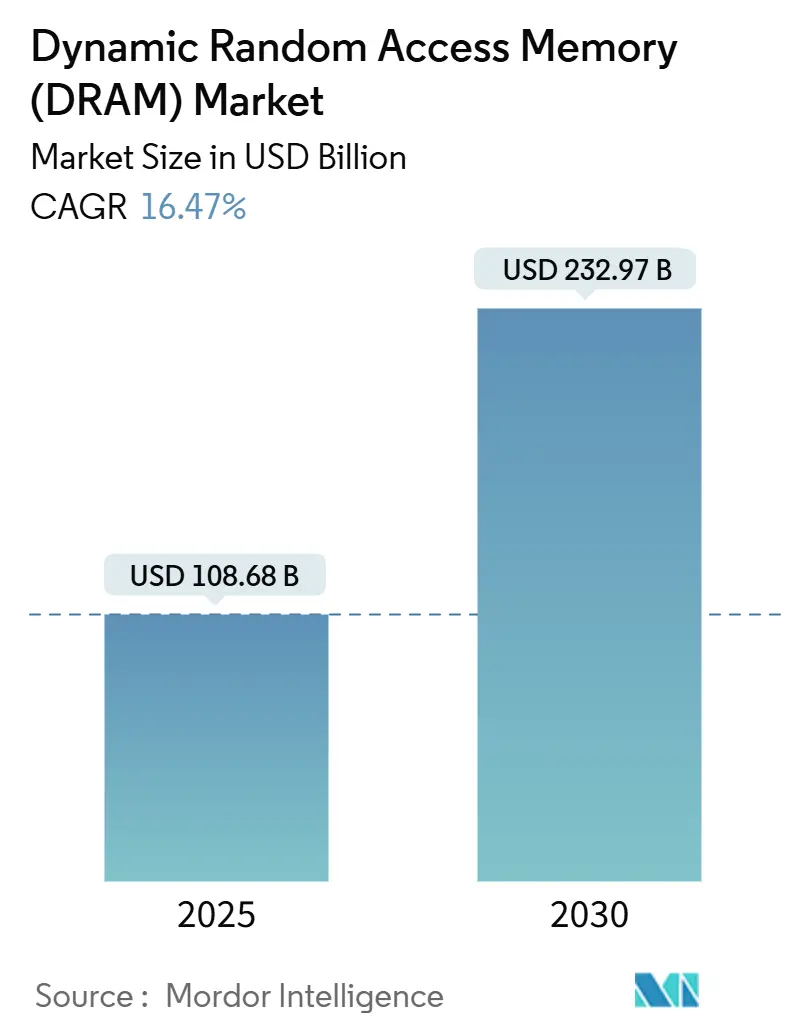

El tamaño del mercado de memoria dinámica de acceso aleatorio está valorado en USD 108,68 mil millones en 2025 y se proyecta que alcance los USD 232,97 mil millones para 2030, lo que se traduce en una sólida TCAC del 16,47%. La adopción acelerada de servidores centrados en IA, el aumento pronunciado de memoria de alto ancho de banda, y los requisitos de calificación automotriz más estrictos han cambiado los criterios de compra de capacidad únicamente a un enfoque equilibrado en ancho de banda, potencia y rendimiento térmico. Los operadores de nube de hiperescala comenzaron a renovar racks con módulos DDR5 y HBM3E durante 2024, mientras que los fabricantes de equipos originales de teléfonos móviles en Asia trasladaron gran parte de sus carteras insignia y de gama media a LPDDR5X, manteniendo colectivamente la utilización de fábricas por encima del 95% hasta mediados de 2025. El contenido de memoria por vehículo eléctrico aumentó rápidamente a medida que las arquitecturas zonales reemplazaron las redes ECU tradicionales, empujando la demanda de DRAM automotriz al territorio de múltiples gigabytes. Al mismo tiempo, los conflictos de asignación de suministro entre las líneas lucrativas de HBM3E y DDR4 heredadas desencadenaron aumentos de precios que reformaron las compensaciones costo-rendimiento para PCs, teléfonos inteligentes y placas IoT industriales.

Puntos clave del informe

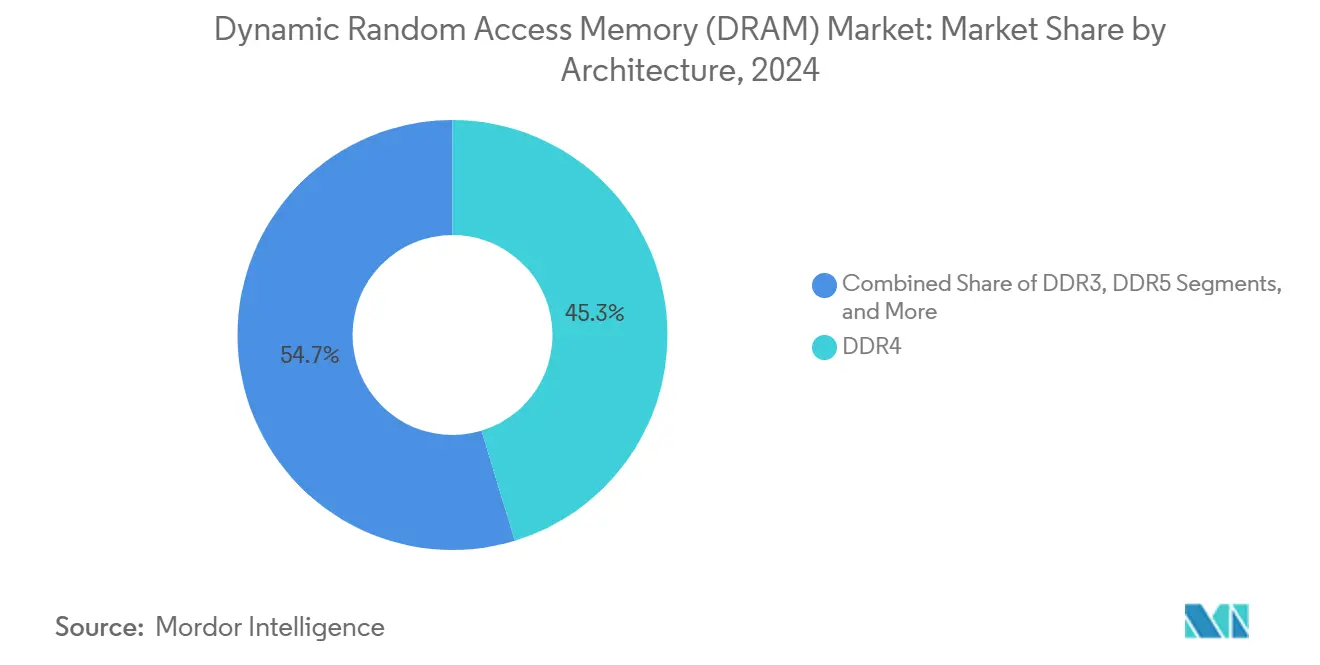

- Por arquitectura, DDR4 mantuvo una participación del mercado de memoria dinámica de acceso aleatorio del 45,3% en 2024, mientras que DDR5 se pronostica que se expandirá a una TCAC del 30,2% hasta 2030.

- Por nodo tecnológico, la categoría de 19 nm-10 nm capturó el 42,3% del tamaño del mercado de memoria dinámica de acceso aleatorio en 2024 y está avanzando a una TCAC del 25,2% hasta 2030.

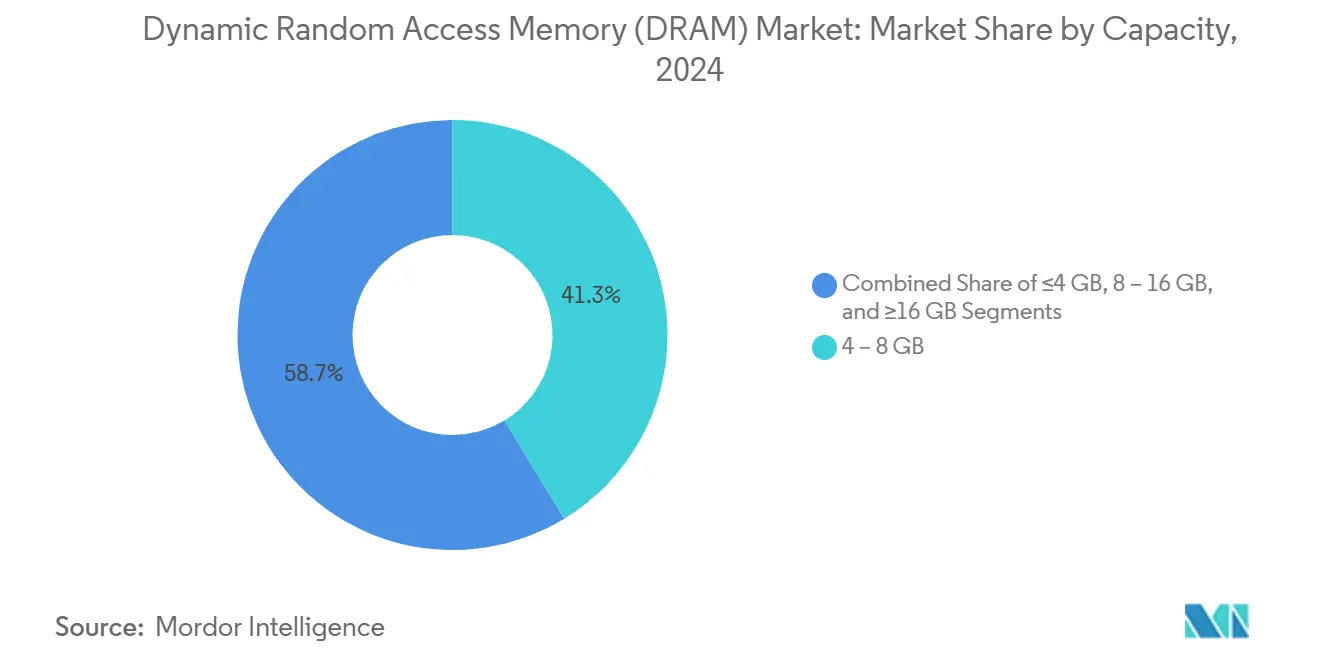

- Por capacidad, los módulos de 4-8 GB comandaron el 41,3% del tamaño del mercado de memoria dinámica de acceso aleatorio en 2024, mientras que las configuraciones ≥16 GB están preparadas para crecer al 28,2% entre 2025 y 2030.

- Por aplicación de uso final, los teléfonos inteligentes y tabletas lideraron con una participación de ingresos del 35,2% en 2024; se proyecta que la electrónica automotriz suba a una TCAC del 31,2% hasta 2030.

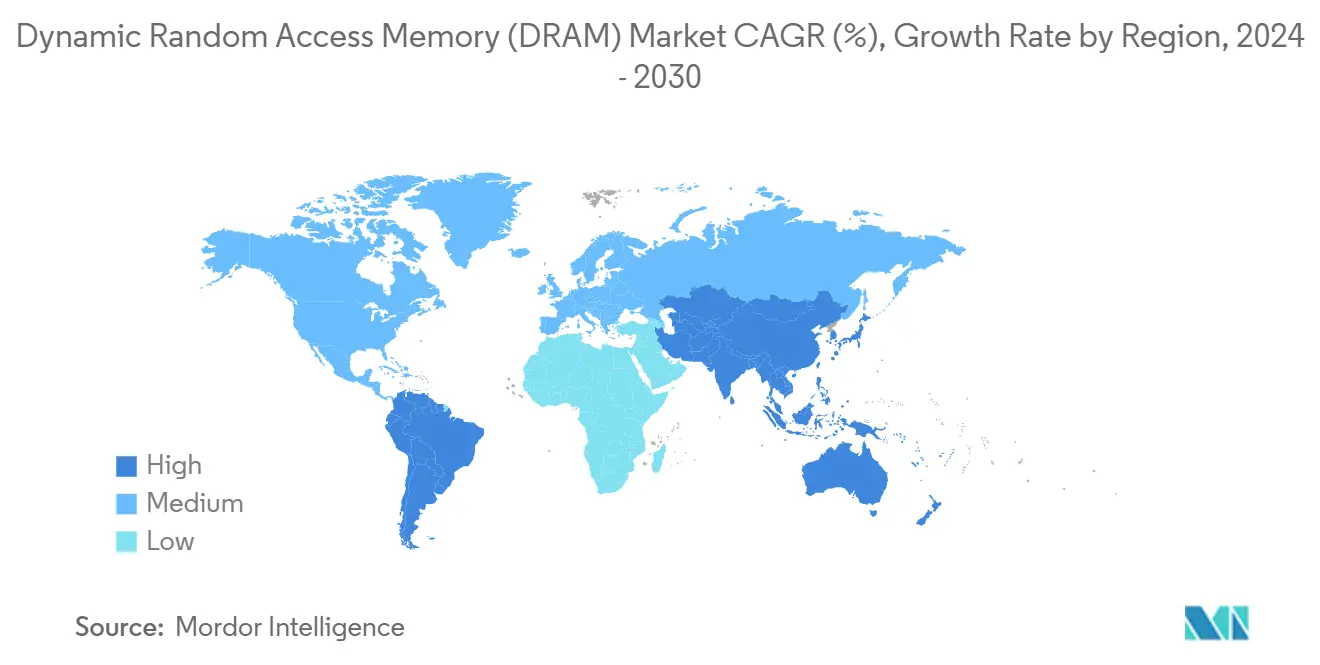

- Por geografía, Asia-Pacífico representó el 31,2% de las ventas de 2024, mientras que se espera que América del Sur registre una TCAC del 22,2% durante la ventana de pronóstico.

Tendencias e insights del mercado global de memoria dinámica de acceso aleatorio (DRAM)

Análisis de impacto de impulsores

| Impulsor | (~) % Impacto en el pronóstico de TCAC | Relevancia geográfica | Cronograma de impacto |

|---|---|---|---|

| Huella de contenido ascendente de cargas de trabajo de IA e IA generativa en centros de datos de hiperescala | +4.2% | Global, con concentración en América del Norte y APAC | Mediano plazo (2-4 años) |

| Adopción creciente de LPDDR en teléfonos inteligentes 5G insignia y de gama media en APAC | +3.8% | Núcleo APAC, expansión a mercados globales | Corto plazo (≤ 2 años) |

| Controladores zonales/de dominio automotriz migrando de NOR a DRAM de alta temperatura | +2.9% | Global, adopción temprana en Europa y América del Norte | Largo plazo (≥ 4 años) |

| Placas edge-AI e IoT industrial que requieren módulos DRAM de temperatura extendida | +2.1% | Global, con centros de fabricación en APAC | Mediano plazo (2-4 años) |

| Transición de proveedores de servicios en la nube a pools de memoria conectada por CXL | +1.8% | América del Norte y UE, expandiéndose a APAC | Largo plazo (≥ 4 años) |

| Fuente: Mordor Intelligence | |||

Huella de contenido ascendente de cargas de trabajo de IA e IA generativa en centros de datos de hiperescala

Las plataformas GP-AI Blackwell 2025 de NVIDIA establecieron líneas base de ancho de banda que eclipsaron las arquitecturas DDR convencionales, elevando la memoria promedio del servidor de 256 GB en 2024 a implementaciones de múltiples terabytes a mediados de 2025. Con cada pila HBM3E entregando más de 1 TB/s, los operadores de nube re-arquitecturaron racks alrededor de topologías centradas en memoria. Samsung entregó DRAM CXL 2.0 lista para producción que permitió a Azure y otros proveedores agrupar memoria entre hosts, mejorando la utilización mientras se difería el capex en nodos de computación adicionales.[1]Samsung Electronics, "CXL DRAM Enables New Data-Center Memory Architecture," semiconductor.samsung.com Los proveedores consecuentemente cambiaron los inicios de oblea de DDR4 a HBM, desencadenando escasez en grados heredados pero acelerando el crecimiento de ganancias en el segmento premium.

Adopción creciente de LPDDR en teléfonos inteligentes 5G insignia y de gama media en APAC

Las muestras LPDDR5X 1γ de Micron funcionando a 9.200 MT/s llegaron a fabricantes de teléfonos móviles en Q1 2025, reduciendo el consumo en 20% y elevando las configuraciones base en modelos chinos e indios de 8 GB a 12 GB de RAM. Xiaomi, OPPO y marcas emergentes como Transsion están bloqueadas en contratos futuros que consumen una porción creciente de la capacidad de fabricación APAC, forzando a los proveedores a hacer malabarismos con compromisos entre líneas móviles y de centros de datos. El cambio le dio a LPDDR una curva de crecimiento más pronunciada que cualquier otra memoria móvil desde que LPDDR4 entró en producción masiva en 2015.

Controladores zonales y de dominio automotriz migrando de NOR a DRAM de alta temperatura

Los vehículos eléctricos construidos sobre plataformas definidas por software requerían pools de memoria que empequeñecían las huellas de infoentretenimiento heredadas. Varios fabricantes europeos validaron DRAM calificada AEC-Q100 de 16 GB en 2024 y posteriormente elevaron los objetivos de plataforma hacia 90 GB por vehículo en los horarios de 2025. Samsung y SK Hynix invirtieron en ajustes de proceso de temperatura amplia para asegurar la conformidad ISO 26262, creando barreras para nuevos participantes y mejorando la disciplina de precios en el rincón de grado automotriz del mercado de memoria dinámica de acceso aleatorio.

Placas edge-AI e IoT industrial que requieren módulos DRAM de temperatura extendida

Los proveedores de automatización de fábrica actualizaron controladores lógicos programables y sistemas de visión con DDR4-3200 en clasificaciones de -40 °C a 85 °C, habilitando inferencia de IA local que reduce la latencia de ida y vuelta a la nube. ATP e Innodisk capitalizaron el nicho ofreciendo DIMMs recubiertos conformes con gestión agresiva de actualización, que los fabricantes industriales aceptaron con primas del 30% sobre las piezas de grado comercial. El resultado de mejora de margen incentivó a los principales de DRAM a licenciar procesos de endurecimiento, expandiendo el suministro hasta 2026.

Análisis de impacto de restricciones

| Restricción | (~) % Impacto en el pronóstico de TCAC | Relevancia geográfica | Cronograma de impacto |

|---|---|---|---|

| Ciclicidad de oferta-demanda impulsando volatilidad extrema de ASP | -2.8% | Global, con efectos amplificados en mercados al contado | Corto plazo (≤ 2 años) |

| Desafíos de erosión de rendimiento por debajo de nodos EUV de 10 nm | -1.9% | Global, concentrado en fábricas avanzadas | Mediano plazo (2-4 años) |

| Controles de exportación geopolíticos sobre China limitando envíos de DRAM de servidor de alta densidad | -1.4% | Enfocado en China, con impactos en la cadena de suministro global | Largo plazo (≥ 4 años) |

| Fuente: Mordor Intelligence | |||

Ciclicidad de oferta-demanda impulsando volatilidad extrema de ASP

Los pull-ins de HBM de alto margen persuadieron a las fábricas a posponer las corridas de DDR4 a principios de 2025, encendiendo un salto de precio al contado del 50% para módulos principales en mayo. Los contratos DDR5 también subieron 15-20%, impulsando a los fabricantes a re-ingeniar las listas de materiales de productos o sobre-ordenar para protegerse contra picos adicionales. El bucle de retroalimentación amplificó la volatilidad y redujo la visibilidad para la planificación de producción, quitando más de dos puntos de la TCAC de pronóstico del mercado de memoria dinámica de acceso aleatorio.

Desafíos de erosión de rendimiento por debajo de nodos EUV de 10 nm

Las primeras corridas de nodos 1β y 1γ sufrieron defectividad de máscara y rugosidad estocástica del borde de línea, arrastrando los rendimientos al rango bajo del 70% en algunas fábricas. Samsung y Micron asignaron presupuestos considerables de I+D a mejoras de resistencia y nueva tecnología de película protectora, sin embargo, las curvas de aprendizaje alargaron los cronogramas de rampa. Los rendimientos ajustados redujeron la producción de chips durante una ventana de demanda pico, agregando presión de costos que se cascó a través de segmentos de consumo y empresa.[2]TrendForce, "Samsung Targets 1c DRAM Yield Improvement by Mid-2025," trendforce.com

Análisis de segmentos

Por arquitectura: la aceleración DDR5 remodela las jerarquías de memoria

DDR5 representó una participación mínima del mercado de memoria dinámica de acceso aleatorio en 2024, sin embargo, llevó la TCAC de pronóstico más rápida del 30,2%, respaldada por la actualización JESD79-5C de JEDEC que elevó los techos de rendimiento a 8.800 Mbps. Ese salto técnico permitió a los constructores de nube de nivel 1 ejecutar configuraciones mixtas DDR5-HBM3E que duplicaron el ancho de banda efectivo por socket. El DDR5 1γ de Micron alcanzó 9.200 MT/s en febrero de 2025, un hito que empujó a los fabricantes de servidores a adelantar las actualizaciones de plataforma. Mientras tanto, DDR4 retuvo una participación del mercado de memoria dinámica de acceso aleatorio del 45,3% durante 2024 porque los presupuestos de TI corporativa aún favorecían configuraciones optimizadas por costos. Las huellas heredadas de DDR3 y DDR2 continuaron encogiéndose a medida que los diseños industriales y automotrices migraron a estándares más nuevos.

Los proveedores enfrentaron un acto de equilibrio: cada oblea reasignada a DDR5 significaba menos chips DDR4 para PCs, impulsando picos de costos que fluyeron aguas abajo a ensambladores de portátiles en China. Los tenedores de inventario de cola larga explotaron el comercio de arbitraje, descargando DDR4 almacenado a primas no vistas desde 2017. El nuevo factor de forma CAMM2 de JEDEC eliminó las restricciones de altura de los SO-DIMMs, permitiendo que portátiles y servidores edge adopten pilas de un solo lado más densas. Esas ganancias de empaque se alimentaron en el impulso del mercado de memoria dinámica de acceso aleatorio hacia normas de mayor ancho de banda a través de dispositivos de consumo y empresa.

Nota: Participaciones de segmento de todos los segmentos individuales disponibles con la compra del informe

Por nodo tecnológico: los procesos avanzados impulsan la diferenciación competitiva

El rango de 19 nm-10 nm mantuvo el 42,3% del tamaño del mercado de memoria dinámica de acceso aleatorio en 2024 y se proyecta que crezca 25,2% hasta 2030 mientras los proveedores exprimen chips adicionales por oblea sin sumergirse en el abismo de riesgo de rendimiento de sub-10 nm. La producción 1γ habilitada por EUV comenzó a enviar unidades de ingresos en Q1 2025, pero los rendimientos de línea permanecieron al menos ocho puntos por debajo de las líneas maduras 1z. Consecuentemente, muchos fabricantes de dispositivos renovaron acuerdos para grados 1z y 1y para amortiguar el riesgo de costos, dando a los procesos de nodo medio un impulso de volumen.

SK Hynix presentó una hoja de ruta de DRAM de puerta vertical que promete apilamiento a nivel de oblea más allá de 2027, señalando el pivote a largo plazo de escalado lateral a arquitecturas 3D. Cada reducción planar sucesiva entrega menos del 12% de reducción de costos después de que se factorizan el conjunto de máscaras, materiales y depreciación, empujando a las fábricas a buscar rediseños estructurales en lugar de solo reducción geométrica. La sensibilidad de costos en electrónica móvil y de consumo mantuvo vivos los nodos ≥20 nm para SKUs enfocados en precio, asegurando una mezcla de producción estratificada que diversificó la producción de fábrica y apuntaló la resistencia general de ingresos.

Por capacidad: las configuraciones de alta densidad se aceleran a través de aplicaciones

Se proyecta que los módulos ≥16 GB registren una TCAC del 28,2% y se muevan del estado de nicho en 2024 a la adopción principal en automotriz y teléfonos móviles premium para 2030. El contenido por vehículo eléctrico aumentó de gigabytes de un solo dígito a principios de 2024 a aproximadamente 40 GB en construcciones piloto de finales de 2025, y las discusiones de hoja de ruta entre fabricantes europeos referencian objetivos de 4 TB para autonomía de Nivel 4 al final de la década. Los líderes de teléfonos inteligentes adoptaron niveles de 16 GB para lanzamientos insignia centrados en IA en H1 2025, ampliando el paraguas de precios para dispositivos de gama media de 12 GB. La categoría de 4-8 GB, aunque aún el 41,3% del tamaño del mercado de memoria dinámica de acceso aleatorio en 2024, comenzó a ceder participación mientras los teléfonos de nivel de entrada cruzaron la línea base de 6 GB.

Los proveedores se beneficiaron de ASPs más ricos en chips de alta densidad pero enfrentaron restricciones de inicio de oblea, especialmente al equilibrar compromisos de HBM3E. El aprendizaje de rendimiento en nodos 1γ y futuros 1δ dictará si las mezclas de capacidad pueden inclinarse más hacia arriba sin desencadenar choques de precios indebidos. Los distribuidores de canal en Shenzhen reportaron inventario más ajustado de chips de 8 GB durante Q2 2025 mientras las fábricas priorizaban coincidencias de chips de 16 GB para asegurar pedidos de centros de datos, ejemplificando la competencia entre vectores de demanda de consumo y empresa.

Por aplicación de uso final: la electrónica automotriz emerge como líder de crecimiento

Se pronostica que la electrónica automotriz suba a una TCAC del 31,2%, eclipsando tabletas y PCs como la vertical de movimiento más rápido del mercado de memoria dinámica de acceso aleatorio. Las arquitecturas de computación zonal mandataron DRAM de alta temperatura y alta confiabilidad que opera sobre -40 °C a 125 °C, y las victorias de diseño en plataformas del año modelo 2026 bloquearon compromisos de compra que se extienden más allá de 2029. Los pools de memoria se acercaron a 90 GB en prototipos de EV premium durante 2025, equipando vehículos para actualizaciones continuas por aire y asistencia al conductor basada en IA. Los envíos de teléfonos inteligentes y tabletas aún entregaron una participación de ingresos del 35,2% en 2024, pero la saturación en regiones maduras temperó su trayectoria de crecimiento.

La demanda de centros de datos permaneció robusta, impulsada por clústeres de inferencia y entrenamiento de IA cuyos ciclos de expansión ahora se miden en trimestres en lugar de años. Las actualizaciones de gráficos y consolas de juegos programadas para finales de 2026 proporcionarán un impulso cíclico para variantes GDDR y DDR6. IoT industrial y gateways edge tomaron participación incremental adoptando módulos endurecidos por temperatura de 8-16 GB, aunque su naturaleza fragmentada diluyó el poder de negociación de cualquier OEM individual. El paisaje de aplicaciones heterogéneo refuerza las complejidades de asignación de suministro, obligando a los proveedores a hacer malabares con diferentes certificaciones de calidad, factores de forma y ciclos de vida en paralelo.

Análisis geográfico

Asia-Pacífico retuvo una posición de ingresos del 31,2% en 2024 con la fuerza de fábricas agrupadas en Corea del Sur, Taiwán y China continental. Los proveedores surcoreanos prometieron KRW 120 billones (USD 84 mil millones) para construcciones de capacidad hasta 2028, una cifra destinada a salvaguardar el liderazgo tanto en HBM como en producción tradicional de DRAM.[3]SK Hynix, "SEDEX 2024: Showcasing AI Memory Leadership," news.skhynix.com Las casas de ensamblaje por contrato de Taiwán, mientras tanto, expandieron líneas de empaque avanzado para atender la demanda creciente de HBM4, aprovechando el conocimiento de front-end de nodos lógicos para introducir innovaciones Through-Silicon-Via que reducen la resistencia térmica.

América del Norte formó el mercado de consumo más grande mientras los constructores de hiperescala aceleraron las actualizaciones de racks y los fabricantes de automóviles en Estados Unidos integraron controladores zonales. Micron aseguró USD 6,1 mil millones en financiamiento del CHIPS Act para construir una nueva megafábrica, un movimiento destinado a reducir el riesgo de exposición geopolítica y acortar los tiempos de entrega para clientes domésticos. Europa mantuvo un enfoque tecnológico en aplicaciones automotrices e industriales, con fabricantes alemanes insistiendo en garantías de temperatura extendida y longevidad que obtuvieron precios premium.

Se pronostica que América del Sur crezca a una TCAC del 22,2% mientras Brasil, Argentina y México nutren ecosistemas de ensamblaje electrónico para localizar el suministro. Los incentivos de política redujeron aranceles de importación en componentes de memoria ensamblados domésticamente, creando cambios modestos pero significativos en estrategias de abastecimiento. El Oriente Medio y África mostraron crecimiento de un solo dígito medio anclado por construcciones de centros de datos en estados del Consejo de Cooperación del Golfo y penetración creciente de teléfonos inteligentes en Nigeria y Kenia, sin embargo, la inestabilidad política continuó temperando una adopción más amplia. Combinadas, estas narrativas regionales subrayan cómo el mercado de memoria dinámica de acceso aleatorio diversifica las corrientes de ingresos incluso mientras la fabricación permanece concentrada en Asia Oriental.

Panorama competitivo

El mercado de memoria dinámica de acceso aleatorio operó como un oligopolio en 2025, con Samsung, SK Hynix y Micron manteniendo conjuntamente aproximadamente el 95% de la capacidad de obleas. SK Hynix se adelantó con una participación del 36% en Q1 2025 después de ser el primero en producir en volumen pilas HBM3E de 1,15 TB/s para programas líderes de aceleradores de IA. Samsung retuvo el liderazgo en líneas de grado automotriz y aseguró un acuerdo de suministro de USD 3 mil millones con AMD para futuros nodos HBM3E. Micron cerró la brecha tecnológica enviando DDR5 1γ y LPDDR5X seis meses antes de su hoja de ruta original, restaurando el equilibrio competitivo en categorías principales de DIMM.

La diferenciación tecnológica giró en torno a la adopción de EUV, con cada capa de máscara eliminada traduciéndose en ahorros de costos de chip apreciables. Sin embargo, la intensa intensidad de capital creó barreras para jugadores de segundo nivel como Nanya y Winbond, que eligieron especializarse en segmentos industriales de nicho o de bajo consumo en lugar de perseguir nodos de vanguardia. Las firmas chinas CXMT y JHICC expandieron la producción DDR5 usando procesos 1x maduros, suministrando ensambladores domésticos de teléfonos inteligentes que buscaban mitigar restricciones de exportación de EE.UU.

También surgieron alianzas de ecosistema alrededor de estándares de interconexión como CXL. Marvell se asoció con múltiples proveedores de DRAM para implementar controladores de expansión de memoria que elevan las tasas de conexión tanto para DDR4 como DDR5 agrupando recursos a través de hojas de servidor. La especificación HBM4 de JEDEC, publicada en abril de 2025, desencadenó nuevos acuerdos de desarrollo conjunto entre fabricantes de dispositivos y fundiciones para alinearse en pitch TSV, presupuestos térmicos y confiabilidad de empaque.[4]JEDEC, "JEDEC Publishes HBM4 Standard," jedec.org Contra este telón de fondo, las startups explorando MRAM, ReRAM y 3D X-AI apuntaron a descargas de carga de trabajo de nicho, aunque ninguna había demostrado aún paridad de costos con DRAM de commodity a mediados de 2025.

Líderes de la industria de memoria dinámica de acceso aleatorio (DRAM)

-

Samsung Electronics Co. Ltd.

-

Micron Technology Inc.

-

SK Hynix Inc.

-

Nanya Technology Corporation

-

Winbond Electronics Corporation

- *Nota aclaratoria: los principales jugadores no se ordenaron de un modo en especial

Desarrollos recientes de la industria

- Abril 2025: JEDEC lanzó el estándar HBM4 (JESD270-4), duplicando el recuento de canales a 32 y elevando el ancho de banda pico a 2 TB/s.

- Marzo 2025: SMART Modular introdujo un módulo de memoria CXL no volátil en factor de forma EDSFF para servidores intensivos en datos.

- Marzo 2025: KIOXIA presentó un SSD NVMe de 122,88 TB basado en BiCS FLASH de octava generación, dirigido a conjuntos de datos de IA.

- Febrero 2025: Micron Technology anunció el envío en volumen de DDR5 1γ funcionando a 9.200 MT/s con 20% menos de potencia, marcando la primera DRAM de sexta generación basada en EUV en el mercado.

Alcance del informe del mercado global de memoria dinámica de acceso aleatorio (DRAM)

La memoria dinámica de acceso aleatorio, llamada DRAM, se utiliza en varios dispositivos informáticos y electrónicos como PCs, teléfonos inteligentes, reproductores de música, portátiles, netbooks y computadoras tablet. El alcance del estudio se centra en el análisis de mercado de semiconductores DRAM vendidos en todo el mundo, y el dimensionamiento del mercado abarca los ingresos generados a través de DRAM vendida por varios actores del mercado a industrias de usuario final. El estudio también rastrea los parámetros clave del mercado, influenciadores de crecimiento subyacentes y principales proveedores operando en la industria, lo que apoyará las estimaciones de mercado y tasas de crecimiento durante el período de pronóstico. El estudio analiza además el impacto general de COVID-19 en el ecosistema.

El mercado DRAM está segmentado por arquitectura (DDR3, DDR4, DDR5 y DDR2), aplicaciones (teléfonos inteligentes/tabletas, PC/portátiles, centros de datos, gráficos, productos de consumo y automotriz), y geografía (Estados Unidos, Europa, Corea, China, Taiwán, el resto de Asia-Pacífico y el resto del mundo). El informe ofrece pronósticos de mercado y tamaños en valor (USD) para todos los segmentos anteriores.

| DDR2 y anteriores |

| DDR3 |

| DDR4 |

| DDR5 |

| LPDDR |

| GDDR |

| ≥20 nm |

| 19 nm - 10 nm |

| <10 nm (EUV) |

| ≤4 GB |

| 4 - 8 GB |

| 8 - 16 GB |

| ≥16 GB |

| Teléfonos inteligentes y tabletas |

| PCs y portátiles |

| Servidores y centros de datos de hiperescala |

| Gráficos y consolas de juegos |

| Electrónica automotriz |

| Electrónica de consumo (decodificadores, TV inteligentes, VR/AR) |

| Dispositivos industriales e IoT |

| Otros |

| América del Norte | Estados Unidos | |

| Canadá | ||

| México | ||

| Europa | Alemania | |

| Francia | ||

| Reino Unido | ||

| Nórdicos | ||

| Resto de Europa | ||

| Asia-Pacífico | China | |

| Taiwán | ||

| Corea del Sur | ||

| Japón | ||

| India | ||

| Resto de Asia-Pacífico | ||

| América del Sur | Brasil | |

| Chile | ||

| Argentina | ||

| Resto de América del Sur | ||

| Oriente Medio y África | Oriente Medio | Arabia Saudí |

| Emiratos Árabes Unidos | ||

| Turquía | ||

| Resto de Oriente Medio | ||

| África | Sudáfrica | |

| Resto de África | ||

| Por arquitectura | DDR2 y anteriores | ||

| DDR3 | |||

| DDR4 | |||

| DDR5 | |||

| LPDDR | |||

| GDDR | |||

| Por nodo tecnológico | ≥20 nm | ||

| 19 nm - 10 nm | |||

| <10 nm (EUV) | |||

| Por capacidad | ≤4 GB | ||

| 4 - 8 GB | |||

| 8 - 16 GB | |||

| ≥16 GB | |||

| Por aplicación de uso final | Teléfonos inteligentes y tabletas | ||

| PCs y portátiles | |||

| Servidores y centros de datos de hiperescala | |||

| Gráficos y consolas de juegos | |||

| Electrónica automotriz | |||

| Electrónica de consumo (decodificadores, TV inteligentes, VR/AR) | |||

| Dispositivos industriales e IoT | |||

| Otros | |||

| Por geografía | América del Norte | Estados Unidos | |

| Canadá | |||

| México | |||

| Europa | Alemania | ||

| Francia | |||

| Reino Unido | |||

| Nórdicos | |||

| Resto de Europa | |||

| Asia-Pacífico | China | ||

| Taiwán | |||

| Corea del Sur | |||

| Japón | |||

| India | |||

| Resto de Asia-Pacífico | |||

| América del Sur | Brasil | ||

| Chile | |||

| Argentina | |||

| Resto de América del Sur | |||

| Oriente Medio y África | Oriente Medio | Arabia Saudí | |

| Emiratos Árabes Unidos | |||

| Turquía | |||

| Resto de Oriente Medio | |||

| África | Sudáfrica | ||

| Resto de África | |||

Preguntas clave respondidas en el informe

¿Cuál es el valor actual del mercado de memoria dinámica de acceso aleatorio?

El mercado está valorado en USD 108,68 mil millones en 2025 y está establecido para alcanzar USD 232,97 mil millones para 2030.

¿Qué arquitectura DRAM está creciendo más rápido?

Se pronostica que DDR5 aumente a una TCAC del 30,2%, impulsado por servidores de IA y PCs de próxima generación.

¿Por qué son tan volátiles los precios de DRAM en 2025?

Las fábricas desviaron capacidad a HBM3E de mayor margen, llevando a un pico de precio al contado del 50% para DDR4 y aumentos del 15-20% para DDR5 en mayo de 2025.

¿Cómo está influyendo el sector automotriz en la demanda de DRAM?

Los vehículos definidos por software requieren DRAM de alta temperatura, empujando el contenido de memoria de gigabytes de un solo dígito en 2024 a aproximadamente 90 GB en prototipos de 2025 y mucho más alto en futuras plataformas de EV.

¿Qué región se espera que crezca más rápido hasta 2030?

Se proyecta que América del Sur se expanda a una TCAC del 22,2% mientras los incentivos de ensamblaje local atraen la producción electrónica.

¿Quién lidera el segmento HBM hoy?

SK Hynix se adelantó siendo el primero en fabricar pilas HBM3E de 16 capas, asegurando una participación del 36% de los envíos totales de DRAM en Q1 2025.

Última actualización de la página el: