Tamaño y participación del mercado de memoria estática de acceso aleatorio (SRAM)

Análisis del mercado de memoria estática de acceso aleatorio (SRAM) por Mordor Intelligence

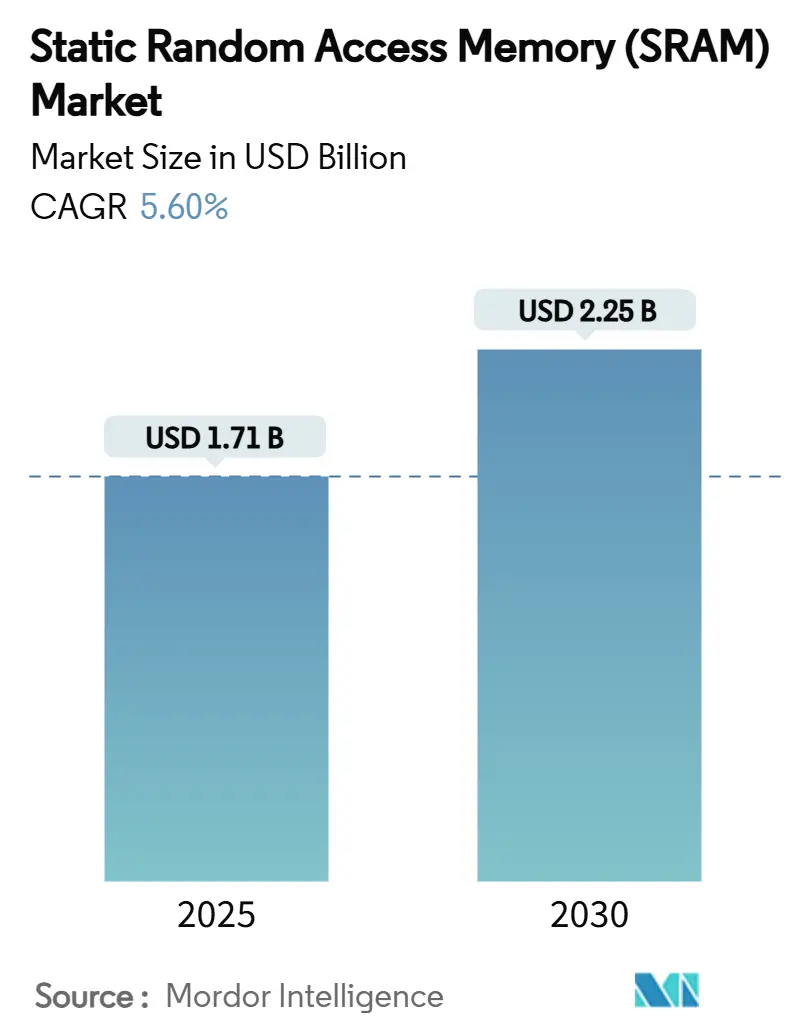

El tamaño del mercado global de memoria estática de acceso aleatorio se situó en USD 1,71 mil millones en 2025 y se pronostica que avance a una TCAC del 5,60% para alcanzar USD 2,25 mil millones para 2030. El crecimiento reflejó la transición hacia la computación centrada en IA, los despliegues de 5G y el procesamiento en tiempo real en el borde, todos los cuales dependen de la ultra baja latencia de la SRAM para las jerarquías de caché. Los proveedores de semiconductores priorizaron la reducción de las celdas SRAM a 2 nm para soportar cachés L2/L3 más grandes mientras mantienen los presupuestos de energía bajo control. La modernización de centros de datos impulsó la demanda de búferes de alta velocidad en switches y aceleradores, mientras que los ciclos de actualización de dispositivos de consumo mantuvieron una línea base estable. La resistencia de la cadena de suministro se volvió fundamental después del terremoto de Taiwán de 2024 que interrumpió la producción de fundiciones, lo que provocó iniciativas de diversificación geográfica. Mientras tanto, las memorias no volátiles emergentes como la MRAM intensificaron la presión competitiva sobre la SRAM convencional en diseños respaldados por batería.[1]Everspin Technologies, "MRAM Replaces nvSRAM," everspin.com

Conclusiones clave del informe

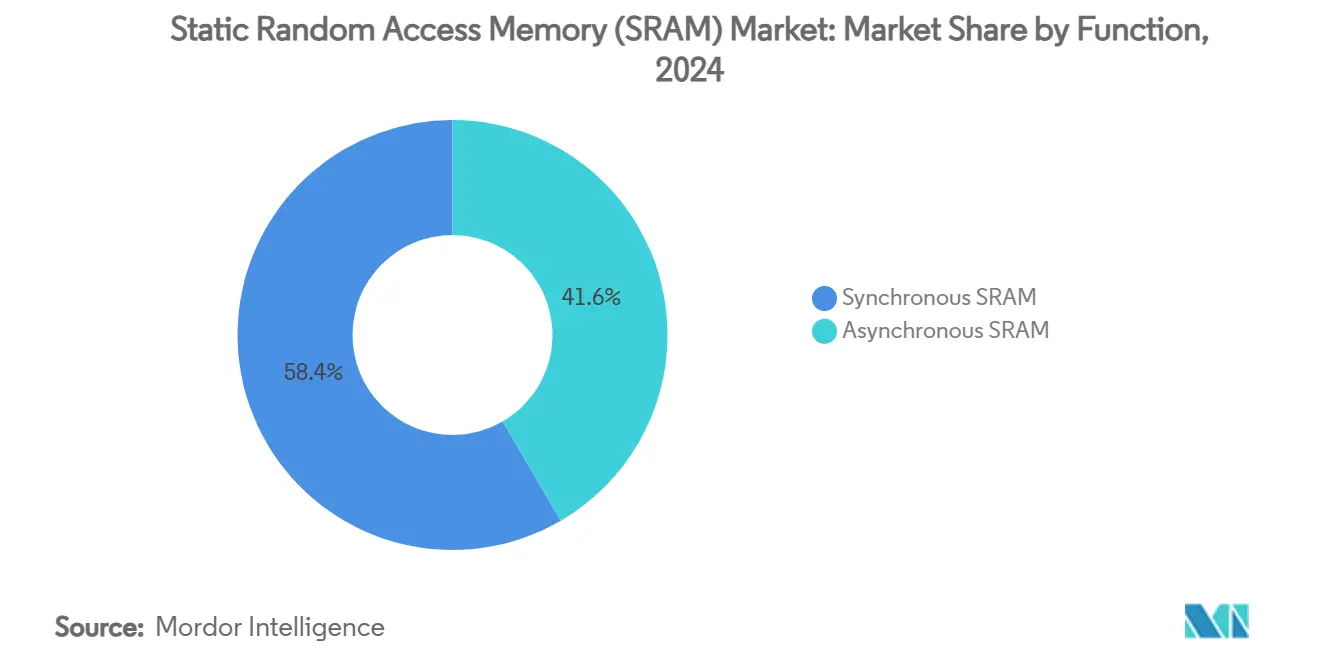

Por función, la SRAM síncrona mantuvo el 58,4% de participación del mercado de memoria estática de acceso aleatorio en 2024; la SRAM asíncrona registró la TCAC más rápida del 6,4% hasta 2030.

Por tipo de producto, la pseudo-SRAM lideró con el 54,4% de participación de ingresos en 2024, mientras que se proyecta que la SRAM no volátil se expanda a una TCAC del 8,7%.

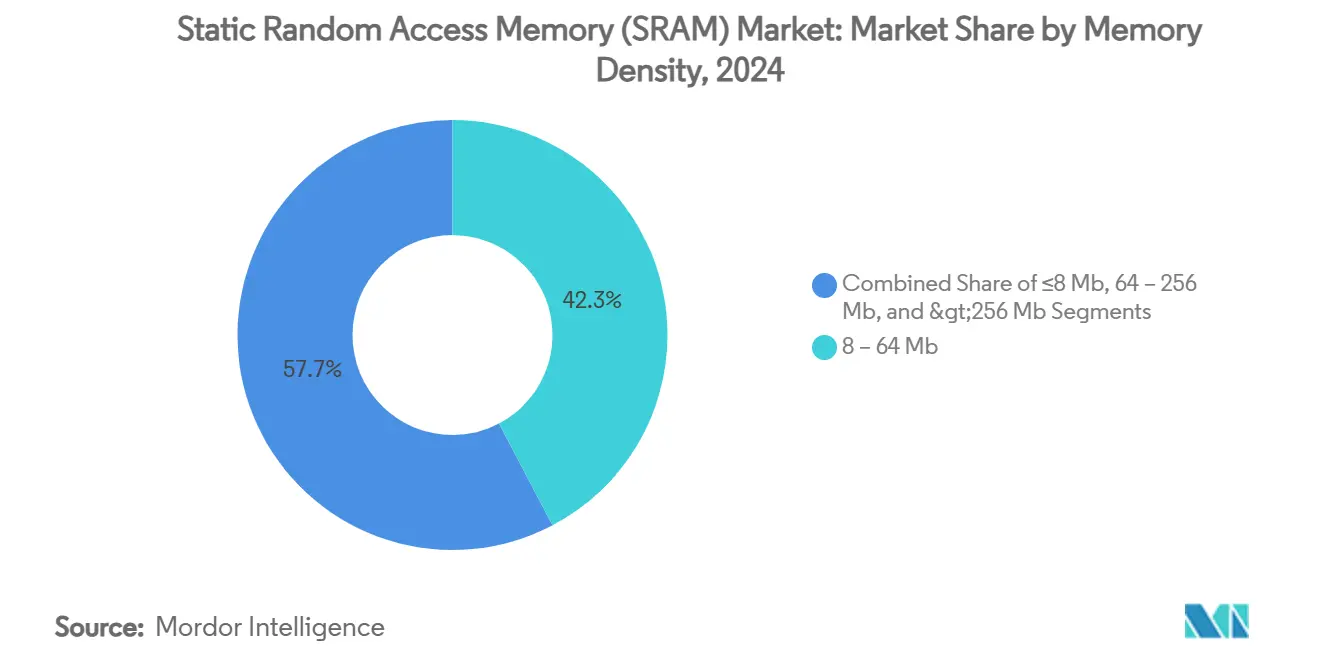

Por densidad de memoria, el nivel de 8-64 Mb representó el 42,3% del tamaño del mercado de memoria estática de acceso aleatorio en 2024; las densidades superiores a 256 Mb están preparadas para crecer a una TCAC del 7,5%.

Por usuario final, la electrónica de consumo capturó el 46,3% de los ingresos en 2024; el sector automotriz y aeroespacial están avanzando a una TCAC del 9,1%.

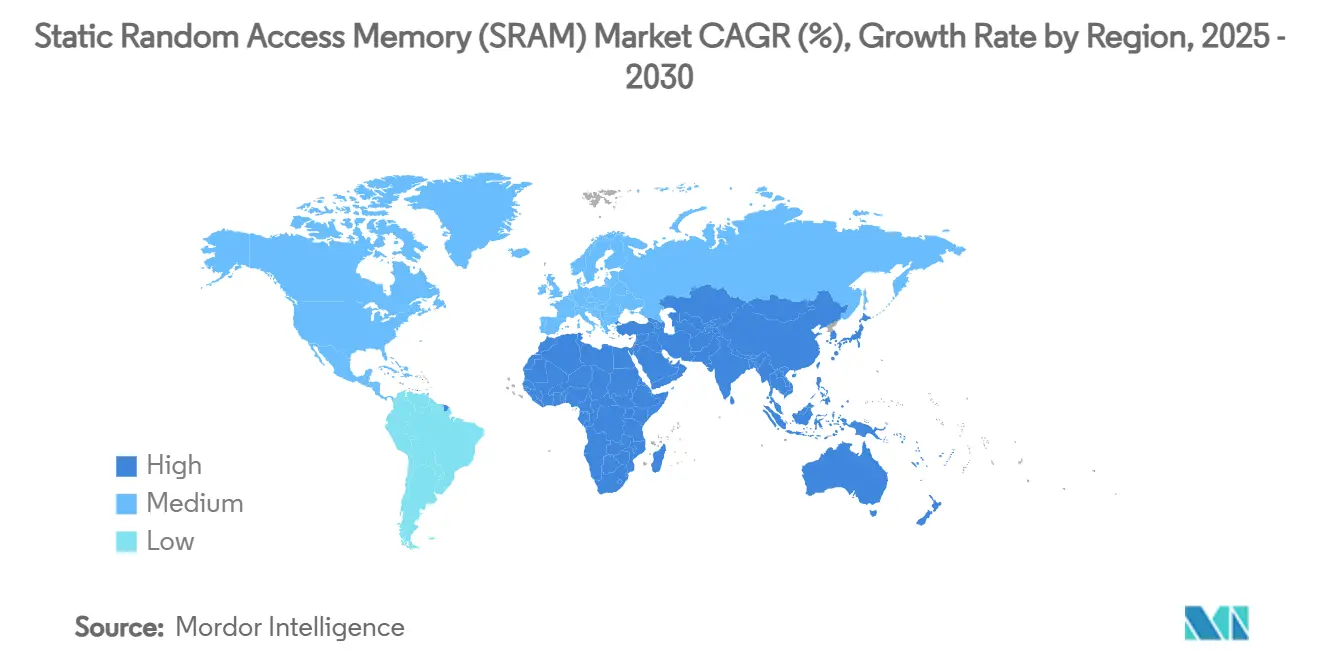

Por geografía, Asia-Pacífico dominó con el 61,4% de participación del mercado de memoria estática de acceso aleatorio en 2024, mientras que Oriente Medio y África son las regiones de crecimiento más rápido con una TCAC del 7,5%.

Tendencias e insights del mercado global de memoria estática de acceso aleatorio (SRAM)

Análisis de impacto de los impulsores

| Impulsor | (~) % Impacto en pronóstico TCAC | Relevancia geográfica | Cronograma de impacto |

|---|---|---|---|

| Creciente demanda de memorias caché más rápidas | +1.2% | Global, concentrado en América del Norte y Asia-Pacífico | Mediano plazo (2-4 años) |

| Construcción de centros de datos y redes 5G | +1.0% | Global, con énfasis en Asia-Pacífico y América del Norte | Corto plazo (≤ 2 años) |

| Proliferación de IoT y dispositivos portables | +0.8% | Global, liderado por centros de manufactura en Asia-Pacífico | Mediano plazo (2-4 años) |

| SRAM integrada en 3D para chiplets | +0.6% | América del Norte y fábricas avanzadas de Asia-Pacífico | Largo plazo (≥ 4 años) |

| SRAM endurecida contra radiación para satélites LEO | +0.4% | Global, concentrado en América del Norte y Europa | Largo plazo (≥ 4 años) |

| Adopción de aceleradores de IA en memoria | +0.7% | Global, con liderazgo de América del Norte y Asia-Pacífico | Mediano plazo (2-4 años) |

| Fuente: Mordor Intelligence | |||

Creciente demanda de memorias caché más rápidas

Los CPUs y GPUs avanzados enviados en 2025 presentaron cachés integrados más grandes para reducir la latencia de inferencia, con el Xeon 6 de Intel mostrando un aumento de rendimiento de 1,4× vinculado a la optimización de caché. La plataforma de 2 nm de TSMC entregó mayor densidad de celdas SRAM que los nodos 18A competidores, dando a los clientes de hiperescala más caché L3 por vatio. Marvell reveló SRAM personalizada de 2 nm que empaqueta 6 Gb de memoria de bajo consumo, reduciendo el uso de energía en un 66% versus nodos anteriores. Tales innovaciones permitieron a los aceleradores de IA mantener los parámetros del modelo más cerca de las unidades de computación, sosteniendo el rendimiento mientras contienen el tráfico de DRAM. En consecuencia, el mercado de memoria estática de acceso aleatorio se benefició de las actualizaciones recurrentes de capacidad a través del silicio de centros de datos y borde.

Construcción de centros de datos y redes 5G

Los operadores de nube duplicaron las densidades de rack para alojar servidores de IA, promoviendo un uso más amplio de búferes de paquetes basados en SRAM en switches top-of-rack. Microsoft probó backplanes inalámbricos de 246-275 GHz en salas de servidores, donde el almacenamiento en búfer a escala de microsegundos dependía de SRAM de alta velocidad. El transporte 5G convergente de Cisco promovió latencia determinística, requiriendo colas profundas de SRAM en enrutadores. Corning pronostica un salto de 18× en la demanda de fibra por rack de IA, reflejando el escalamiento de búferes de switch construidos sobre SRAM síncrona. Esta ola de infraestructura reforzó la visibilidad de ingresos a corto plazo para el mercado de memoria estática de acceso aleatorio.

Proliferación de IoT y dispositivos portables

Los chips de borde de ultra bajo consumo que alimentan dispositivos portables de salud adoptaron bloques SRAM personalizados que retienen datos a microvatios de un solo dígito; los procesadores neurales de Syntiant ejemplificaron la tendencia. Las puertas de enlace Edge2LoRa integraron SRAM modesta para preprocesar datos de sensores, reduciendo el ancho de banda de backhaul en un 90%. Los MCUs automotrices como el R-Car de Renesas integran SRAM determinística para actualizaciones over-the-air y cargas de trabajo ADAS. Colectivamente, estos despliegues ampliaron la base de clientes para productos SRAM asíncronos y pseudo-SRAM adaptados a restricciones de energía.

Adopción de aceleradores de IA en memoria

Los prototipos de investigación demostraron SRAM fotónica con lógica XOR integrada ejecutando a >10 GHz mientras consumen 13,2 fJ por bit, apuntando a futuras arquitecturas de computación en memoria. Una SRAM de computación en memoria de 28 nm y 36 Kb redujo la energía de actualización de pesos, allanando el camino para motores de inferencia de IA integrados. El PERSYST de Everspin posicionó la memoria persistente para cargas de trabajo de IA críticas para la seguridad donde se requiere retención de datos después de pérdida de energía. Estos avances aumentaron el interés en SRAM especializada que combina velocidad con programabilidad, expandiendo aún más el mercado de memoria estática de acceso aleatorio.

Análisis de impacto de las limitaciones

| Limitación | (~) % Impacto en pronóstico TCAC | Relevancia geográfica | Cronograma de impacto |

|---|---|---|---|

| Alto costo por bit vs. DRAM/NAND | -0.9% | Global, particularmente impactando aplicaciones sensibles al costo | Corto plazo (≤ 2 años) |

| Escalamiento de energía en nodos ≤5 nm | -0.7% | Fábricas avanzadas en Asia-Pacífico y América del Norte | Mediano plazo (2-4 años) |

| Desplazamiento de NVM emergente (MRAM/ReRAM) | -0.5% | Global, con adopción temprana en automotriz e industrial | Largo plazo (≥ 4 años) |

| Pérdida de rendimiento por variabilidad litográfica | -0.4% | Nodos de proceso avanzados globalmente | Mediano plazo (2-4 años) |

| Fuente: Mordor Intelligence | |||

Alto costo por bit vs. DRAM/NAND

La SRAM permaneció varias veces más costosa por bit que la DRAM de commodities, presionando a los diseñadores a recortar el uso en dispositivos del mercado masivo. Los precios de módulos DDR4 subieron aproximadamente 50% en el primer semestre de 2025, ilustrando la volatilidad a través de la pila de memoria. Samsung aprovechó el ajuste del suministro para elevar los precios de LPDDR4, pero esa táctica arriesgaba acelerar el interés de los OEM en arquitecturas híbridas SRAM-DRAM para reducir las listas de materiales. En consecuencia, el mercado de memoria estática de acceso aleatorio enfrentó resistencia en segmentos de consumo de nivel básico hasta que mejoraran las compensaciones entre densidad versus costo.

Desplazamiento de NVM emergente (MRAM/ReRAM)

Las uniones de túnel magnético CoFeB/MgO de un solo nanómetro lograron conmutación sub-10 ns y retención de diez años, habilitando que la MRAM reemplace a la nvSRAM en sistemas rugosos. Everspin comercializó la MRAM como un sustituto directo para SRAM respaldada por batería, ofreciendo no volatilidad sin capacitores externos. Los proveedores de FPGA automotrices como Lattice cambiaron de flash a memoria de configuración MRAM, mostrando adopción real.[2]Jim Tavacoli, "From Flash to MRAM," Lattice Semiconductor, latticesemi.com Si los costos de producción caen más, una porción del mercado de memoria estática de acceso aleatorio podría migrar hacia alternativas persistentes.

Análisis de segmentos

Por función: el rendimiento depende de arquitecturas síncronas

La SRAM síncrona capturó el 58,4% de participación del mercado de memoria estática de acceso aleatorio en 2024, subrayando su indispensabilidad para operación de caché determinística en CPUs, GPUs y ASICs de red. Los MCUs automotrices usaron arreglos síncronos para cumplir requisitos estrictos de tiempo real para cargas de trabajo de asistencia al conductor. El segmento mantendrá el liderazgo mientras los nodos avanzados extienden las envolventes de frecuencia y reducen voltajes de núcleo.

La SRAM asíncrona se expandió a una TCAC del 6,4% e sirvió cada vez más a dispositivos portables IoT y puertas de enlace de borde donde los presupuestos de energía superan los objetivos de latencia. Los diseños eficientes en energía eliminaron árboles de reloj y simplificaron los diseños de placa, una ventaja para dispositivos de salud operados por batería que emplean coprocesadores neurales de Syntiant. Esta divergencia enfatizó la tendencia del mercado de memoria estática de acceso aleatorio hacia la optimización específica de aplicación en lugar de la persecución de rendimiento de talla única.

Nota: Participaciones de segmento de todos los segmentos individuales disponibles con la compra del informe

Por tipo de producto: la pseudo-SRAM optimizada en costos prevalece

La pseudo-SRAM mantuvo una participación del 54,4% en 2024 al integrar celdas DRAM detrás de una interfaz estilo SRAM, logrando mayor densidad sin gestión de actualización a nivel del sistema. RAAAM Memory Technologies y NXP reclamaron ahorros del 50% en área y 10× en energía versus SRAM clásica de alta densidad, atrayendo a microcontroladores del mercado masivo.

La SRAM no volátil creció más rápido a una TCAC del 8,7% mientras las fábricas y vehículos demandaron integridad de datos durante caídas de voltaje. Los actores de automatización industrial seleccionaron módulos nvSRAM para proteger variables de proceso, evitando tiempo de inactividad costoso. Aunque de nicho, esta cohorte enriqueció el panorama del mercado de memoria estática de acceso aleatorio con características de resistencia de valor agregado.

Por densidad de memoria: el rango medio sigue siendo el punto ideal

El nivel de 8-64 Mb representó el 42,3% del tamaño del mercado de memoria estática de acceso aleatorio en 2024, coincidiendo con las huellas típicas de caché L2/L3 a través de CPUs mainstream. La SRAM rápida de 32 Mb de Alliance Memory en empaque FBGA ilustró el refinamiento continuo en esta zona.

Los dispositivos >256 Mb registraron una TCAC robusta del 7,5% mientras los aceleradores de IA buscaron cachés integrados más grandes para minimizar las búsquedas en DRAM. Micron proyectó que los automóviles pronto llevarían 90 GB de memoria total, sugiriendo una demanda creciente de SRAM de alta densidad en controladores zonales. La evolución de densidad, por lo tanto, reflejó el crecimiento de cargas de trabajo intensivas en computación que sustentan el mercado de memoria estática de acceso aleatorio.

Por usuario final: volumen de consumo vs. velocidad automotriz

La electrónica de consumo generó el 46,3% de los ingresos de 2024 gracias a la vasta escala de smartphones, tabletas y PCs. Micron y Samsung integraron LPDDR5X y SRAM a bordo en el Galaxy S24, elevando la capacidad de respuesta de IA móvil.

Los segmentos automotriz y aeroespacial registraron una TCAC del 9,1% mientras los vehículos definidos por software requirieron caché determinística para fusión de sensores y reconfiguración over-the-air. El MCU S32K5 de NXP con RAM magnética integrada escribe 15× más rápido que flash, demostrando el apetito por memoria de alta confiabilidad.[3]NXP Semiconductors, "S32K5 MCU," stocktitan.net Tal impulso amplió el mercado de memoria estática de acceso aleatorio más allá de los ciclos tradicionales de actualización de consumo.

Análisis geográfico

Asia-Pacífico retuvo el 61,4% de participación del mercado de memoria estática de acceso aleatorio en 2024, impulsado por el dominio de fundiciones de Taiwán, la innovación en memoria de Corea del Sur y los esfuerzos de escalamiento de China. El ascenso de SK Hynix al 36% de la producción global de DRAM destacó la profundidad tecnológica de la región. Sin embargo, el terremoto de Taiwán de 2024 expuso el riesgo de concentración, provocando fábricas de contingencia en Japón y Singapur. Japón proyectó ventas de equipos de semiconductores de JPY 5,51 billones (USD 38,35 mil millones) en el año fiscal 26, subrayando la construcción continua de capacidad.

Oriente Medio y África trazaron la TCAC más rápida del 7,5%, anclada por el gasto de fondos soberanos para posicionar el Golfo como un hub de datos tricontinental. La automatización de almacenes en la región estaba preparada para un crecimiento anual del 17,5% a USD 1,6 mil millones para 2025, impulsando la demanda de cachés a bordo confiables. Los proyectos energéticos de África destinaron USD 730 mil millones en nuevos capex hasta 2030, requiriendo sistemas de control industrial que se apoyen en SRAM para respuesta determinística.

América del Norte se enfocó en despliegues de centros de datos de IA, mientras Europa duplicó la apuesta por la soberanía a través de la Ley de Chips de EUR 43 mil millones. STMicroelectronics aseguró EUR 5 mil millones (USD 5,4 mil millones) para un campus de carburo de silicio en Italia, ampliando la competencia regional en electrónica de potencia que también consume SRAM especializada. Las escaseces de talento, sin embargo, amenazaron la expansión, con ASML advirtiendo que podría cambiar operaciones si se endureciera la inmigración. Estos contrastes destacan diversas palancas regionales que dan forma al mercado de memoria estática de acceso aleatorio.

Panorama competitivo

El mercado mostró consolidación moderada alrededor de fabricantes de dispositivos integrados y desafiantes alineados con fundiciones. Samsung, SK Hynix y Micron fortalecieron posiciones escalando hojas de ruta HBM; Samsung aceleró su fábrica de obleas de Pyeongtaek para capturar negocio HBM4. SK Hynix se asoció con TSMC en empaque avanzado para sostener el liderazgo en ancho de banda.[4]SK hynix, "Partners with TSMC to Strengthen HBM Leadership," skhynix.com

En la capa de IP y especialidad, GSI Technology y Cypress se dirigieron a equipos de red de baja latencia, mientras recién llegados como Numem planearon chiplets MRAM prometiendo rendimiento clase HBM para 2025. Imec, TSMC y Samsung-IBM cada uno demostró prototipos SRAM CFET con reducción del 40% en área de celda, anticipando híbridos lógica-memoria apilados en 3D.

Los nichos emergentes incluyeron celdas 18T endurecidas contra radiación para satélites LEO que mejoraron la estabilidad de lectura mientras reducían la energía en espera. El financiamiento del Consejo Europeo de Innovación habilitó a RAAAM para avanzar en pseudo-SRAM integrada para mercados MCU, ilustrando cómo la política regional catalizó nuevos participantes. La ventaja competitiva así giró hacia la innovación en empaque, el conocimiento de procesos especializados y la amplitud de propiedad intelectual, todo dando forma al futuro posicionamiento del mercado de memoria estática de acceso aleatorio.

Líderes de la industria de memoria estática de acceso aleatorio (SRAM)

-

Renesas Electronics Corporation

-

STMicroelectronics N.V.

-

Toshiba Corporation

-

Cypress Semiconductor

-

Integrated Silicon Solution, Inc. (ISSI)

- *Nota aclaratoria: los principales jugadores no se ordenaron de un modo en especial

Desarrollos recientes de la industria

- Julio 2025: Samsung aceleró la planta de obleas de Pyeongtaek para asegurar capacidad HBM4.

- Junio 2025: Marvell introdujo SRAM personalizada de 2 nm entregando capacidad de 6 Gb con 66% menor consumo.

- Junio 2025: SK Hynix registró un aumento de ganancias de KRW 9 billones por demanda HBM.

- Mayo 2025: Samsung y SK Hynix avanzaron en unión híbrida para HBM de próxima generación.

Alcance del informe del mercado global de memoria estática de acceso aleatorio (SRAM)

SRAM (RAM estática) es memoria de acceso aleatorio (RAM) que retiene bits de datos en su memoria mientras se suministre energía. A diferencia de la RAM dinámica (DRAM), que almacena bits en celdas que consisten en un capacitor y un transistor, la SRAM no tiene que ser refrescada periódicamente. La RAM estática proporciona acceso más rápido a los datos y es más costosa que la DRAM.

| SRAM asíncrona |

| SRAM síncrona |

| Pseudo SRAM (PSRAM) |

| SRAM no volátil (nvSRAM) |

| Otros tipos de productos |

| ≤8 Mb |

| 8 - 64 Mb |

| 64 - 256 Mb |

| >256 Mb |

| Electrónica de consumo |

| Industrial |

| Infraestructura de comunicaciones |

| Automotriz y aeroespacial |

| Otros usuarios finales |

| América del Norte | Estados Unidos | |

| Canadá | ||

| México | ||

| América del Sur | Brasil | |

| Argentina | ||

| Resto de América del Sur | ||

| Europa | Alemania | |

| Reino Unido | ||

| Francia | ||

| Italia | ||

| Rusia | ||

| Resto de Europa | ||

| Asia-Pacífico | China | |

| Japón | ||

| Corea del Sur | ||

| India | ||

| Taiwán | ||

| Resto de Asia-Pacífico | ||

| Oriente Medio y África | Oriente Medio | Turquía |

| Israel | ||

| Países del CCG | ||

| Resto de Oriente Medio | ||

| África | Sudáfrica | |

| Nigeria | ||

| Resto de África | ||

| Por función | SRAM asíncrona | ||

| SRAM síncrona | |||

| Por tipo de producto | Pseudo SRAM (PSRAM) | ||

| SRAM no volátil (nvSRAM) | |||

| Otros tipos de productos | |||

| Por densidad de memoria | ≤8 Mb | ||

| 8 - 64 Mb | |||

| 64 - 256 Mb | |||

| >256 Mb | |||

| Por usuario final | Electrónica de consumo | ||

| Industrial | |||

| Infraestructura de comunicaciones | |||

| Automotriz y aeroespacial | |||

| Otros usuarios finales | |||

| Por geografía | América del Norte | Estados Unidos | |

| Canadá | |||

| México | |||

| América del Sur | Brasil | ||

| Argentina | |||

| Resto de América del Sur | |||

| Europa | Alemania | ||

| Reino Unido | |||

| Francia | |||

| Italia | |||

| Rusia | |||

| Resto de Europa | |||

| Asia-Pacífico | China | ||

| Japón | |||

| Corea del Sur | |||

| India | |||

| Taiwán | |||

| Resto de Asia-Pacífico | |||

| Oriente Medio y África | Oriente Medio | Turquía | |

| Israel | |||

| Países del CCG | |||

| Resto de Oriente Medio | |||

| África | Sudáfrica | ||

| Nigeria | |||

| Resto de África | |||

Preguntas clave respondidas en el informe

¿Cuál es el valor actual del mercado de memoria estática de acceso aleatorio?

El mercado alcanzó USD 1,71 mil millones en 2025 y se pronostica que suba a USD 2,25 mil millones para 2030.

¿Qué región domina los ingresos del mercado de memoria estática de acceso aleatorio?

Asia-Pacífico representó el 61,4% de los ingresos globales en 2024, anclado por los ecosistemas de manufactura de Taiwán y Corea del Sur.

¿Qué segmento del mercado de memoria estática de acceso aleatorio está creciendo más rápido?

Las aplicaciones automotrices y aeroespaciales se están expandiendo a una TCAC del 9,1% mientras los vehículos adoptan arquitecturas definidas por software que requieren cachés de baja latencia.

¿Cómo está impactando la tecnología MRAM emergente la demanda de SRAM?

La MRAM ofrece no volatilidad y menor consumo en espera, desafiando a la SRAM en sistemas respaldados por batería y rugosos, potencialmente desviando participación a largo plazo.

¿Qué clase de densidad es más común en los chips SRAM actuales?

El rango de 8-64 Mb capturó el 42,3% de las ventas de 2024 porque se alinea con los tamaños de caché de procesadores mainstream.

¿Por qué la SRAM síncrona superó a los tipos asíncronos en participación de ingresos?

Los diseños sincronizados por reloj proporcionan temporización determinística esencial para CPUs, GPUs y ASICs de red de alto rendimiento, asegurando el 58,4% de participación de mercado en 2024.

Última actualización de la página el: