Halbleiterpackaging-Marktgröße und -anteil

Halbleiterpackaging-Marktanalyse von Mordor Intelligence

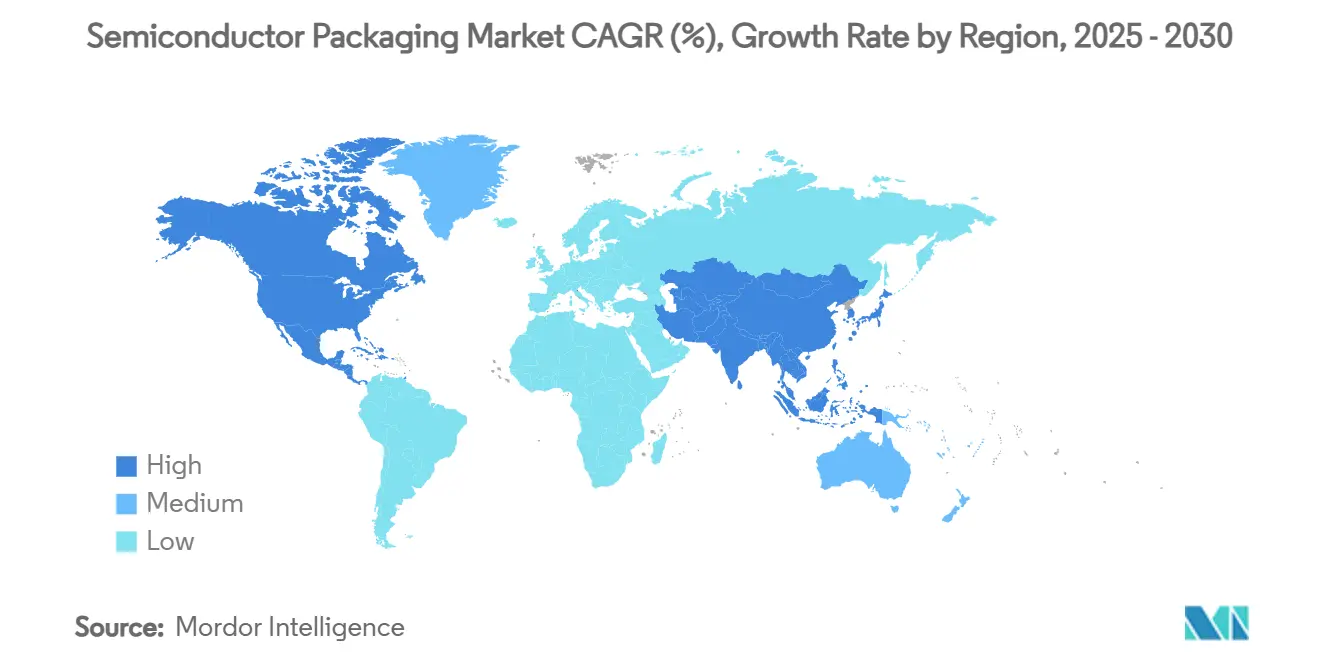

Die Halbleiterpackaging-Marktgröße betrug 49,88 Milliarden USD im Jahr 2025 und wird voraussichtlich bis 2030 81,22 Milliarden USD erreichen, mit einem Wachstum von 10,24 % CAGR über 2025-2030. [1]Cheng Ting-Fang, "TSMC moves closer to next-gen packaging for Nvidia, Google AI chips," Nikkei Asia, asia.nikkei.comEin Wandel von kostengetriebener Montage hin zu leistungskritischer Integration untermauert dieses Wachstum. Die Nachfrage nach 2,5D- und 3D-Architekturen ist stark gestiegen, da KI-Arbeitslasten High-Bandwidth-Memory und überlegene Thermalpfade erfordern. Das Volumen bleibt in traditionellen Wire-Bond- und Lead-Frame-Formaten verankert, doch die Wertschöpfung wandert zu Fan-Out Wafer-Level Packaging (WLP) und Chiplet-fähigen Interposern. Die Elektrifizierung im Automobilbereich unterstützt zweistellige Expansion bei leistungsdichten Modulen, während Smartphone- und PC-Aktualisierungszyklen Basisvolumen im Verbrauchersegment aufrechterhalten. Regional beherrscht Asien mehr als die Hälfte der globalen Produktion, aber Nordamerika verzeichnet die höchste CAGR dank CHIPS Act-Anreizen, die neue Back-End-Fabs finanzieren.[2]U.S. Department of Commerce, "CHIPS for America Announces up to $300 million in Funding to Boost U.S. Semiconductor Packaging," commerce.gov Versorgungsengpässe bei ABF-Substraten und Exportbeschränkungen für fortschrittliche Werkzeuge katalysieren geografische Diversifizierung und Materialinnovation.

Wichtige Erkenntnisse des Berichts

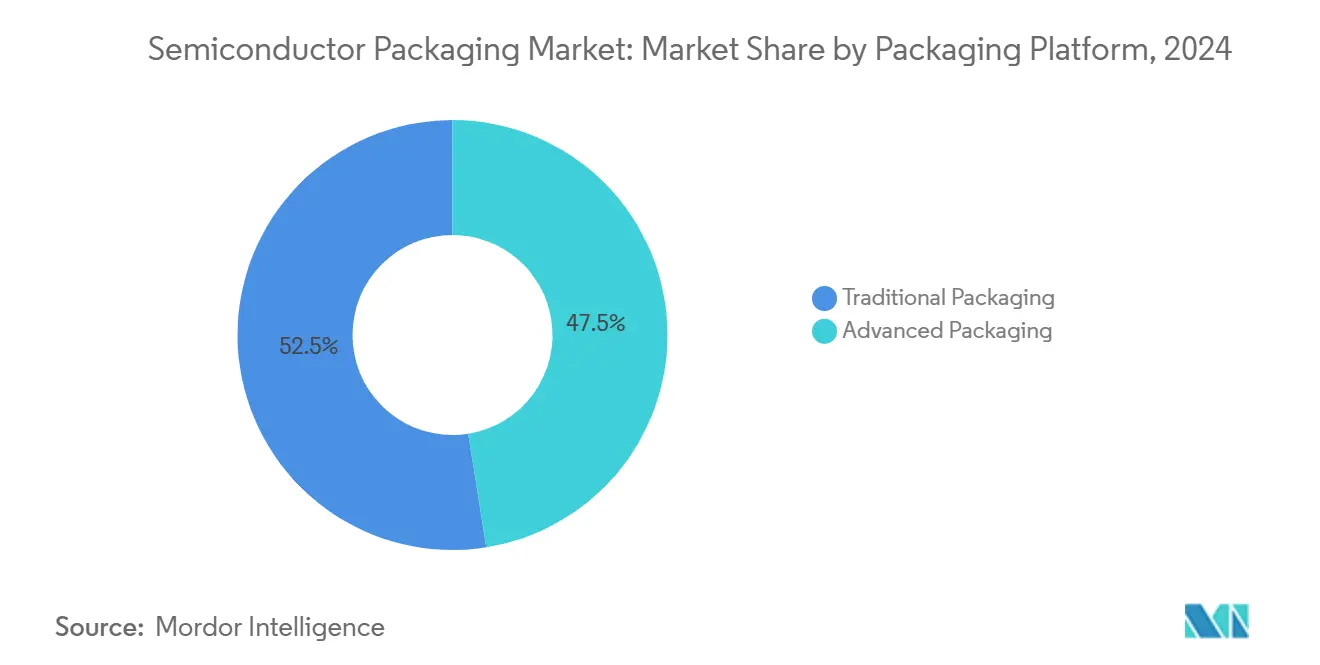

- Nach Packaging-Plattform hielten traditionelle Formate 52,5 % des Halbleiterpackaging-Marktanteils im Jahr 2024, während Fan-Out WLP voraussichtlich mit 12,3 % CAGR bis 2030 expandieren wird.

- Nach Endverbraucherindustrie führte Unterhaltungselektronik mit 43,8 % Umsatzanteil der Halbleiterpackaging-Marktgröße im Jahr 2024; Automotive zeigt das schnellste Wachstum mit 10,3 % CAGR bis 2030.

- Nach Wafer-Größe: 300 mm treibt Effizienz, eroberte 74,0 % des Halbleiterpackaging-Marktanteils im Jahr 2024, während Panel-Format aufkommt und Panel-Level-Verarbeitung auf Substraten von 450 mm oder mehr das am schnellsten wachsende Segment mit 12,5 % CAGR bis 2030 darstellt

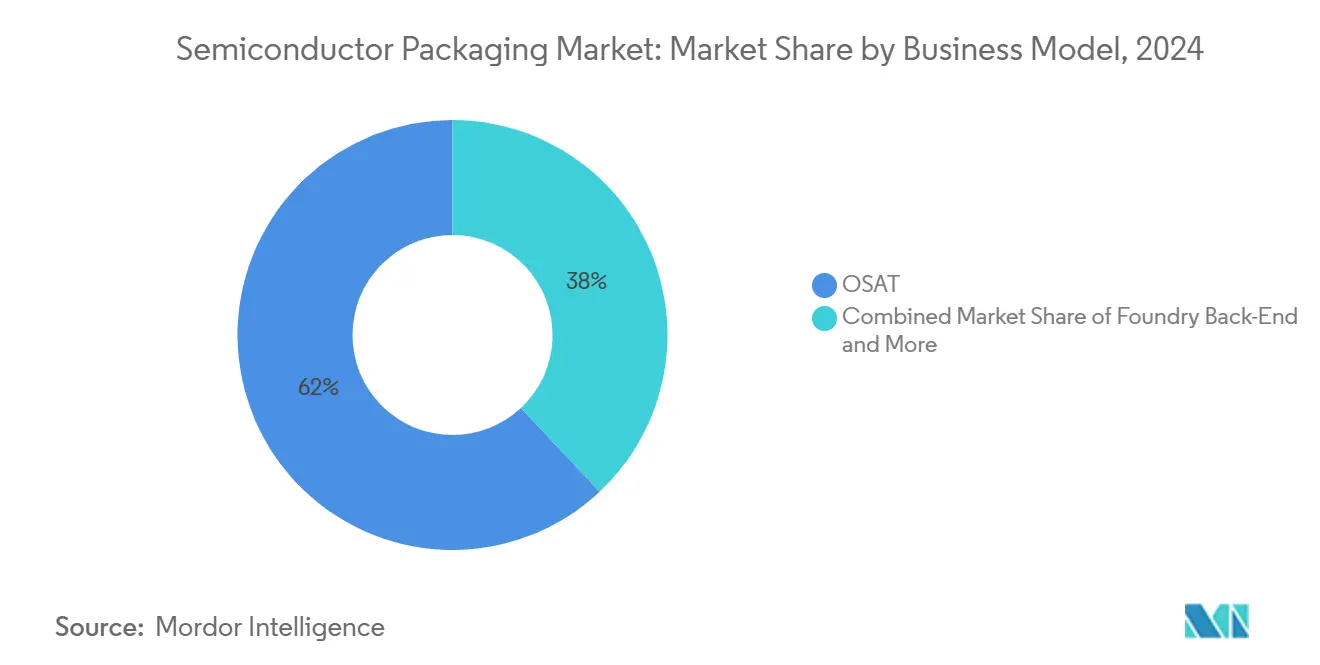

- Nach Geschäftsmodell kontrollierte das OSAT-Segment 62,0 % des globalen Halbleiterpackaging-Marktanteils im Jahr 2024, während Foundry-Back-End-Services mit 10,9 % CAGR steigen.

- Nach Packaging-Material trugen organische ABF-Substrate 41,5 % Umsatz im Jahr 2024 und untermauern das Mainstream-Flip-Chip-Ökosystem

- Nach Geografie hielt Asien 53,0 % des Halbleiterpackaging-Markts im Jahr 2024; Nordamerika ist für eine 11,1 % CAGR bis 2030 positioniert.

- ASE, Amkor und JCET machten gemeinsam mehr als 30 % Anteil am Advanced-Technology-Umsatz im Jahr 2024 aus, was Skalenvorteile bei Hybrid Bonding und SiP-Produktion widerspiegelt

Globale Halbleiterpackaging-Markttrends und Einblicke

Treiber-Impact-Analyse

| Treiber | (~) % Auswirkung auf CAGR-Prognose | Geografische Relevanz | Auswirkungszeithorizont |

|---|---|---|---|

| KI-Beschleuniger-Boom treibt 2,5D/3D-Interposer | +2.8% | Global (Taiwan, USA, China) | Mittelfristig (2-4 Jahre) |

| Elektrifizierte Fahrzeug-Leistungspackages | +1.9% | Nordamerika & APAC | Langfristig (≥4 Jahre) |

| US-EU-CHIPS-Anreize schaffen lokale Back-End-Fabs | +1.4% | Nordamerika & EU | Langfristig (≥4 Jahre) |

| 5G RF-SiP-Nachfrage in China & Korea | +1.2% | APAC-Kern | Kurzfristig (≤2 Jahre) |

| Panel-Level Packaging für kostengünstiges IoT | +0.9% | Global (APAC-Hubs) | Mittelfristig (2-4 Jahre) |

| Chiplet-Architekturen treiben hochdichte Interposer | +1.6% | Global (US-Design, Taiwan-Fertigung) | Mittelfristig (2-4 Jahre) |

| Quelle: Mordor Intelligence | |||

KI-Beschleuniger-Boom treibt 2,5D/3D-Interposer

TSMCs CoWoS-Kapazität verdoppelt sich zwischen 2023 und 2024 von 120.000 auf 240.000 Einheiten, kann aber die Hyperscaler-Nachfrage noch immer nicht vollständig erfüllen. Die Kapazitätslücke stimuliert alternative Panel-Level-Abläufe und 3,5D-Stacking-Tests, die mehr als 6.000 mm² Silizium pro Package aggregieren. [3]James Morra, "Broadcom Bets on 3.5D Packaging Technology to Build Bigger AI Chips," Electronic Design, electronicdesign.com Advanced Packaging hat sich daher von einem Kostenfaktor zu einem strategischen Hebel für KI-Systemleistung entwickelt

Elektrifizierte Fahrzeug-Leistungspackages in den USA & Asien

onSemis EliteSiC-Plattform, ausgezeichnet von Volkswagen, veranschaulicht die Migration zu integrierten Leistungsmodulen mit überlegener Wärmeableitung. ROHMs 6-in-1-geformte SiC-Module liefern dreifache Leistungsdichte gegenüber vorherigen. Diese Innovationen konzentrieren sich auf US- und asiatische Lieferketten, die strenge Automobilqualifikationen erfüllen können.

US-EU-CHIPS-Anreize schaffen lokale Back-End-Fabs

Das CHIPS-Gesetz stellt 300 Millionen USD ausschließlich für Advanced-Packaging-F&E bereit und subventioniert Testlinien in Georgia, Kalifornien und Arizona. Intels 3,5-Milliarden-USD-Foveros-Standort in New Mexico verankert inländische 3D-Integrationskapazität. Vergleichbare Mittel in der EU zielen darauf ab, Automobil- und Verteidigungselektronik von asiatischen Versorgungsunterbrechungen zu befreien.

5G RF-SiP-Nachfrage in China & Korea

JCETs heterogenes RF-SiP für Leistungsverstärker erhöht die Integrationsdichte um das 1,5-fache gegenüber vorherigen Knoten. Während Premium-Handys Innovation aufrechterhalten, hat die Nachfrageschwäche bei Massen-Android das Einheitenwachstum gedämpft und Anbieter unter Druck gesetzt, Kostenstrukturen zu optimieren

Hemmfaktoren-Impact-Analyse

| Hemmfaktor | (~) % Auswirkung auf CAGR-Prognose | Geografische Relevanz | Auswirkungszeithorizont |

|---|---|---|---|

| ABF-Substrat-Versorgungskrise | -1.8% | Global (APAC akut) | Kurzfristig (≤2 Jahre) |

| Ausbeute-Herausforderungen bei 3D TSV/Hybrid Bonding | -1.3% | Global (Taiwan, Korea, USA) | Mittelfristig (2-4 Jahre) |

| Exportkontrollen für fortschrittliche Packaging-Werkzeuge nach China | -0.9% | China primär | Langfristig (≥4 Jahre) |

| Thermische Ableitung begrenzt Fan-Out WLP @ <5 nm | -0.7% | Global fortschrittliche Knoten | Mittelfristig (2-4 Jahre) |

| Quelle: Mordor Intelligence | |||

ABF-Substrat-Versorgungskrise

Nittobos 20%-Preiserhöhung im August 2025 offenbart systemische Materialknappheit, die besonders Flip-Chip-BGA-Linien betrifft. Begrenzte qualifizierte Kapazitäten in Taiwan und Japan verlängern Lieferzeiten und drängen OEMs zur Erforschung von Glas-Core- oder Silizium-Core-Alternativen.

Ausbeute-Herausforderungen bei 3D TSV/Hybrid Bonding

Kupfer-zu-Kupfer Hybrid-Bonding-Toleranzen unter 0,5 nm und TSV-Seitenverhältnisse jenseits von 10:1 multiplizieren Defektrisiken über gestapelte. NVIDIAs Blackwell-Programm erlitt Berichten zufolge Ausbeuteausfälle im Zusammenhang mit CoWoS-L thermomechanischem Stress.

Segmentanalyse

Nach Packaging-Plattform: Fortschrittliche Technologien treiben Wertmigration

Traditionelle Wire-Bond- und Lead-Frame-Angebote dominierten 2024 noch immer Lieferungen mit 52,5 % Halbleiterpackaging-Marktanteil und stellen sicher, dass Unterhaltungselektronik und Industriegeräte erschwingliche Stücklistenkosten beibehalten. Fan-Out WLP übertrifft jedoch jedes andere Format mit 12,3 % CAGR und signalisiert den Wandel des Halbleiterpackaging-Markts zu substratfreien Umverteilungsschichten, die Z-Höhe schrumpfen und I/O-Dichte steigern. Flip-Chip überbrückt die Lücke durch Paarung feinpitchiger Bumps mit moderaten Kosten, während SiP- und PoP-Architekturen vertikales Stacking für platzbeschränkte Handsets ermöglichen.

Auf fortschrittlicher Front positionieren 2,5D-Interposer High-Bandwidth-Memory neben KI-Logik, und 3D-Stacks erschließen Latenzgewinne. Embedded-Die- und Panel-Level-Abläufe ziehen neue Marktteilnehmer an, die auf IoT-Preispunkte fokussiert sind, und demonstrieren, dass sich der Halbleiterpackaging-Markt in Premium-Performance-Knoten und Ultra-Low-Cost-Volumenspiele spaltet. Im Gegensatz dazu liefern Panel-Level-Linien unter 0,10 USD pro Pin, ein Verhältnis, das divergierende Kostenstrukturen unterstreicht. Infolgedessen haben Ausrüstungshersteller ihre Portfolios segmentiert: Hochpräzisions-Bonder-Cluster für 3 µm Ausrichtung koexistieren mit Large-Panel-MOLD-Linien für IoT-Tags. Eine solche Bifurkation redefiniert die Anbieterpositionierung im Halbleiterpackaging-Markt.

Notiz: Segmentanteile aller einzelnen Segmente verfügbar beim Berichtskauf

Nach Packaging-Material: Organische Substrate dominieren bei Innovationsdruck

Organische ABF-Substrate trugen 41,5 % Umsatz im Jahr 2024 und untermauern das Mainstream-Flip-Chip-Ökosystem. Doch die Halbleiterpackaging-Marktgröße für Bonding-Drähte soll jährlich um 11,4 % wachsen, da Automobil- und Industriesektoren die Lebensdauer bewährter Aluminium- und Gold-Draht-Packages verlängern. Leadframes bestehen in Leistungsanwendungen, die Kupfer-Heat-Spreader-Performance schätzen. Verkapselungsharze haben sich zu wärmeleitfähigen Graden entwickelt und unterstützen nächste Generation SiC- und GaN-Module.

Glassubstrate könnten organische Builds nach 2027 ersetzen. Intel- und Samsung-Prototypen zeigen 40 % Via-Pitch-Reduktion und nahezu null CTE-Fehlanpassung, was Verwerfung in 3D-Stacks reduziert. Thermal Interface Materials integrieren nun Nano-Diamant-Füllstoffe und reduzieren Junction-to-Case-Widerstand um 30 % in 1.200 V Traktionswechselrichtern. Goldpreisspitzen komprimierten Margen für Display-Driver-IC-Packaging 2025 und motivierten Migration zu Kupfersäulen-Bumps

Nach Wafer-Größe: 300 mm treibt Effizienz, während Panel-Format aufkommt

Das 300-mm-Wafer-Format eroberte 74,0 % des Halbleiterpackaging-Marktanteils im Jahr 2024 und bestätigt seinen Status als bevorzugte Wahl für fortschrittliche Back-End-Abläufe, die Verarbeitungseffizienz mit Front-End-Werkzeugkompatibilität ausbalancieren. Kleinere Wafer von 200 mm oder weniger bleiben für Legacy-Analog-, Sensor- und Leistungslinien viable, wo Umwandlungskosten Produktivitätsgewinne überwiegen. Größere Formate ermöglichen Skaleneffekte, die zunehmend kritisch sind, da Gerätezahlen in Smartphones, PCs und industriellen IoT-Knoten steigen.

Panel-Level-Verarbeitung auf Substraten von 450 mm oder mehr stellt das am schnellsten wachsende Segment mit 12,5 % CAGR bis 2030 dar und ist positioniert, die Halbleiterpackaging-Marktgröße durch Reduzierung des Pro-Einheit-Materialverbrauchs und der Zykluszeiten zu erhöhen. Verwerfungskontrolle, Inline-Ausbeute-Metrologie und Ausrüstungsstandardisierung bleiben die Haupthürden und erfordern gemeinsame Entwicklungsanstrengungen zwischen Werkzeugherstellern und Hochvolumen-Packaging-Häusern.

Nach Geschäftsmodell: OSAT-Führung sieht sich Foundry-Herausforderung gegenüber

OSATs behielten 62,0 % des Halbleiterpackaging-Marktanteils im Jahr 2024 aufgrund breiter Kundenlisten und globaler Präsenz. Doch Foundry-Back-End-Expansion mit 10,9 % CAGR signalisiert vertikale Integration. TSMCs Wafer Manufacturing 2.0 verschmilzt Litho, Test und CoWoS unter einem Angebot und verwischt OSAT-Grenzen.

Als Antwort zielt ASE auf 1,6 Milliarden USD Advanced-Packaging-Umsatz 2025 über strategische Capex und Co-Design mit System-OEMs reuters.com. Start-ups wie Chipletz fokussieren auf servicierbare zugängliche Märkte, wo maßgeschneidertes Interposer-Design mit KI-Inferenzkarten übereinstimmt und Nischenpenetrationsstrategien illustriert.

Notiz: Segmentanteile aller einzelnen Segmente verfügbar beim Berichtskauf

Nach Endverbraucherindustrie: Unterhaltungselektronik führt, während Automotive beschleunigt

Smartphones, Tablets und PCs sicherten einen 43,8 % Anteil des Halbleiterpackaging-Markts im Jahr 2024, da OEMs Formfaktoren aktualisierten und generative KI-On-Device-Fähigkeiten einführten. Dennoch zeigt die Automotive-Vertikale die höchste CAGR mit 10,3 % auf der Basis von EV-Wechselrichter- und ADAS-Domain-Controller-Inhaltswachstum.

Automotive-grade Leistungsmodule erzielen ASPs fünfmal höher als mobile SoCs und erweitern die Halbleiterpackaging-Marktgröße überproportional zu Stückzahlvolumen. Kommunikationsinfrastruktur trägt RF-SiP-Nachfrage bei, während Rechenzentrum-HPC die fortschrittlichsten Architekturen steuert und den Kreis zwischen KI-Algorithmus-Roadmaps und physischen Integrationsentscheidungen schließt.

Geografieanalyse

Asien eroberte 53,0 % des Halbleiterpackaging-Markts im Jahr 2024, zementiert durch Taiwans CoWoS-Monopol und Chinas Skalierung in Wire-Bond-Assembly. JCETs RMB 4,4 Milliarden Automotive-Werk in Jiangsu fördert lokale Kompetenz in SiC-Leistungspackages. Südkorea profitiert von memory-zentrischem SiP, während Japan zentrale Substratchemien kontrolliert und einen eng vernetzten regionalen Cluster verstärkt.

Nordamerikas Halbleiterpackaging-Markt wird voraussichtlich 11,1 % CAGR bis 2030 erreichen. CHIPS Act-Anreize sammeln 300 Millionen USD für F&E-Linien und schaffen Hubs in Arizona, New Mexico und Kalifornien. Partnerschaften wie TSMC-Amkor in Arizona bauen komplette Back-End-Ökosysteme nahe zu führenden Wafer-Fabs auf. Kanada kultiviert Photonik-Packaging, und Mexiko bietet kostengünstige Endtests für Verbraucher-ASICs.

Europa positioniert sich um Automotive- und Industriestärke. Deutsche Tier-1s co-entwickeln doppelseitig gekühlte SiC-Module, die 9 kW/L Wechselrichterdichte anstreben und Nischen-OSAT-Investitionen katalysieren. Die Niederlande drängen Hochfrequenz-optische Transceiver-Packaging, das mit Vertical-Cavity Surface-Emitting Laser (VCSEL)-Adoption übereinstimmt. Naher Osten und Afrika bleiben aufstrebend, lagern primär Assembly an asiatische Hubs aus, planen aber inländische Linien für sichere IoT- und Verteidigungselektronik unter souveränen Mandaten.

Wettbewerbslandschaft

Wettbewerbsintensität dreht sich von Preis zu Technologie. TSMC nutzt Foundry-Know-how zur Dominierung von 2,5D-Interposern, während Samsung H-cube einsetzt, um Memory und Logic für mobile KI zu mischen. ASE und Amkor verteilen Risiken über 40+ Anlagen und fokussieren auf Ausbeute-Learning und Design-for-Manufacturability-Services. JCET skaliert SiP-Linien mit Automotive AEC-Q100-Abläufen. Intels Foveros-Werk verkörpert einen strategischen Sprung zur Wiedererlangung der Packaging-Führung und bietet 50 µm Die-to-Die-Pitch für Client- und Rechenzentrum-Plattformen.

Markteintrittsbarrieren umfassen Capex-Intensität, Substrat-Versorgungssicherheit und Kunden-Co-Development-Lock-ins. Folglich spiegelt Konsolidierung durch M&A-z.B. Empyreans Kauf von Xpeedic-einen Versuch wider, EDA- und Packaging-IP unter einem Dach zu aggregieren

Halbleiterpackaging-Industrieführer

-

ASE Technology Holding Co., Ltd.

-

Amkor Technology, Inc.

-

JCET Group Co., Ltd.

-

Siliconware Precision Industries Co., Ltd.

-

Powertech Technology Inc.

- *Haftungsausschluss: Hauptakteure in keiner bestimmten Reihenfolge sortiert

Aktuelle Industrieentwicklungen

- Juni 2025: ASE und AMD partnern zur Steigerung der Rechenzentrumseffizienz um 50 % bei 6,5 % Leistungsreduzierung, bewerten Instinct MI300 GPUs für KI-Arbeitslasten

- Juni 2025: Infineon stellt trench-basierte SiC Super-Junction MOSFETs vor, zielt auf Traktionswechselrichter mit ersten 1.200 V Geräten in ID-PAK-Packages

- Mai 2025: ROHM veröffentlicht 4-in-1 und 6-in-1 SiC-geformte Module, die Leistungsdichte verdreifachen und Platinenfläche um 52 % reduzieren

- April 2025: ASE demonstriert co-packaged Optics, die Verbindungsenergie auf <5 pJ/bit reduzieren bei 24,9 % Rechenzentrum-Bandbreiten-CAGR-Prognose

Globaler Halbleiterpackaging-Marktberichtsumfang

Halbleiterpackaging bezieht sich auf ein Gehäuse, das ein oder mehrere diskrete Halbleiterbauelemente oder integrierte Schaltungen aus Kunststoff-, Keramik-, Metall- oder Glasgehäuse enthält. Packaging schützt ein elektronisches System vor Hochfrequenz-Rausch-Emissionen, elektrostatischer Entladung, mechanischen Schäden und Kühlung. Der Aufstieg der Halbleiterindustrie weltweit ist einer der Hauptfaktoren, die das Wachstum des Halbleiterpackaging-Markts antreiben. Die kontinuierlichen Fortschritte in Bezug auf Integration, Energieeffizienz und Produkteigenschaften aufgrund der wachsenden Nachfrage über verschiedene Endverbraucher-Vertikalen der Industrie und die Verwendung von Packaging zur Verbesserung der Leistung, Zuverlässigkeit und Kosteneffektivität elektronischer Systeme beschleunigen das Marktwachstum.

Der Bericht verfolgt die Verkäufe von Halbleiterpackaging global, um den Marktumsatz für den globalen Advanced-Packaging- und Traditional-Packaging-Markt zu bewerten. Verschiedene Advanced-Packaging-Plattformen werden im Bericht berücksichtigt, einschließlich Flip-Chip, Fan-In, Embedded-Die, 3D-Stacking und Fan-Out-Packaging, die in mehreren Endverbraucheranwendungen wie Unterhaltungselektronik, Medizingeräte, Kommunikation und Telekom und Automotive verwendet werden. Die Wettbewerbslandschaft wurde aufgenommen, um Packaging-Penetration zu berechnen und wie sich Akteure in organische und anorganische Wachstumsstrategien einbringen. Diese Unternehmen innovieren ihre Produkte, um ihren Marktanteil und ihre Rentabilität zu erhöhen. Darüber hinaus fokussiert der Bericht auf die Analyse makroökonomischer Faktoren im Markt.

Der Halbleiterpackaging-Markt ist segmentiert nach Packaging-Plattform (Advanced Packaging [Flip-Chip, SIP, 2,5D/3D, Embedded-Die, Fan-In Wafer Level Packaging (FI-WLP) und Fan-Out Wafer Level Packaging (FO-WLP)] und Traditional Packaging), Endverbraucherindustrie (Unterhaltungselektronik, Luft- und Raumfahrt und Verteidigung, Medizingeräte, Kommunikation und Telekom, Automotive und Energie und Beleuchtung) und Geografie (USA, China, Taiwan, Korea, Japan und Europa). Der Bericht bietet Marktgrößen und Prognosen in Wertangaben (USD) für alle diese Segmente.

| Advanced Packaging | Flip-Chip |

| Fan-Out WLP | |

| Fan-In WLP | |

| 2,5D / 3D IC | |

| Embedded-Die | |

| SiP / PoP | |

| Panel-Level Packaging | |

| Traditional Packaging | Wire-Bond |

| Leadframe | |

| QFN / QFP / SOP |

| Organische Substrate |

| Leadframes |

| Bonding-Drähte |

| Verkapselungsharze |

| Keramikpackages |

| Lötkugeln und Bumps |

| Die-Attach und TIMs |

| ≤ 200 mm |

| 300 mm |

| ≥ 450 mm / Panel |

| OSAT |

| Foundry Back-End |

| IDM In-house |

| Unterhaltungselektronik | Smartphones und Wearables | |

| Computing / Rechenzentrum | ||

| Automotive und Mobilität | ADAS / EV Power | |

| Kommunikation und Telekom | 5G-Infrastruktur | |

| Luft- und Raumfahrt und Verteidigung | ||

| Medizin- und Gesundheitsgeräte | ||

| Industrie und Energie (LED / Power) | ||

| Nordamerika | USA |

| Kanada | |

| Mexiko | |

| Südamerika | Brasilien |

| Rest von Südamerika | |

| Europa | Deutschland |

| Frankreich | |

| Vereinigtes Königreich | |

| Italien | |

| Niederlande | |

| Nordische Länder | |

| Rest von Europa | |

| Naher Osten und Afrika | Israel |

| Türkei | |

| GCC | |

| Südafrika | |

| Rest von Naher Osten und Afrika | |

| APAC | China |

| Taiwan | |

| Südkorea | |

| Japan | |

| Indien | |

| Singapur | |

| Australien | |

| Neuseeland | |

| Rest von APAC |

| Nach Packaging-Plattform | Advanced Packaging | Flip-Chip | |

| Fan-Out WLP | |||

| Fan-In WLP | |||

| 2,5D / 3D IC | |||

| Embedded-Die | |||

| SiP / PoP | |||

| Panel-Level Packaging | |||

| Traditional Packaging | Wire-Bond | ||

| Leadframe | |||

| QFN / QFP / SOP | |||

| Nach Packaging-Material | Organische Substrate | ||

| Leadframes | |||

| Bonding-Drähte | |||

| Verkapselungsharze | |||

| Keramikpackages | |||

| Lötkugeln und Bumps | |||

| Die-Attach und TIMs | |||

| Nach Wafer-Größe | ≤ 200 mm | ||

| 300 mm | |||

| ≥ 450 mm / Panel | |||

| Nach Geschäftsmodell | OSAT | ||

| Foundry Back-End | |||

| IDM In-house | |||

| Nach Endverbraucherindustrie | Unterhaltungselektronik | Smartphones und Wearables | |

| Computing / Rechenzentrum | |||

| Automotive und Mobilität | ADAS / EV Power | ||

| Kommunikation und Telekom | 5G-Infrastruktur | ||

| Luft- und Raumfahrt und Verteidigung | |||

| Medizin- und Gesundheitsgeräte | |||

| Industrie und Energie (LED / Power) | |||

| Nach Geografie | Nordamerika | USA | |

| Kanada | |||

| Mexiko | |||

| Südamerika | Brasilien | ||

| Rest von Südamerika | |||

| Europa | Deutschland | ||

| Frankreich | |||

| Vereinigtes Königreich | |||

| Italien | |||

| Niederlande | |||

| Nordische Länder | |||

| Rest von Europa | |||

| Naher Osten und Afrika | Israel | ||

| Türkei | |||

| GCC | |||

| Südafrika | |||

| Rest von Naher Osten und Afrika | |||

| APAC | China | ||

| Taiwan | |||

| Südkorea | |||

| Japan | |||

| Indien | |||

| Singapur | |||

| Australien | |||

| Neuseeland | |||

| Rest von APAC | |||

Wichtige im Bericht beantwortete Fragen

Wie hoch ist der aktuelle Wert des Halbleiterpackaging-Markts?

Der Halbleiterpackaging-Markt ist mit 49,88 Milliarden USD im Jahr 2025 bewertet und wird voraussichtlich bis 2030 81,22 Milliarden USD erreichen.

Welche Packaging-Technologie wächst am schnellsten?

Fan-Out Wafer-Level Packaging ist die am schnellsten wachsende Plattform mit 12,3 % CAGR bis 2030.

Warum sind ABF-Substrate ein Engpass?

ABF-Substrate werden hauptsächlich in Taiwan und Japan produziert, und Versorgungsengpässe haben Preiserhöhungen von 20 % verursacht und begrenzen Flip-Chip-Kapazitätserweiterung.

Wie wirkt sich das CHIPS-Gesetz auf Packaging aus?

Das CHIPS-Gesetz stellt 300 Millionen USD für inländische Advanced-Packaging-F&E bereit, fördert neue Fabs in Arizona, Kalifornien und New Mexico und erhöht Nordamerikas CAGR auf 11,1 %.

Welcher Endverbrauchssektor wird das höchste Wachstum sehen?

Automotive-Anwendungen werden das höchste Wachstum mit 10,3 % CAGR erreichen, angetrieben von Elektrofahrzeug-Leistungselektronik und ADAS-Nachfrage.

Wie beeinflussen Chiplet-Architekturen Packaging-Design?

Offene Standards wie UCIe 2.0 ermöglichen heterogene Chiplets und drängen Packaging zu hochdichten Interposern und Hybrid Bonding für höhere Bandbreite und niedrigere Latenz.

Seite zuletzt aktualisiert am: