Tamanho e Participação do Mercado de Encapsulamento de Semicondutores

Análise do Mercado de Encapsulamento de Semicondutores pela Mordor Intelligence

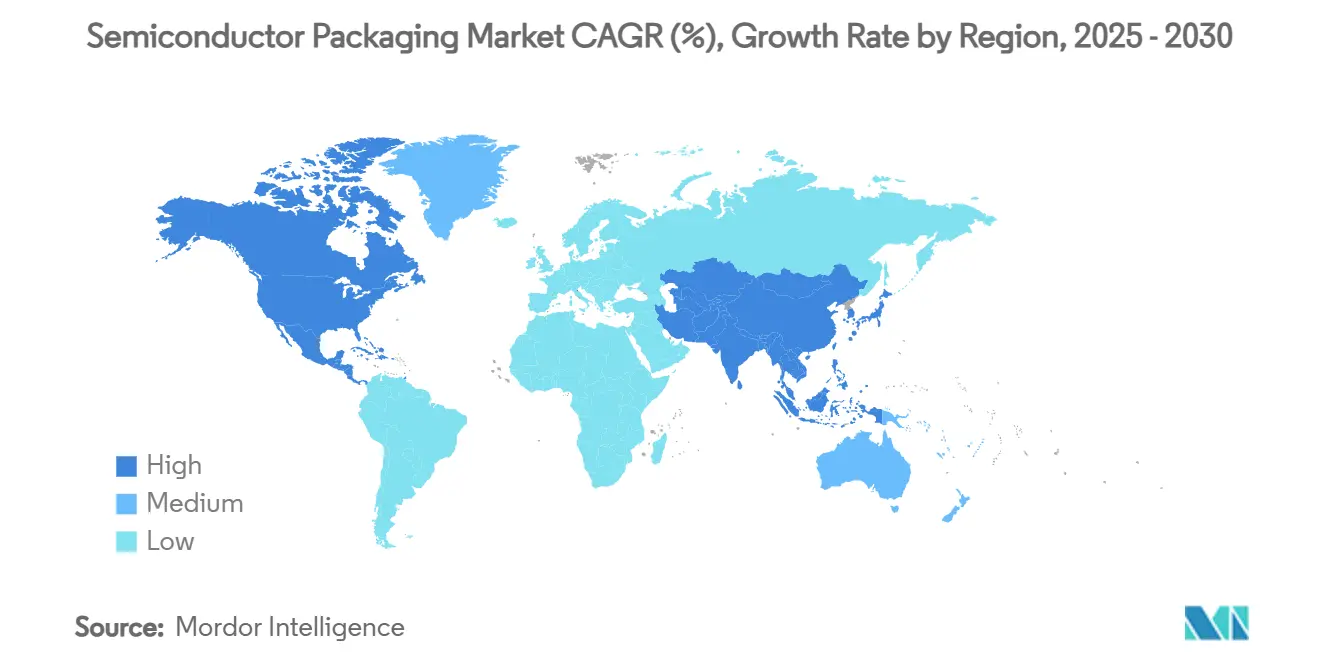

O tamanho do mercado de encapsulamento de semicondutores foi de USD 49,88 bilhões em 2025 e está projetado para atingir USD 81,22 bilhões até 2030, avançando a uma TCAC de 10,24% no período 2025-2030. [1]Cheng Ting-Fang, "TSMC moves closer to next-gen packaging for Nvidia, Google AI chips," Nikkei Asia, asia.nikkei.comUma mudança da montagem baseada em custos para a integração crítica de desempenho sustenta esse crescimento. A demanda por arquiteturas 2.5D e 3D aumentou drasticamente à medida que as cargas de trabalho de IA exigem memória de alta largura de banda e caminhos térmicos superiores. O volume permanece ancorado em formatos tradicionais de wire-bond e lead-frame, porém a criação de valor está migrando para encapsulamento fan-out em nível de wafer (WLP) e interposers habilitados para chiplet. A eletrificação automotiva apoia expansão de dois dígitos em módulos de alta densidade de potência, enquanto os ciclos de renovação de smartphones e PCs sustentam volumes básicos no segmento de consumo. Regionalmente, a Ásia comanda mais da metade da produção global, mas a América do Norte registra a maior TCAC graças aos incentivos do CHIPS Act que financiam novas fábricas de back-end.[2]U.S. Department of Commerce, "CHIPS for America Announces up to $300 million in Funding to Boost U.S. Semiconductor Packaging," commerce.gov Gargalos de fornecimento em substratos ABF e restrições de exportação em ferramentas avançadas estão catalisando a diversificação geográfica e inovação de materiais.

Principais Conclusões do Relatório

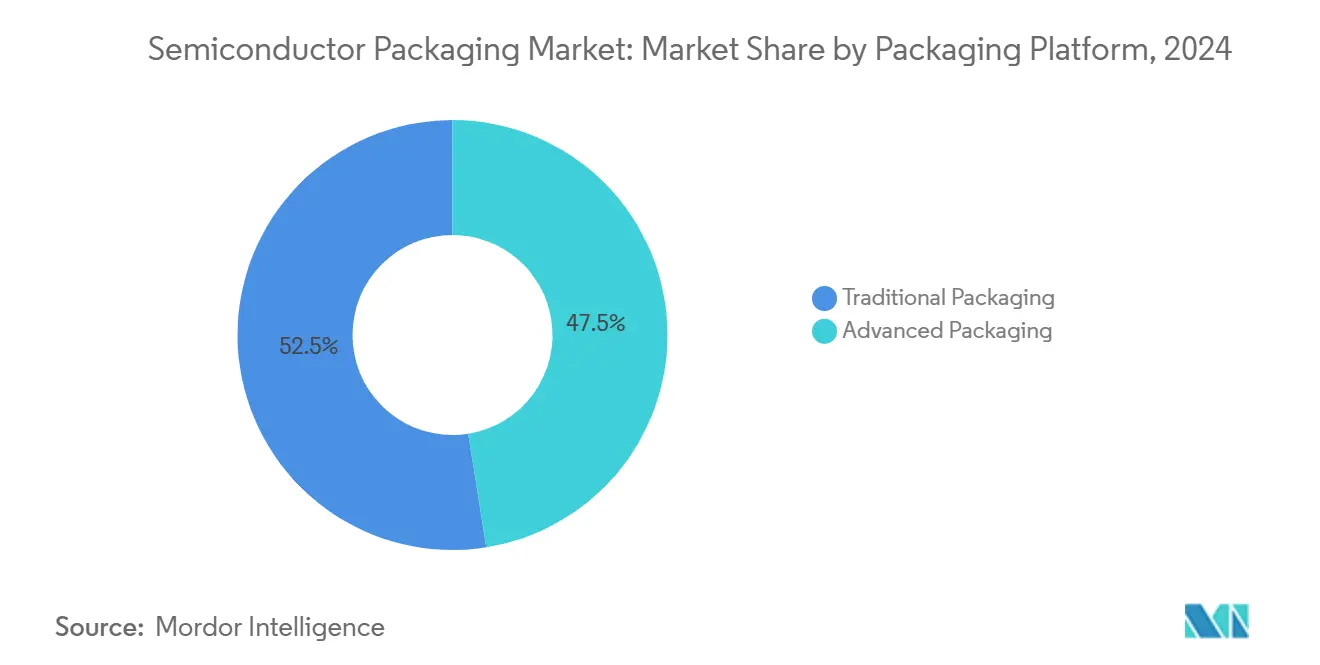

- Por plataforma de encapsulamento, os formatos tradicionais detiveram 52,5% da participação do mercado de encapsulamento de semicondutores em 2024, enquanto o fan-out WLP está previsto para expandir a uma TCAC de 12,3% até 2030.

- Por indústria de usuário final, eletrônicos de consumo lideraram com 43,8% de participação na receita do tamanho do mercado de encapsulamento de semicondutores em 2024; automotivo está no ritmo de crescimento mais rápido a 10,3% TCAC até 2030.

- Por Tamanho de Wafer: 300 mm impulsiona eficiência, capturou 74,0% da participação do mercado de encapsulamento de semicondutores em 2024, enquanto o formato de painel emerge e o processamento em nível de painel em substratos de 450 mm ou mais representa o segmento de crescimento mais rápido a uma TCAC de 12,5% até 2030

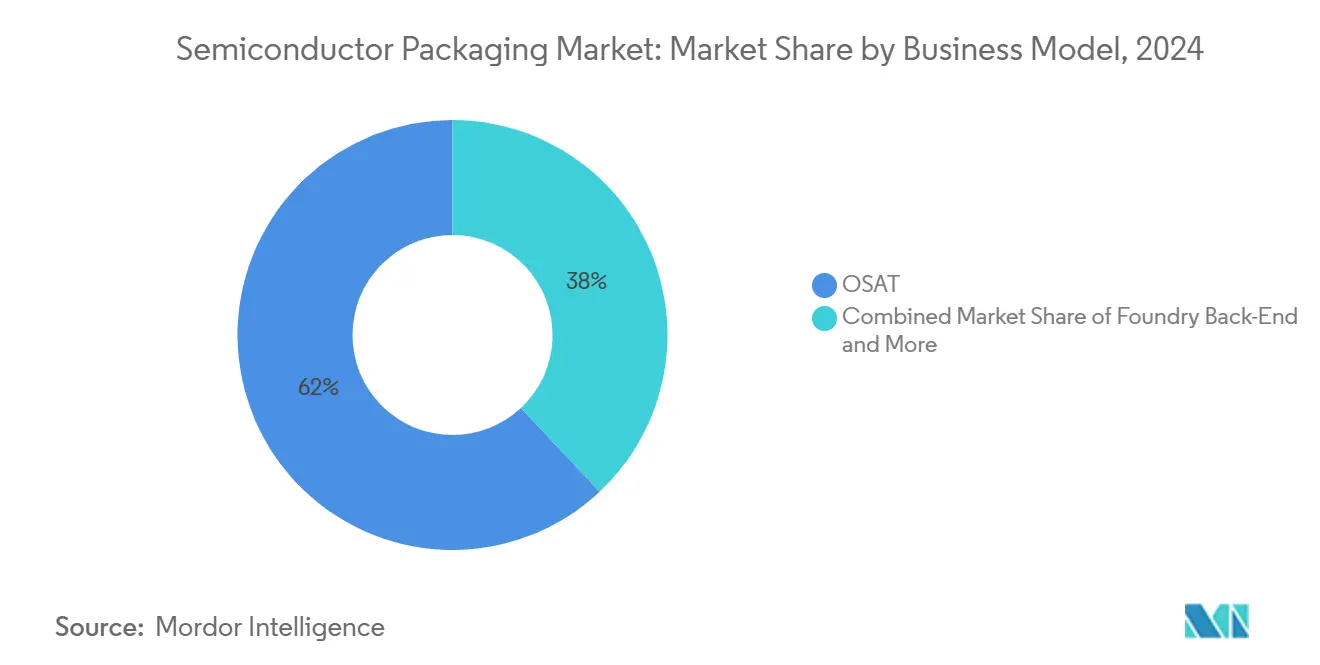

- Por modelo de negócio, o segmento OSAT controlou 62,0% da participação global do mercado de encapsulamento de semicondutores em 2024 enquanto os serviços de back-end de foundry estão aumentando a 10,9% TCAC.

- Por Material de Encapsulamento, substratos ABF orgânicos carregaram 41,5% da receita em 2024, sustentando o ecossistema flip-chip mainstream

- Por geografia, a Ásia deteve 53,0% do mercado de encapsulamento de semicondutores em 2024; a América do Norte está posicionada para uma TCAC de 11,1% até 2030.

- ASE, Amkor e JCET conjuntamente representaram mais de 30% de participação da receita de tecnologia avançada em 2024, refletindo vantagens de escala na produção de hybrid bonding e SiP

Tendências e Insights do Mercado Global de Encapsulamento de Semicondutores

Análise de Impacto dos Direcionadores

| Direcionador | (~) % Impacto na Previsão TCAC | Relevância Geográfica | Cronograma de Impacto |

|---|---|---|---|

| Boom de aceleradores de IA impulsionando interposers 2.5D/3D | +2.8% | Global (Taiwan, EUA, China) | Médio prazo (2-4 anos) |

| Pacotes de energia para veículos eletrificados | +1.9% | América do Norte & APAC | Longo prazo (≥4 anos) |

| Incentivos CHIPS EUA-UE criando fábricas locais de back-end | +1.4% | América do Norte & UE | Longo prazo (≥4 anos) |

| Demanda de RF-SiP 5G na China e Coreia | +1.2% | Núcleo APAC | Curto prazo (≤2 anos) |

| Encapsulamento em nível de painel para IoT de baixo custo | +0.9% | Global (hubs APAC) | Médio prazo (2-4 anos) |

| Arquiteturas chiplet alimentando interposers de alta densidade | +1.6% | Global (design EUA, mfg. Taiwan) | Médio prazo (2-4 anos) |

| Fonte: Mordor Intelligence | |||

Boom de aceleradores de IA impulsionando interposers 2.5D/3D

A capacidade CoWoS da TSMC está dobrando de 120.000 para 240.000 unidades entre 2023 e 2024, mas ainda não consegue atender totalmente à demanda de hyperscalers. A lacuna de capacidade está estimulando fluxos alternativos em nível de painel e testes de empilhamento 3.5D que agregam mais de 6.000 mm² de silício por pacote. [3]James Morra, "Broadcom Bets on 3.5D Packaging Technology to Build Bigger AI Chips," Electronic Design, electronicdesign.com O encapsulamento avançado passou de um centro de custo para uma alavanca estratégica para o desempenho de sistemas de IA

Pacotes de energia para veículos eletrificados nos Estados Unidos e Ásia

A plataforma EliteSiC da onsemi premiada pela Volkswagen exemplifica a migração para módulos de energia integrados com dissipação de calor superior. Os módulos SiC moldados 6-em-1 da ROHM entregam o triplo da densidade de potência dos anteriores. Essas inovações se concentram nas cadeias de suprimento dos EUA e asiáticas que podem atender à qualificação automotiva rigorosa.

Incentivos CHIPS EUA-UE criando fábricas locais de back-end

O CHIPS Act destina USD 300 milhões exclusivamente para P&D de encapsulamento avançado, subsidiando linhas de teste na Geórgia, Califórnia e Arizona. O site Foveros de USD 3,5 bilhões da Intel no Novo México ancora a capacidade de integração 3D doméstica. Fundos comparáveis na UE visam reduzir o risco de eletrônicos automotivos e de defesa de interrupções de fornecimento asiáticas.

Demanda de RF-SiP 5G na China e Coreia

O RF-SiP heterogêneo da JCET para amplificadores de potência eleva a densidade de integração 1,5× em relação aos nós anteriores. Enquanto smartphones premium sustentam a inovação, a suavidade da demanda Android de nível de massa temperou o crescimento de unidades, pressionando fornecedores a otimizar estruturas de custos

Análise de Impacto das Restrições

| Restrição | (~) % Impacto na Previsão TCAC | Relevância Geográfica | Cronograma de Impacto |

|---|---|---|---|

| Escassez de fornecimento de substrato ABF | -1.8% | Global (APAC agudo) | Curto prazo (≤2 anos) |

| Desafios de rendimento em TSV/hybrid bonding 3D | -1.3% | Global (Taiwan, Coreia, EUA) | Médio prazo (2-4 anos) |

| Controles de exportação em ferramentas de encapsulamento avançadas para a China | -0.9% | China primário | Longo prazo (≥4 anos) |

| Limites de dissipação térmica em fan-out WLP @ <5 nm | -0.7% | Nós avançados globais | Médio prazo (2-4 anos) |

| Fonte: Mordor Intelligence | |||

Escassez de fornecimento de substrato ABF

O aumento de preço de 20% da Nittobo em agosto de 2025 expõe rigidez sistêmica do material que afeta particularmente as linhas flip-chip BGA. Capacidade qualificada limitada em Taiwan e Japão prolonga prazos de entrega e empurra OEMs a explorar alternativas de núcleo de vidro ou núcleo de silício.

Desafios de rendimento em TSV/hybrid bonding 3D

Tolerâncias de hybrid bonding cobre-para-cobre sob 0,5 nm e proporções de aspecto TSV além de 10:1 multiplicam riscos de defeitos em empilhados. O programa Blackwell da NVIDIA supostamente atingiu escapes de rendimento ligados ao estresse termomecânico CoWoS-L.

Análise de Segmento

Por Plataforma de Encapsulamento: Tecnologias avançadas impulsionam migração de valor

As ofertas tradicionais de wire-bond e lead-frame ainda dominaram os embarques com 52,5% de participação do mercado de encapsulamento de semicondutores em 2024, garantindo que eletrônicos de consumo e dispositivos industriais mantenham custos acessíveis de lista de materiais. No entanto, Fan-out WLP supera todos os outros formatos a uma TCAC de 12,3%, sinalizando o movimento do mercado de encapsulamento de semicondutores em direção a camadas de redistribuição sem substrato que reduzem a altura z e aumentam a densidade de I/O. Flip-chip preenche a lacuna ao combinar bumps de pitch fino com custo moderado, enquanto arquiteturas SiP e PoP permitem empilhamento vertical para smartphones com restrições de espaço.

Na frente avançada, interposers 2.5D posicionam memória de alta largura de banda adjacente à lógica de IA, e pilhas 3D desbloqueiam ganhos de latência. Fluxos de die embebido e nível de painel atraem novos participantes focados em pontos de preço de IoT, demonstrando que o mercado de encapsulamento de semicondutores está se dividindo em nós de desempenho premium e jogadas de volume de ultra baixo custo. Em contraste, linhas de nível de painel entregam sub-USD 0,10 por pino, uma proporção que ressalta estruturas de custos divergentes. Como resultado, fabricantes de equipamentos segmentaram seus portfólios: clusters de bonder de alta precisão para alinhamento de 3 µm coexistem com grandes linhas MOLD de painel voltadas para tags IoT. Tal bifurcação redefine o posicionamento de fornecedores dentro do mercado de encapsulamento de semicondutores.

Nota: Participações de segmentos de todos os segmentos individuais disponíveis mediante compra do relatório

Por Material de Encapsulamento: Substratos orgânicos dominam em meio à pressão de inovação

Substratos ABF orgânicos carregaram 41,5% da receita em 2024, sustentando o ecossistema flip-chip mainstream. Ainda assim, o tamanho do mercado de encapsulamento de semicondutores para fios de ligação está definido para crescer 11,4% anualmente à medida que os setores automotivo e industrial estendem a vida de pacotes de fio de alumínio e ouro comprovados. Leadframes persistem em aplicações de energia que valorizam o desempenho do dissipador de calor de cobre. Resinas de encapsulamento progrediram para graus de alta condutividade térmica, apoiando módulos SiC e GaN de próxima geração.

Substratos de vidro poderiam deslocar construções orgânicas após 2027. Protótipos da Intel e Samsung mostram redução de pitch de via de 40% e incompatibilidade CTE próxima de zero, diminuindo o empenamento em pilhas 3D. Materiais de interface térmica agora integram preenchimentos de nano-diamante, cortando a resistência junction-to-case em 30% em inversores de tração de 1.200 V. Picos de preço do ouro comprimiram margens para encapsulamento IC de driver de display em 2025, motivando migração para bumps de coluna de cobre

Por Tamanho de Wafer: 300 mm impulsiona eficiência enquanto formato de painel emerge

O formato de wafer de 300 mm capturou 74,0% da participação do mercado de encapsulamento de semicondutores em 2024, confirmando seu status como a escolha preferida para fluxos avançados de back-end que equilibram eficiência de processamento com compatibilidade de ferramentas de front-end. Wafers menores de 200 mm ou menos permanecem viáveis para linhas analógicas, de sensores e de energia legadas onde custos de conversão superam ganhos de produtividade. Formatos maiores permitem economias de escala que são cada vez mais críticas à medida que contagens de dispositivos sobem em smartphones, PCs e nós IoT industriais.

O processamento em nível de painel em substratos de 450 mm ou mais representa o segmento de crescimento mais rápido a uma TCAC de 12,5% até 2030 e está posicionado para aumentar o tamanho do mercado de encapsulamento de semicondutores ao diminuir o consumo de material por unidade e tempos de ciclo. Controle de empenamento, metrologia de rendimento inline e padronização de equipamentos permanecem os principais obstáculos, exigindo esforços de desenvolvimento conjunto entre fabricantes de ferramentas e casas de encapsulamento de alto volume.

Por Modelo de Negócio: Liderança OSAT enfrenta desafio de foundry

OSATs mantiveram 62,0% da participação do mercado de encapsulamento de semicondutores em 2024 devido a amplos cadastros de clientes e pegadas globais. Ainda assim, a expansão de back-end de foundry a 10,9% TCAC sinaliza integração vertical. O Wafer Manufacturing 2.0 da TSMC combina litografia, teste e CoWoS sob uma cotação, borrando fronteiras OSAT.

Em resposta, a ASE visa receita de encapsulamento avançado de USD 1,6 bilhão em 2025 via capex estratégico e co-design com OEMs de sistema reuters.com. Start-ups como Chipletz focam em mercados acessíveis e serviceable onde design de interposer sob medida se alinha com placas de inferência de IA, ilustrando estratégias de penetração de nicho.

Nota: Participações de segmentos de todos os segmentos individuais disponíveis mediante compra do relatório

Por Indústria de Usuário Final: Eletrônicos de consumo lideram enquanto automotivo acelera

Smartphones, tablets e PCs garantiram uma participação de 43,8% do mercado de encapsulamento de semicondutores em 2024 à medida que OEMs renovaram fatores de forma e introduziram capacidades de IA generativa on-device. No entanto, o vertical automotivo registra a maior TCAC a 10,3% com base no crescimento de conteúdo de inversor EV e controlador de domínio ADAS.

Módulos de energia de grau automotivo comandam ASPs cinco vezes maiores que SoCs móveis, expandindo o tamanho do mercado de encapsulamento de semicondutores desproporcionalmente versus volumes unitários. A infraestrutura de comunicações contribui com demanda RF-SiP, enquanto HPC de data-center orienta as arquiteturas mais avançadas, fechando o ciclo entre roadmaps de algoritmos de IA e escolhas de integração física.

Análise Geográfica

A Ásia capturou 53,0% do mercado de encapsulamento de semicondutores em 2024, cimentada pelo monopólio CoWoS de Taiwan e escala da China em montagem wire-bond. A planta automotiva de RMB 4,4 bilhões da JCET em Jiangsu avança competência local em pacotes de energia SiC. A Coreia do Sul se beneficia de SiP centrado em memória, enquanto o Japão controla químicas de substrato essenciais, reforçando um cluster regional bem integrado.

O mercado de encapsulamento de semicondutores da América do Norte está projetado para registrar uma TCAC de 11,1% até 2030. Os incentivos do CHIPS Act acumulam USD 300 milhões para linhas de P&D, gerando hubs no Arizona, Novo México e Califórnia. Parcerias como TSMC-Amkor no Arizona constroem ecossistemas completos de back-end próximos a fábricas de wafer de ponta. O Canadá cultiva encapsulamento de fotônica, e o México oferece teste final de baixo custo para ASICs de consumo.

A Europa se posiciona em torno da força automotiva e industrial. Tier-1s alemãs co-desenvolvem módulos SiC resfriados dos dois lados visando densidade de inversor de 9 kW/L, catalisando investimento OSAT de nicho. Os Países Baixos empurram encapsulamento de transceptor óptico de alta frequência que se alinha com adoção de laser emissor de superfície de cavidade vertical (VCSEL). Oriente Médio e África permanecem emergentes, principalmente terceirizando montagem para hubs asiáticos ainda planejando linhas domésticas para eletrônicos seguros de IoT e defesa sob mandatos soberanos.

Cenário Competitivo

A intensidade competitiva gira do preço para a tecnologia. A TSMC aproveita know-how de foundry para dominar interposers 2.5D enquanto a Samsung emprega H-cube para misturar memória e lógica para IA móvel. ASE e Amkor espalham risco através de mais de 40 instalações, focando em aprendizado de rendimento e serviços de design-for-manufacturability. A JCET escala linhas SiP executando fluxos automotivos AEC-Q100. A planta Foveros da Intel incorpora um salto estratégico para recuperar liderança em encapsulamento, oferecendo pitch die-to-die de 50 µm para plataformas cliente e data-center.

Barreiras de entrada incluem intensidade de capex, segurança de fornecimento de substrato e lock-ins de co-desenvolvimento de clientes. Consequentemente, consolidação através de M&A-ex., compra da Xpeedic pela Empyrean-reflete uma tentativa de agregar EDA e IP de encapsulamento sob um teto

Líderes da Indústria de Encapsulamento de Semicondutores

-

ASE Technology Holding Co., Ltd.

-

Amkor Technology, Inc.

-

JCET Group Co., Ltd.

-

Siliconware Precision Industries Co., Ltd.

-

Powertech Technology Inc.

- *Isenção de responsabilidade: Principais participantes classificados em nenhuma ordem específica

Desenvolvimentos Recentes da Indústria

- Junho 2025: ASE e AMD fazem parceria para aumentar a eficiência de data-center em 50% enquanto reduzem energia em 6,5%, avaliando GPUs Instinct MI300 para cargas de trabalho de IA

- Junho 2025: Infineon revela MOSFETs SiC super-junction baseados em trench, visando inversores de tração com primeiros dispositivos de 1.200 V em pacotes ID-PAK

- Maio 2025: ROHM lança módulos SiC moldados 4-em-1 e 6-em-1 que triplicam a densidade de potência e reduzem área da placa em 52%

- Abril 2025: ASE demonstra ótica co-empacotada cortando energia de link para <5 pJ/bit em meio à previsão TCAC de largura de banda de data-center de 24,9%

Escopo do Relatório Global do Mercado de Encapsulamento de Semicondutores

Encapsulamento de semicondutores refere-se a um invólucro que contém um ou mais dispositivos semicondutores discretos ou circuitos integrados feitos de invólucro de plástico, cerâmica, metal ou vidro. O encapsulamento protege um sistema eletrônico da emissão de ruído de radiofrequência, descarga eletrostática, danos mecânicos e resfriamento. O aumento na indústria de semicondutores mundialmente é um dos principais fatores impulsionando o crescimento do mercado de encapsulamento de semicondutores. Os contínuos avanços em termos de integração, eficiência energética e características do produto devido à crescente demanda através de vários verticais de usuário final da indústria e o uso de encapsulamento para melhorar o desempenho, confiabilidade e custo-efetividade de sistemas eletrônicos aceleram o crescimento do mercado.

O relatório rastreia as vendas de encapsulamento de semicondutores globalmente para avaliar a receita do mercado para o mercado global de encapsulamento avançado e tradicional. Diferentes plataformas de encapsulamento avançadas são consideradas no relatório, incluindo flip-chip, fan-in, die embebido, empilhamento 3D e encapsulamento fan-out, que são usados em múltiplas aplicações de usuário final como eletrônicos de consumo, dispositivos médicos, comunicação e telecom, e automotivo. O cenário competitivo foi tomado para calcular penetração de encapsulamento e como jogadores se envolvem em estratégias de crescimento orgânicas e inorgânicas. Essas empresas estão inovando seus produtos para aumentar sua participação de mercado e rentabilidade. Além disso, o relatório foca em analisar fatores macroeconômicos no mercado.

O mercado de encapsulamento de semicondutores é segmentado por plataforma de encapsulamento (encapsulamento avançado [flip chip, SIP, 2.5D/3D, die embebido, encapsulamento em nível de wafer fan-in (FI-WLP), e encapsulamento em nível de wafer fan-out (FO-WLP)] e encapsulamento tradicional), indústria de usuário final (eletrônicos de consumo, aeroespacial e defesa, dispositivos médicos, comunicações e telecom, automotivo, e energia e iluminação), e geografia (Estados Unidos, China, Taiwan, Coreia, Japão, e Europa). O relatório oferece tamanhos de mercado e previsões em termos de valor (USD) para todos esses segmentos.

| Encapsulamento Avançado | Flip-Chip |

| Fan-Out WLP | |

| Fan-In WLP | |

| 2.5D / 3D IC | |

| Die Embebido | |

| SiP / PoP | |

| Encapsulamento em Nível de Painel | |

| Encapsulamento Tradicional | Wire-Bond |

| Leadframe | |

| QFN / QFP / SOP |

| Substratos Orgânicos |

| Leadframes |

| Fios de Ligação |

| Resinas de Encapsulamento |

| Pacotes Cerâmicos |

| Esferas e Bumps de Solda |

| Die-Attach e TIMs |

| ≤ 200 mm |

| 300 mm |

| ≥ 450 mm / Painel |

| OSAT |

| Back-End de Foundry |

| IDM Interno |

| Eletrônicos de Consumo | Smartphones e Wearables | |

| Computação / Data-Center | ||

| Automotivo e Mobilidade | ADAS / Energia EV | |

| Comunicações e Telecom | Infraestrutura 5G | |

| Aeroespacial e Defesa | ||

| Dispositivos Médicos e de Saúde | ||

| Industrial e Energia (LED / Energia) | ||

| América do Norte | Estados Unidos |

| Canadá | |

| México | |

| América do Sul | Brasil |

| Resto da América do Sul | |

| Europa | Alemanha |

| França | |

| Reino Unido | |

| Itália | |

| Países Baixos | |

| Nórdicos | |

| Resto da Europa | |

| Oriente Médio e África | Israel |

| Turquia | |

| CCG | |

| África do Sul | |

| Resto do Oriente Médio e África | |

| APAC | China |

| Taiwan | |

| Coreia do Sul | |

| Japão | |

| Índia | |

| Singapura | |

| Austrália | |

| Nova Zelândia | |

| Resto da APAC |

| Por Plataforma de Encapsulamento | Encapsulamento Avançado | Flip-Chip | |

| Fan-Out WLP | |||

| Fan-In WLP | |||

| 2.5D / 3D IC | |||

| Die Embebido | |||

| SiP / PoP | |||

| Encapsulamento em Nível de Painel | |||

| Encapsulamento Tradicional | Wire-Bond | ||

| Leadframe | |||

| QFN / QFP / SOP | |||

| Por Material de Encapsulamento | Substratos Orgânicos | ||

| Leadframes | |||

| Fios de Ligação | |||

| Resinas de Encapsulamento | |||

| Pacotes Cerâmicos | |||

| Esferas e Bumps de Solda | |||

| Die-Attach e TIMs | |||

| Por Tamanho de Wafer | ≤ 200 mm | ||

| 300 mm | |||

| ≥ 450 mm / Painel | |||

| Por Modelo de Negócio | OSAT | ||

| Back-End de Foundry | |||

| IDM Interno | |||

| Por Indústria de Usuário Final | Eletrônicos de Consumo | Smartphones e Wearables | |

| Computação / Data-Center | |||

| Automotivo e Mobilidade | ADAS / Energia EV | ||

| Comunicações e Telecom | Infraestrutura 5G | ||

| Aeroespacial e Defesa | |||

| Dispositivos Médicos e de Saúde | |||

| Industrial e Energia (LED / Energia) | |||

| Por Geografia | América do Norte | Estados Unidos | |

| Canadá | |||

| México | |||

| América do Sul | Brasil | ||

| Resto da América do Sul | |||

| Europa | Alemanha | ||

| França | |||

| Reino Unido | |||

| Itália | |||

| Países Baixos | |||

| Nórdicos | |||

| Resto da Europa | |||

| Oriente Médio e África | Israel | ||

| Turquia | |||

| CCG | |||

| África do Sul | |||

| Resto do Oriente Médio e África | |||

| APAC | China | ||

| Taiwan | |||

| Coreia do Sul | |||

| Japão | |||

| Índia | |||

| Singapura | |||

| Austrália | |||

| Nova Zelândia | |||

| Resto da APAC | |||

Principais Perguntas Respondidas no Relatório

Qual é o valor atual do mercado de encapsulamento de semicondutores?

O mercado de encapsulamento de semicondutores está avaliado em USD 49,88 bilhões em 2025 e está projetado para atingir USD 81,22 bilhões até 2030.

Qual tecnologia de encapsulamento está crescendo mais rapidamente?

O encapsulamento fan-out em nível de wafer é a plataforma de crescimento mais rápido, avançando a uma TCAC de 12,3% até 2030.

Por que os substratos ABF são um gargalo?

Os substratos ABF são produzidos principalmente em Taiwan e Japão, e a escassez de fornecimento tem levado a aumentos de preços de 20%, limitando a expansão da capacidade flip-chip.

Como o CHIPS Act afeta o encapsulamento?

O CHIPS Act aloca USD 300 milhões para P&D de encapsulamento avançado doméstico, fomentando novas fábricas no Arizona, Califórnia e Novo México e elevando a TCAC da América do Norte para 11,1%.

Qual setor de uso final verá o maior crescimento?

As aplicações automotivas registrarão o maior crescimento a uma TCAC de 10,3%, impulsionadas pela eletrônica de energia de veículos elétricos e demanda ADAS.

Como as arquiteturas chiplet estão influenciando o design de encapsulamento?

Padrões abertos como UCIe 2.0 permitem chiplets heterogêneos, empurrando o encapsulamento em direção a interposers de alta densidade e hybrid bonding para maior largura de banda e menor latência.

Página atualizada pela última vez em: