3D IC Packaging Market Size and Share

3D IC Packaging Market Analysis by Mordor Intelligence

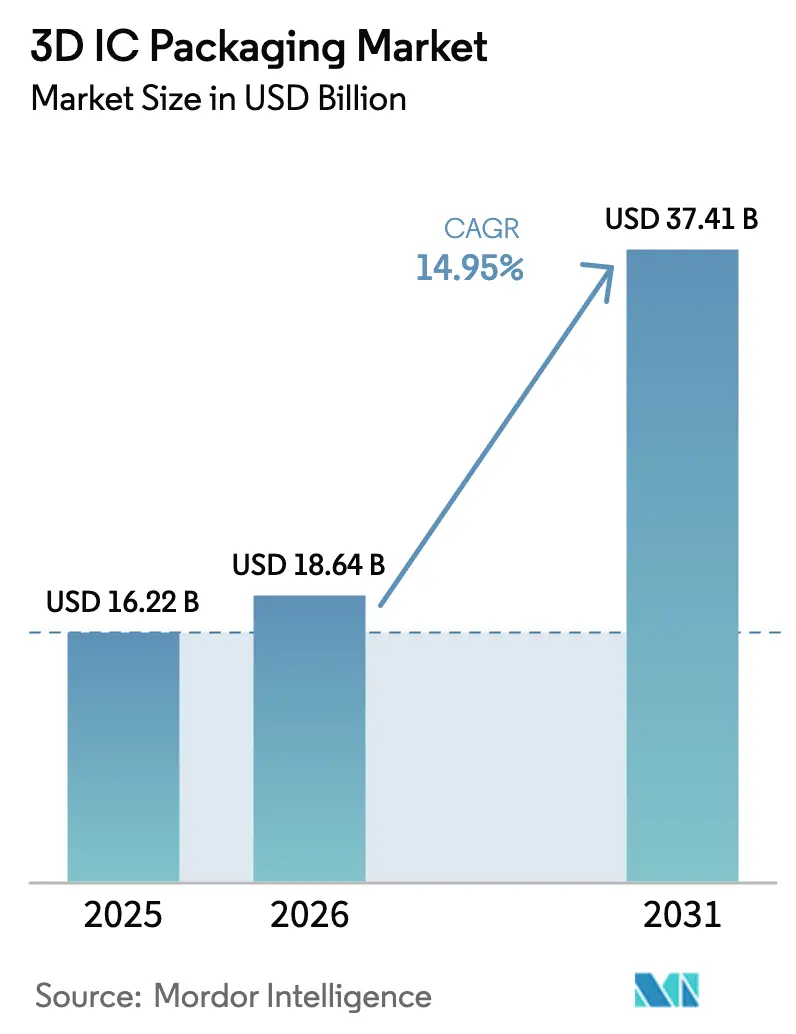

3D IC packaging market size in 2026 is estimated at USD 18.64 billion, growing from 2025 value of USD 16.22 billion with 2031 projections showing USD 37.41 billion, growing at 14.95% CAGR over 2026-2031. This surge is propelled by soaring artificial-intelligence and high-performance-computing workloads that outstrip the bandwidth, latency and power limits of conventional 2D layouts, forcing semiconductor vendors to adopt vertically stacked architectures. Advanced memory such as HBM4+ and logic-to-memory co-design inside the 3D IC packaging market are resetting cost hierarchies, while supply–demand imbalances in through-silicon-via (TSV) tooling and CoWoS substrates temper near-term output expansion. Asia-Pacific maintains a formidable lead thanks to Taiwan and South Korea’s tightly integrated foundry clusters, but North American reshoring under the CHIPS Act and Gulf-region green-field programs are altering long-term capacity maps. Intensifying export-control regimes, coupled with defense-grade security mandates, compel foundries to re-engineer equipment procurement and partner networks without compromising time-to-yield.[1]Cheng Ting-Fang, “TSMC moves closer to next-gen packaging for Nvidia, Google AI chips,” Nikkei Asia, asia.nikkei.com

Key Report Takeaways

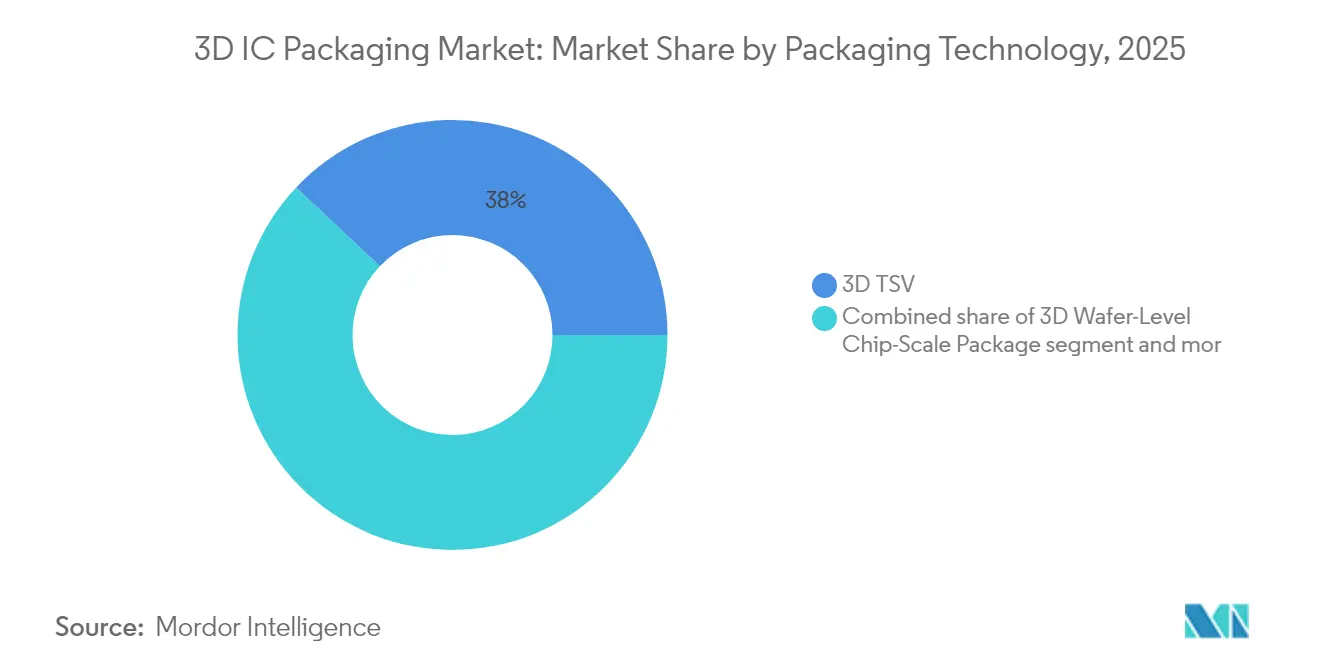

- By packaging technology, 3D TSV retained 37.96% of the 3D IC packaging market share in 2025, while hybrid-bond stacking is projected to compound at 21.15% CAGR through 2031.

- By integration approach, 2.5D interposers held 57.38% share of the 3D IC packaging market in 2025; true 3D stacking shows the steepest growth at 21.28% CAGR to 2031.

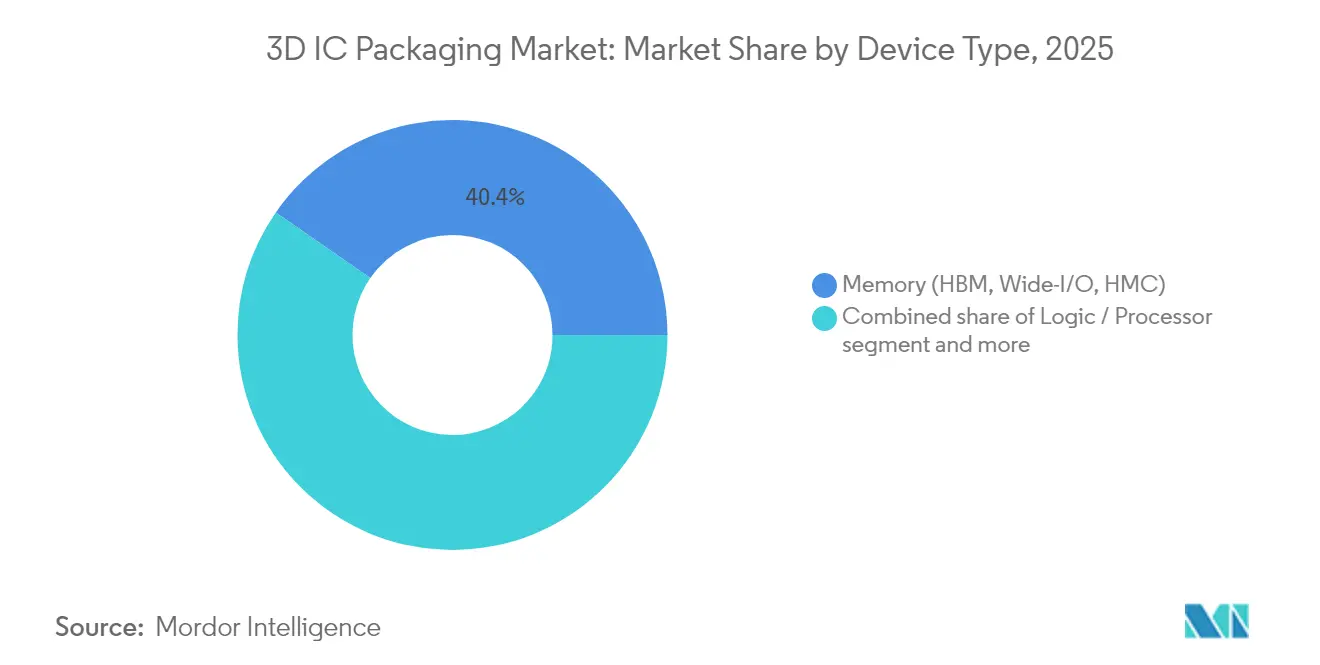

- By device type, memory—dominated by HBM stacks—accounted for 40.35% of the 3D IC packaging market size in 2025; HBM4+ volumes are poised for a 23.86% CAGR through 2031.

- By end-user application, HPC and AI captured 37.45% revenue share of the 3D IC packaging market in 2025 and is on track for a 19.05% CAGR to 2031.

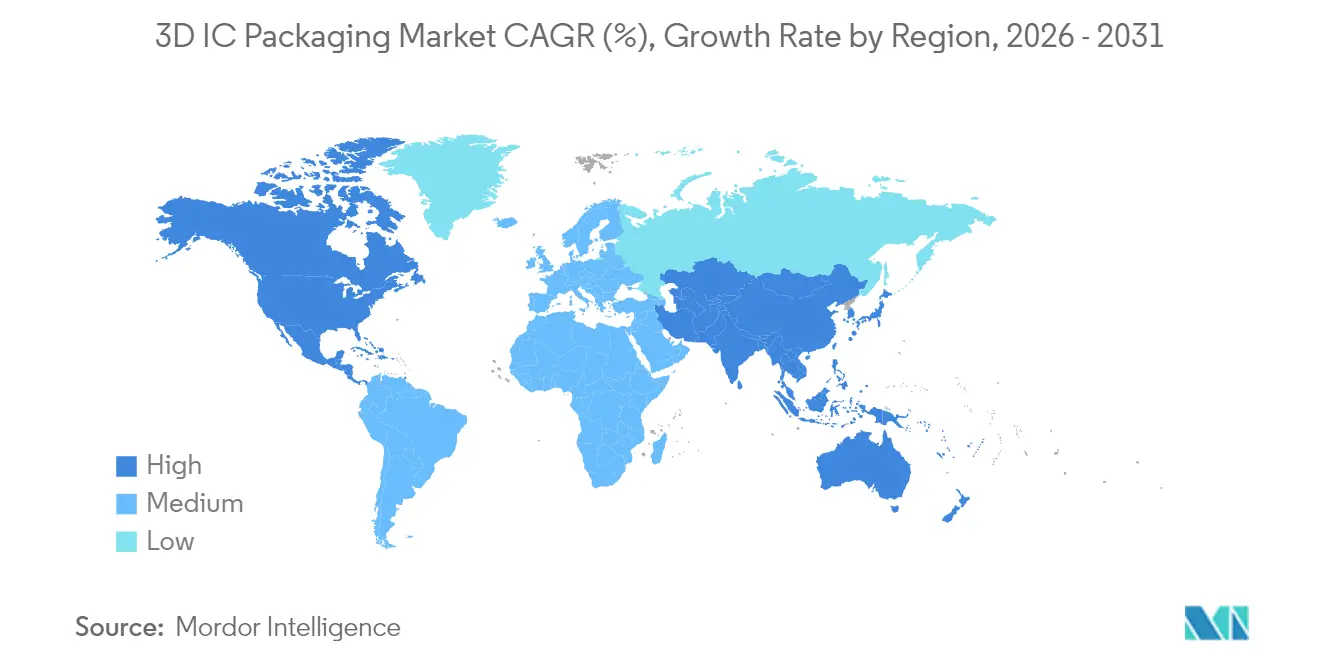

- By geography, Asia-Pacific led with 62.41% share in 2025, whereas the Middle East and Africa region is forecast to register a 19.06% CAGR between 2026 and 2031.

Note: Market size and forecast figures in this report are generated using Mordor Intelligence’s proprietary estimation framework, updated with the latest available data and insights as of January 2026.

Global 3D IC Packaging Market Trends and Insights

Drivers Impact Analysis

| Driver | (~) % Impact on CAGR Forecast | Geographic Relevance | Impact Timeline |

|---|---|---|---|

| Explosive AI / HPC demand for HBM-stacked packages | 4.20% | Global, concentrated in North America & APAC | Short term (≤ 2 years) |

| Mobile & wearables shift to Wafer-Level Chip-Scale Packages (WLCSP) | 2.80% | APAC core, spill-over to North America | Medium term (2-4 years) |

| Foundry "Foundry 2.0" strategy integrating packaging | 2.10% | Global, led by Taiwan & South Korea | Medium term (2-4 years) |

| Glass-core & panel-level substrates lowering cost at scale | 1.90% | APAC manufacturing, global deployment | Long term (≥ 4 years) |

| Defense-grade chiplets mandate secure heterogeneous integration | 1.40% | North America & EU, selective APAC | Long term (≥ 4 years) |

| Carbon-neutral fabs prioritising low-temperature hybrid bonding | 0.80% | EU & North America, expanding to APAC | Long term (≥ 4 years) |

| Source: Mordor Intelligence | |||

Explosive AI / HPC Demand for HBM-Stacked Packages

A wave of data-center accelerators is reshaping bill-of-materials priorities, pushing HBM stacks inside the 3D IC packaging market to the top of every advanced-node roadmap. TSMC is scaling CoWoS output to 88,000 wafers per month by 2026 to keep pace with Nvidia’s next-generation GPUs. The shift from HBM3E to HBM4+ triples effective bandwidth density while holding thermal design limits steady, forcing substrate makers to qualify thicker core materials and finer copper redistribution layers. Samsung’s H-Cube platform couples’ logic and memory on-package, illustrating how memory-centric topologies are cascading down to board-level architecture. The net effect is a higher stacked-die ratio per device, a richer TSV mix and, ultimately, an elevated ASP across the 3D IC packaging market.

Mobile and Wearables Shift to Wafer-Level Chip-Scale Packages (WLCSP)

Wearable and premium-smartphone OEMs now view wafer-level system-in-package footprints as the default path to squeezing radios, PMICs and MEMS into sub-7 mm platforms. Apple’s 2026 flagship is widely expected to showcase advanced WLCSP for its A-series SoC, a signal that form-factor is trumping traditional cost-per-pin trade-offs. Taiwanese OSATs have responded by doubling lithography lines dedicated to redistributed-layer-count (RDL)-first flows, while South Korean rivals pivot toward resin-coated copper foils to mitigate warpage. These moves expand the 3D IC packaging market beyond data-center silicon and into everyday consumer devices, diversifying revenue streams and improving fab loading factors.

Foundry “Foundry 2.0” Strategy Integrating Packaging

The boundary between wafer fabrication and advanced packaging vanished once node-to-node transistor gains slipped below historical norms. TSMC’s USD 65 billion Arizona campus now dedicates two buildings exclusively to CoWoS and SoIC services. Samsung’s roadmap marries 2 nm FEOL with 2.5D H-CUBE back-end in the same cleanroom complex, lowering inter-factory cycle time by 30%. Intel Foundry Services, meanwhile, bundles Foveros Direct and EMIB with reticle-stitching options, allowing customers to marry leading-edge compute tiles with mature I/O dice. Vertical integration lifts margin accelerates yield learning and positions foundries as one-stop shops for the full 3D IC packaging market lifecycle.[2]Flora Wang and Jingyue Hsiao, “C Sun poised to join US semiconductor expansion wave,” DIGITIMES, digitimes.com

Glass-Core and Panel-Level Substrates Lowering Cost at Scale

Organic substrates cannot meet the co-planarity and CTE requirements of ≥50 Gbps die-to-die links, prompting early adoption of glass-core laminates that support through-glass vias (TGVs). Intel’s 2025 pilot showed a 40% reduction in skew variance across 300 mm glass cores, paving the way for panel-level stitching onto 510 mm × 515 mm substrates. TSMC’s panel-level packaging program targets a 20–30% unit-cost drop for AI accelerators by 2027, while C Sun and Mycronic ship over-size lithography gear to Taiwan OSATs. As economies of scale kick in, glass-based carriers will widen the addressable tier-2 customer base of the 3D IC packaging market.

Defense-Grade Chiplets Mandate Secure Heterogeneous Integration

U.S. and European defense agencies now specify tamper-resistant, multi-vendor chiplet stacks that can be audited down to individual bump geometry. Programs such as the U.S. SHIP initiative fund prototype runs where logic processed at a trusted North American fab is hybrid-bonded to Asia-Pacific-sourced RF dice within secure facilities. The requirement for onshore trusted flows, secure firmware provisioning and lifetime traceability raises the engineering content per unit and injects premium pricing into specialized corridors of the 3D IC packaging market. Supply-chain transparency tools and cryptographic die-to-die links are becoming as critical as mechanical alignment accuracy.

Restraints Impact Analysis

| Restraint | (~) % Impact on CAGR Forecast | Geographic Relevance | Impact Timeline |

|---|---|---|---|

| Scarcity of production TSV tools and CoWoS capacity | -3.10% | Global, most severe in APAC | Short term (≤ 2 years) |

| Thermal-design-limit (TDL) challenges beyond 1 W/mm² | -2.40% | Global, critical for HPC applications | Medium term (2-4 years) |

| High IP / EDA cost for 3D floor-planning | -1.80% | Global, concentrated in design centers | Medium term (2-4 years) |

| Panel warp and yield loss >3% in early PLP lines | -1.20% | APAC manufacturing hubs | Short term (≤ 2 years) |

| Source: Mordor Intelligence | |||

Scarcity of Production TSV Tools and CoWoS Capacity

TSV etchers, bonding aligners and CoWoS-grade substrate laminators remain booked 12–18 months out, constraining upside for OSATs scrambling to meet AI accelerator schedules. Applied Materials and Tokyo Electron both forecast double-digit equipment backlog into mid-2026, yet component shortages and install-crew bottlenecks slow actual ramp-ups. With TSMC commanding the lion’s share of CoWoS substrates, buyers compete for wafer-start allocations, sometimes pre-paying quarters in advance. The scarcity curtails immediate revenue realization across the 3D IC packaging market even when demand signals are unmistakably strong.[3]“ASM International Delivers Record 53.4% Margins as AI Chip Orders Soar 14% in Q1 2025,” StockTitan, stocktitan.net

Thermal-Design-Limit (TDL) Challenges Beyond 1 W/mm²

As stacked dies exceed 1 W/mm², conventional heat-spreaders fail to evacuate junction heat in the middle tiers. TSMC is piloting microfluidic cooling channels etched directly into silicon interposers, but early-stage prototypes add manufacturing complexity and uncertain reliability. Device builders must therefore throttle clocks or adopt spread-out chiplet layouts, diluting some performance gains and nudging power budgets upward. The gap between cooling innovation and power-density escalation will persist throughout the decade, shaving points off the compound trajectory of the 3D IC packaging market.

Segment Analysis

By Packaging Technology: TSV Leadership Faces Hybrid Bonding Disruption

3D TSV nodes retained 37.96% of the 3D IC packaging market share in 2025 because mature lithographic rules, bulk production tooling and field reliability data aligned with memory vendors’ cost-per-GB targets. Multiple HBM3E lines already amortized their TSV drill and fill equipment, stabilizing gross margins even as die counts increased. Yet the hybrid-bond segment is expanding at a 21.15% CAGR, levering copper-to-copper direct contact to cut z-height by 40% and interconnect resistance by 15%. These electrical gains are pivotal in compute-dense AI accelerators that push beyond traditional package-substrate escape routing limits.

The pivot does not render TSV obsolete. Instead, dual-path roadmaps emerge: TSV remains the default for high-volume memory and sensor stacks, while hybrid bonding occupies compute-centric, low-latency corners of the 3D IC packaging market. OSATs able to host both flows on adjacent lines secure risk-diversified bookings. As substrate makers scale glass cores, hybrid bonding alignment accuracy improves further, hinting at future cross-over where cost curves intersect and hybrid bonding usurps TSV in certain volume SKUs.

Note: Segment shares of all individual segments available upon report purchase

By Integration Approach: Interposer Dominance Challenged by True 3D Evolution

2.5D interposers booked 57.38% revenue in 2025, capitalizing on a decade of yield learning that brought silicon-interposer defectivity to <0.1 dpm. Because interposers decouple front-end node choice from back-end assembly, GPU vendors ship reticle-sized compute tiles beside older-node I/O dies without redesigning the full stack. However, true 3D stacking logs a 21.28% CAGR, fuelled by die-to-die latency gains that can cut model-training time by double-digit percentages. Flagship use cases include vertical NAND, near-memory compute lenses and in-package high-Q RF filters—all scenarios where z-axis proximity beats planar reticulation.

Early reliability fears—electro-migration in buried micro-bumps and thermo-mechanical shear at die corners—are being mitigated by low-modulus under-fills and hybrid-bond copper diffusion barriers. As micro-fluidic cooling and graphene heat-spreaders mature, true 3D adoption accelerates. The 3D IC packaging market therefore bifurcates into an interposer mainstream and a true-stacked performance edge, each advancing on differentiated KPI roadmaps rather than price alone.

By Device Type: Memory Applications Drive HBM4+ Innovation

Memory held 40.35% of 2025 revenue, the single largest usage slice inside the 3D IC packaging market. The impending jump to HBM4+—slated for high-volume ramp in 2027—injects a forecast 23.86% CAGR for memory-centric packages through 2031. Stacked-memory vendors co-design channel architecture and micro-bump pitch with foundry partners to preserve signal integrity at >1 Tbps aggregate bandwidth. Logic-plus-memory cobonds yield SKU-specific trade-offs: more layers raise cache residency but translate into tougher thermal budgets.

Outside memory, logic processors gain share through chiplet partitioning that mixes EUV-patterned compute tiles with mature-node PHY dice. Sensor and MEMS modules adopt 3D WLCSP to marry optical, inertial and environmental sensing within dental-paste-sized packages for wearables and automotive cabins. RF and analog players harness vertical isolation inside glass cores to shield noise-sensitive blocks even as 5G FR2 frequencies cross 52 GHz. Each device sub-niche shapes its own cost-performance envelope within the 3D IC packaging market, driving demand diversity and smoothing capacity utilization.

Note: Segment shares of all individual segments available upon report purchase

By End-User Application: HPC and AI Dominance Reshapes Industry Priorities

HPC and AI workloads seized 37.45% of 2025 sales and are projected to rise at a 19.05% CAGR through 2031, catapulting accelerator vendors to the top tier of package-substrate allocation. Cloud hyperscalers increasingly sidestep merchant silicon and fund custom ASICs stitched inside CoWoS or panel-level carriers, ensuring guaranteed slotting in the 3D IC packaging market. With model-parameter counts doubling every nine months, bandwidth per millimetre of substrate outpaces Moore-era transistor density as the key metric.

Consumer electronics retains scale momentum—especially as OEMs add mixed-reality compute to smartphones—but its pricing power pales next to data-center ASPs. Automotive and ADAS designs, governed by AEC-Q100 and ISO 26262, seek extended runtimes over a −40 °C-to-150 °C envelope, nudging suppliers to adopt under-fill chemistries resistant to temperature cycling. Aerospace and defence embrace secure chiplets and radiation-hard dielectrics, paying 3–5 × consumer ASP per square millimetre. Medical and Industrial IoT packages prioritise photonic sensors and extreme-low-leakage logic, broadening the footprint of the 3D IC packaging market without diluting its technology edge.

Geography Analysis

Asia-Pacific commanded 62.41% of the 3D IC packaging market in 2025, a consequence of Taiwan’s advanced-node hegemony, South Korea’s memory-centric back-end clusters and mainland China’s sprint toward domestic capacity. TSMC’s CoWoS, Samsung’s H-Cube and ASE’s FOCoS platforms anchor dense supplier habitats, driving low logistics latency and fast process transfer loops. Even so, relocation risk under geopolitical crosscurrents pushes some customers to dual source into Malaysia, Singapore and Vietnam, lengthening the region’s technology reach while marginally raising cost baselines.

North America benefits from USD-denominated CHIPS Act incentives that subsidize capex for both leading-edge wafers and advanced packaging lines. TSMC Arizona and Intel Ohio collectively exceed a projected 100,000 wafers per month of back-end capacity by 2028, a cushion against Asia-bound supply disruption. Proximity to Nvidia, AMD and a host of machine-learning start-ups tightens design-manufacturing feedback loops, granting North America disproportionate influence over the direction of the 3D IC packaging market even if absolute volume lags Asia.

The Middle East and Africa region posts the highest forecast CAGR at 19.06%, albeit from a small base. Sovereign-wealth-fund-backed fabs in the UAE and Saudi Arabia’s Vision 2030 industrial zones earmark billions for glass-core substrate lines and OSAT pilot plants. Europe focuses on automotive reliability and green-manufacturing leadership, leveraging German power-electronic expertise and French photonics clusters. Latin America remains a niche assembly point for consumer devices, while Eastern Europe eyes defense-oriented secure-package initiatives. Together, these moves fragment capacity geographically, opening localized demand pockets inside the broader 3D IC packaging market.

Competitive Landscape

Technological differentiation rather than labour cost now dictates competitive rank. TSMC and Samsung together hold the premium slice of the 3D IC packaging market with CoWoS, SoIC and H-Cube portfolios addressing compute and memory concurrently. ASE Group retains volume leadership in versatile FOCoS flows, while Amkor champions turnkey service for consumer SOCs. Intel Foundry Services bridges FEOL and BEOL with Foveros Direct plus EMIB, luring fabless clients seeking node-agnostic chiplet aggregation.

Chinese contenders—JCET, Huahong and SMIC’s packaging arms—narrow process gaps by licensing hybrid-bond aligners and TSV etchers, accelerating domestic uptake under the national “advanced packaging first” policy. Equipment access constraints and export-licence uncertainty, however, complicate scale-up pace. Japanese specialists such as Ibiden and Shinko Electric secure high-TG BT substrates and next-gen Ajinomoto-build-up films, undergirding the material backbone of the 3D IC packaging market. Patent thickets in copper direct bonding and elastomer-embedded micro-fluidics grant early entrants’ defensible moats, but standards bodies—chiefly the UCIe Consortium—chip away at proprietary interposer and chiplet link protocols, gradually commoditizing baseline connectivity.

Strategic moves over the past 18 months underline a pivot toward end-to-end verticals. TSMC’s USD 35 billion multiyear capex uplift channels one-third of spend into BEOL packaging, while Samsung corrals logic, DRAM and packaging into a single business unit. ASE’s Penang mega-campus triples cleanroom footage, signalling OSAT commitment to HPC packages. In response, equipment vendors consolidate through M and A—e.g., Lam Research’s acquisition of a specialist panel-warpage metrology start-up—to anchor share in a swelling capex cycle. Competition is therefore dynamic but not yet fragmented, keeping the 3D IC packaging market moderately concentrated.[4]UCIe Consortium, “Specifications,” uciexpress.org

3D IC Packaging Industry Leaders

-

Taiwan Semiconductor Manufacturing Company Limited

-

Advanced Semiconductor Engineering Inc.

-

Amkor Technology Inc.

-

Samsung Electronics Co., Ltd.

-

Siliconware Precision Industries Co. Ltd.

- *Disclaimer: Major Players sorted in no particular order

Recent Industry Developments

- July 2025: TSMC accelerated panel-level packaging, targeting 2027 readiness and 20–30% cost reductions for AI chips.

- June 2025: ASE Technology debuted FOCoS-Bridge, integrating TSVs to meet soaring AI bandwidth needs.

- June 2025: Broadcom revealed 3.5D eXtreme Dimension System in Package, integrating 6,000 mm² of silicon and 12 HBM stacks.

- June 2025: TSMC broke ground on eight fabs and an advanced-packaging plant, expanding global capacity.

Global 3D IC Packaging Market Report Scope

3D IC packaging is a packing methodology for including numerous IC inside the same package. In a 3D structure, active chips are integrated by die stacking for the shortest interconnect and smallest package footprint.

The 3D IC Packaging Market is segmented by Packaging Technology (3D wafer-level chip-scale packaging (WLCSP), 3D TSV), by End-User (Consumer Electronics, Aerospace, and Defense, Medical Devices, Communications and Telecom, Automotive), and Geography.

| 3D TSV |

| 3D Wafer-Level Chip-Scale Package (WLCSP) |

| Hybrid-Bond Stacking (WoW, CoW, SoIC) |

| Fan-Out 3D & Panel-Level Packaging (PLP) |

| 2.5D Interposer |

| True 3D Stacking |

| System-in-Package / Chiplet-based HI |

| Memory (HBM, Wide-I/O, HMC) |

| Logic / Processor |

| Sensor & MEMS |

| RF & Analog |

| High-Performance Computing & AI |

| Consumer Electronics & Mobile |

| Automotive & ADAS |

| Aerospace & Defence |

| Medical & Industrial IoT |

| North America | United States |

| Canada | |

| Mexico | |

| Europe | United Kingdom |

| Germany | |

| France | |

| Italy | |

| Rest of Europe | |

| Asia-Pacific | China |

| Japan | |

| India | |

| South Korea | |

| Rest of Asia | |

| Middle East | Israel |

| Saudi Arabia | |

| United Arab Emirates | |

| Turkey | |

| Rest of Middle East | |

| Africa | South Africa |

| Egypt | |

| Rest of Africa | |

| South America | Brazil |

| Argentina | |

| Rest of South America |

| By Packaging Technology | 3D TSV | |

| 3D Wafer-Level Chip-Scale Package (WLCSP) | ||

| Hybrid-Bond Stacking (WoW, CoW, SoIC) | ||

| Fan-Out 3D & Panel-Level Packaging (PLP) | ||

| By Integration Approach | 2.5D Interposer | |

| True 3D Stacking | ||

| System-in-Package / Chiplet-based HI | ||

| By Device Type | Memory (HBM, Wide-I/O, HMC) | |

| Logic / Processor | ||

| Sensor & MEMS | ||

| RF & Analog | ||

| By End-User Application | High-Performance Computing & AI | |

| Consumer Electronics & Mobile | ||

| Automotive & ADAS | ||

| Aerospace & Defence | ||

| Medical & Industrial IoT | ||

| Geography | North America | United States |

| Canada | ||

| Mexico | ||

| Europe | United Kingdom | |

| Germany | ||

| France | ||

| Italy | ||

| Rest of Europe | ||

| Asia-Pacific | China | |

| Japan | ||

| India | ||

| South Korea | ||

| Rest of Asia | ||

| Middle East | Israel | |

| Saudi Arabia | ||

| United Arab Emirates | ||

| Turkey | ||

| Rest of Middle East | ||

| Africa | South Africa | |

| Egypt | ||

| Rest of Africa | ||

| South America | Brazil | |

| Argentina | ||

| Rest of South America | ||

Key Questions Answered in the Report

What is the current size of the 3D IC packaging market?

The 3D IC packaging market size reached USD 18.64 billion in 2026 and is forecast to hit USD 37.41 billion by 2031.

Which segment leads the 3D IC packaging market?

By technology, 3D TSV maintains leadership with 37.96% share, though hybrid-bonding is the fastest-growing segment.

Why is Asia-Pacific dominant in 3D IC packaging?

Asia-Pacific hosts the densest cluster of foundries and OSATs—chiefly in Taiwan and South Korea—giving it 62.41% market share in 2025.

How fast is the HPC and AI application segment growing?

HPC and AI packages are projected to expand at a 19.05% CAGR, reflecting rising demand for memory-centric accelerator designs.

What are the main restraints on market growth?

Capacity shortages in TSV and CoWoS tooling, thermal-design-limit challenges above 1 W/mm², and high 3D EDA licensing costs collectively dampen near-term expansion.

Which new technologies could lower advanced packaging costs?

Glass-core and panel-level substrates promise 20–30% unit-cost reductions once high-volume lines mature, reshaping future cost curves in the 3D IC packaging market.

Page last updated on: