Taille et part du marché du emballage de semiconducteurs

Analyse du marché du emballage de semiconducteurs par Mordor Intelligence

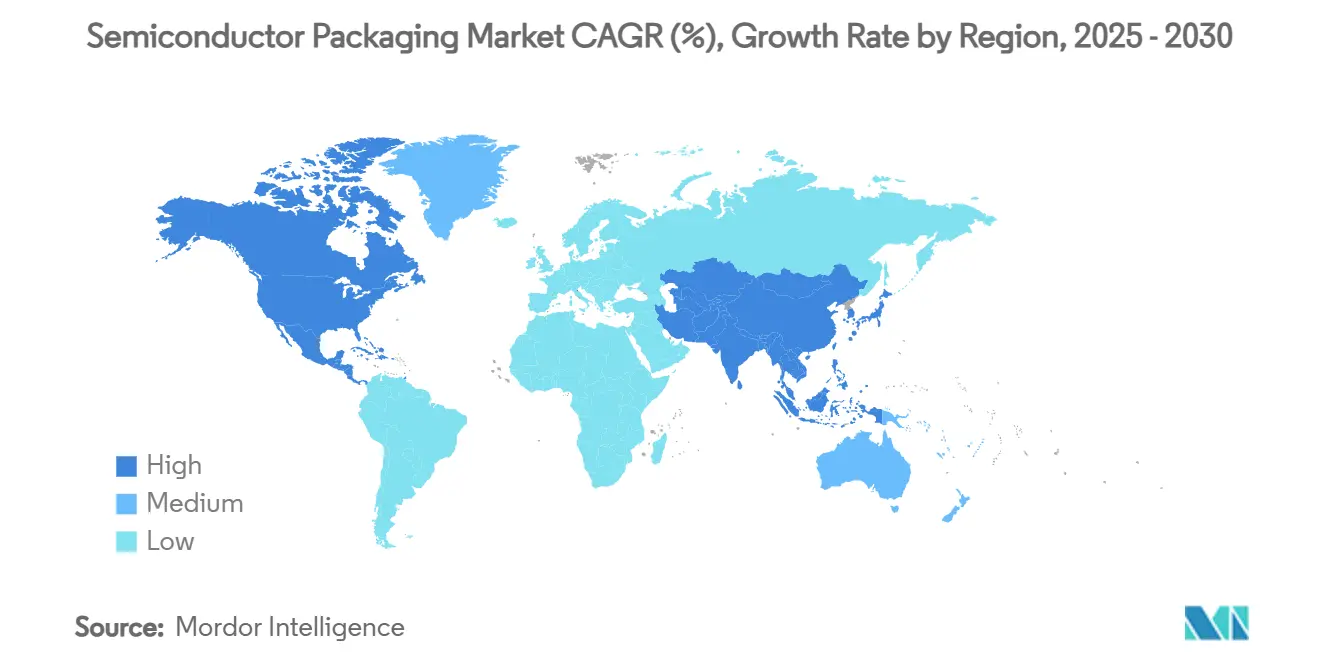

La taille du marché du emballage de semiconducteurs s'élevait à 49,88 milliards USD en 2025 et devrait atteindre 81,22 milliards USD d'ici 2030, progressant à un TCAC de 10,24 % sur la période 2025-2030. [1]Cheng Ting-Fang, "TSMC moves closer to next-gen emballage for Nvidia, Google AI puces," Nikkei Asia, asia.nikkei.comUne transition de l'assemblage axé sur les coûts vers l'intégration critique pour les performances sous-tend cette croissance. La demande pour les architectures 2.5D et 3D un fortement augmenté car les charges de travail d'IA nécessitent une mémoire à large bande passante et des chemins thermiques supérieurs. Le volume reste ancré dans les formats traditionnels de wire-bond et leadframe, mais la création de valeur migre vers le emballage au niveau wafer fan-out (WLP) et les interposeurs compatibles chiplet. L'électrification automobile soutient une expansion à deux chiffres dans les modules à haute densité de puissance, tandis que les cycles de renouvellement des smartphones et PC maintiennent les volumes de base dans le segment grand public. Régionalement, l'Asie commande plus de la moitié de la production mondiale, mais l'Amérique du Nord enregistre le TCAC le plus élevé grâce aux incitations du puces Act qui financent de nouvelles usines back-end.[2]U.S. Department of Commerce, "puces for America Announces up to $300 million in Funding to Boost U.S. Semiconductor emballage," commerce.gov Les goulots d'étranglement d'approvisionnement en substrats ABF et les restrictions d'exportation sur les outils avancés catalysent la diversification géographique et l'innovation des matériaux.

Points clés du rapport

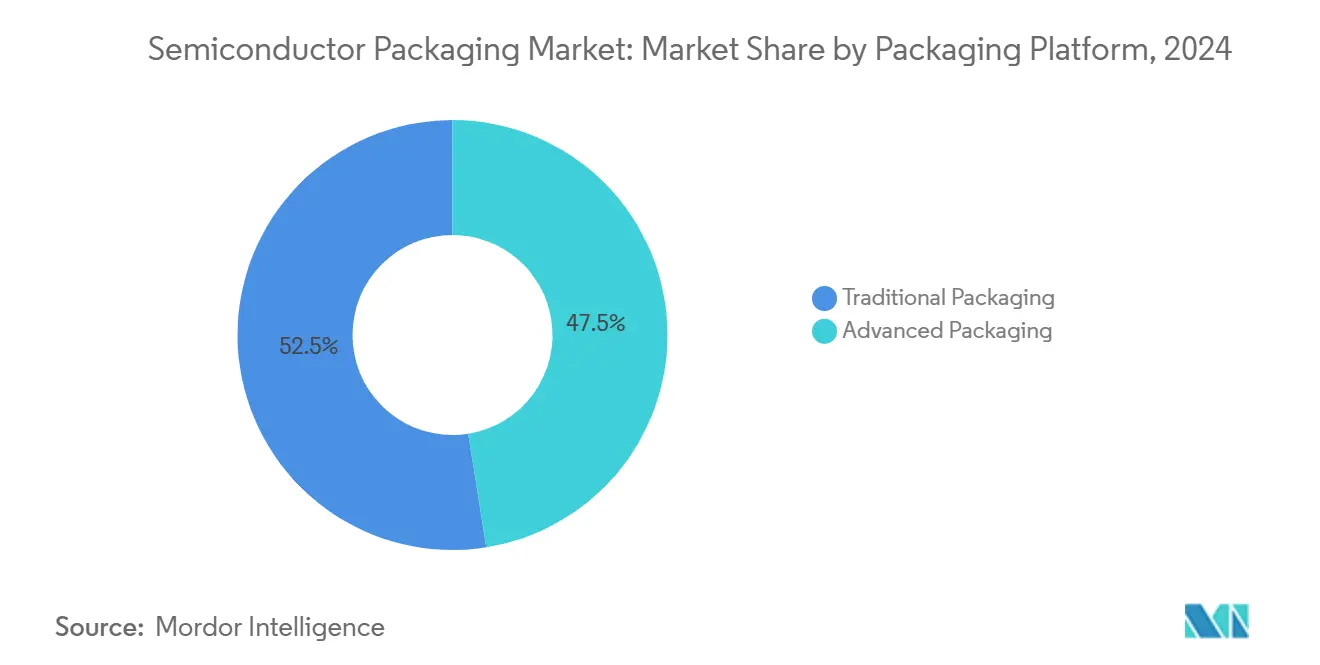

- Par plateforme de emballage, les formats traditionnels détenaient 52,5 % de la part du marché du emballage de semiconducteurs en 2024, tandis que le fan-out WLP devrait croître à un TCAC de 12,3 % jusqu'en 2030.

- Par industrie d'utilisation finale, l'électronique grand public menait avec 43,8 % de part de revenus de la taille du marché du emballage de semiconducteurs en 2024 ; l'automobile affiche la croissance la plus rapide à 10,3 % de TCAC jusqu'en 2030.

- Par taille de wafer : 300 mm stimule l'efficacité, un capturé 74,0 % de la part du marché du emballage de semiconducteurs en 2024, tandis que le format panel émerge et le traitement au niveau panel sur des substrats de 450 mm ou plus représente le segment à croissance la plus rapide avec un TCAC de 12,5 % jusqu'en 2030

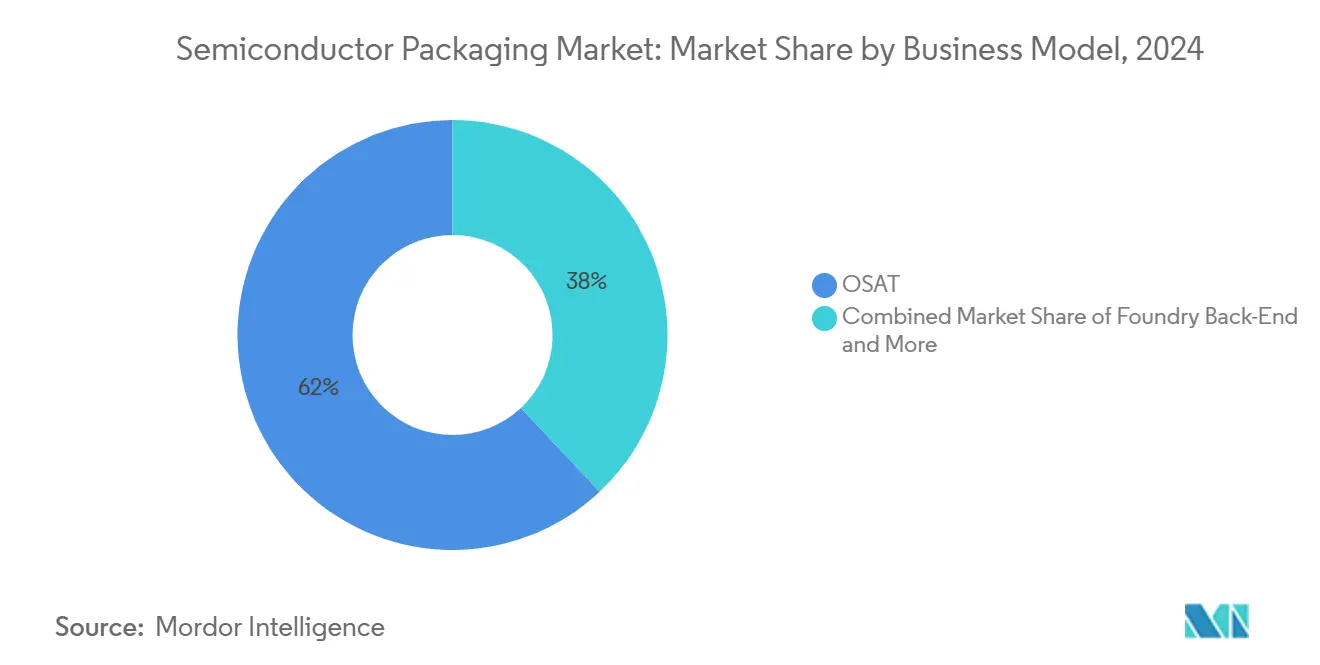

- Par modèle économique, le segment OSAT contrôlait 62,0 % de la part mondiale du marché du emballage de semiconducteurs en 2024 tandis que les services back-end de fonderie augmentent à un TCAC de 10,9 %.

- Par matériau de emballage, les substrats ABF organiques représentaient 41,5 % des revenus en 2024, soutenant l'écosystème basculer-chip grand public

- Par géographie, l'Asie détenait 53,0 % du marché du emballage de semiconducteurs en 2024 ; l'Amérique du Nord est positionnée pour un TCAC de 11,1 % jusqu'en 2030.

- ASE, Amkor et JCET représentaient conjointement plus de 30 % de part des revenus de technologie avancée en 2024, reflétant les avantages d'échelle dans la production de bonding hybride et SiP

Tendances et insights du marché mondial du emballage de semiconducteurs

Analyse d'impact des moteurs

| Moteur | (~) % d'impact sur les prévisions TCAC | Pertinence géographique | Calendrier d'impact |

|---|---|---|---|

| Boom des accélérateurs IA stimulant les interposeurs 2.5D/3D | +2.8% | Mondial (Taïwan, États-Unis, Chine) | Moyen terme (2-4 ans) |

| Packages de puissance de véhicules électrifiés | +1.9% | Amérique du Nord et APAC | Long terme (≥4 ans) |

| Incitations puces États-Unis-UE créant des usines back-end locales | +1.4% | Amérique du Nord et UE | Long terme (≥4 ans) |

| Demande RF-SiP 5G en Chine et Corée | +1.2% | APAC central | Court terme (≤2 ans) |

| emballage au niveau panel pour IoT bas coût | +0.9% | Mondial (hubs APAC) | Moyen terme (2-4 ans) |

| Architectures chiplet alimentant les interposeurs haute densité | +1.6% | Mondial (conception États-Unis, fab. Taïwan) | Moyen terme (2-4 ans) |

| Source: Mordor Intelligence | |||

Boom des accélérateurs IA stimulant les interposeurs 2.5D/3D

La capacité CoWoS de TSMC double de 120 000 à 240 000 unités entre 2023 et 2024, mais ne peut toujours pas répondre entièrement à la demande des hyperscalers. L'écart de capacité stimule les flux alternatifs au niveau panel et les essais d'empilement 3.5D qui agrègent plus de 6 000 mm² de silicium par package. [3]James Morra, "Broadcom Bets on 3.5D emballage Technology to Build Bigger AI puces," Electronic Design, electronicdesign.com Le emballage avancé est donc passé d'un centre de coûts à un levier stratégique pour les performances des systèmes d'IA

Packages de puissance de véhicules électrifiés aux États-Unis et en Asie

La plateforme EliteSiC d'onsemi attribuée par Volkswagen illustre la migration vers des modules de puissance intégrés avec une dissipation thermique supérieure. Les modules SiC moulés 6-en-1 de ROHM offrent triple la densité de puissance des précédents. Ces innovations se concentrent dans les chaînes d'approvisionnement américaines et asiatiques qui peuvent répondre à la qualification automobile rigoureuse.

Incitations CHIPS États-Unis-UE créant des usines back-end locales

Le puces Act alloue 300 millions USD exclusivement à la R&D de emballage avancé, subventionnant les lignes d'essai en Géorgie, Californie et Arizona. Le site Foveros de 3,5 milliards USD d'Intel au Nouveau-Mexique ancre la capacité d'intégration 3D domestique. Des fonds comparables dans l'UE visent à dérisquer l'électronique automobile et de défense des perturbations d'approvisionnement asiatiques.

Demande RF-SiP 5G en Chine et Corée

Le RF-SiP hétérogène de JCET pour amplificateurs de puissance augmente la densité d'intégration de 1,5× par rapport aux nœuds précédents. Bien que les smartphones premium soutiennent l'innovation, la mollesse de la demande Android de masse un tempéré la croissance unitaire, poussant les fournisseurs à optimiser les structures de coûts

Analyse d'impact des contraintes

| Contrainte | (~) % d'impact sur les prévisions TCAC | Pertinence géographique | Calendrier d'impact |

|---|---|---|---|

| Pénurie d'approvisionnement en substrats ABF | -1.8% | Mondial (APAC aigu) | Court terme (≤2 ans) |

| Défis de rendement dans TSV 3D/bonding hybride | -1.3% | Mondial (Taïwan, Corée, États-Unis) | Moyen terme (2-4 ans) |

| Contrôles d'exportation sur outils de emballage avancés vers la Chine | -0.9% | Chine principalement | Long terme (≥4 ans) |

| Limites de dissipation thermique dans fan-out WLP @ <5 nm | -0.7% | Nœuds avancés mondiaux | Moyen terme (2-4 ans) |

| Source: Mordor Intelligence | |||

Pénurie d'approvisionnement en substrats ABF

La hausse de prix de 20 % de Nittobo en août 2025 expose une tension matérielle systémique qui affecte particulièrement les lignes basculer-chip BGA. La capacité qualifiée limitée à Taïwan et au Japon prolonge les délais et pousse les OEM à explorer les alternatives glass-core ou silicon-core.

Défis de rendement dans TSV 3D/bonding hybride

Les tolérances de bonding hybride cuivre-à-cuivre sous 0,5 nm et les rapports d'aspect TSV au-delà de 10:1 multiplient les risques de défauts à travers les empilements. Le programme Blackwell de NVIDIA aurait rencontré des échappées de rendement liées au stress thermomécanique CoWoS-L.

Analyse par segment

Par plateforme de packaging : Les technologies avancées stimulent la migration de valeur

Les offres traditionnelles de wire-bond et leadframe dominaient encore les expéditions avec 52,5 % de part du marché du emballage de semiconducteurs en 2024, garantissant que l'électronique grand public et les dispositifs industriels conservent des coûts de nomenclature abordables. Cependant, le Fan-out WLP dépasse tous les autres formats avec un TCAC de 12,3 %, signalant le mouvement du marché du emballage de semiconducteurs vers des couches de redistribution sans substrat qui réduisent la hauteur z et augmentent la densité d'E/S. Le basculer-chip comble l'écart en associant des bumps à pas fin avec un coût modéré, tandis que les architectures SiP et PoP permettent l'empilement vertical pour les smartphones à espace restreint.

Sur le front avancé, les interposeurs 2.5D positionnent la mémoire à large bande passante adjacente à la logique IA, et les empilements 3D débloquent les gains de latence. Les flux embedded-die et au niveau panel attirent de nouveaux entrants focalisés sur les points de prix IoT, démontrant que le marché du emballage de semiconducteurs se divise en nœuds de performance premium et jeux de volume ultra-bas coût. En contraste, les lignes au niveau panel livrent moins de 0,10 USD par broche, un ratio qui souligne les structures de coûts divergentes. En conséquence, les fabricants d'équipements ont segmenté leurs portefeuilles : les clusters de bonder haute précision pour l'alignement 3 µm coexistent avec les lignes MOLD grand panel visant les étiquettes IoT. Une telle bifurcation redéfinit le positionnement des fournisseurs à l'intérieur du marché du emballage de semiconducteurs.

Note: Parts de segment de tous les segments individuels disponibles à l'achat du rapport

Par matériau de packaging : Les substrats organiques dominent sous la pression d'innovation

Les substrats ABF organiques représentaient 41,5 % des revenus en 2024, soutenant l'écosystème basculer-chip grand public. Pourtant la taille du marché du emballage de semiconducteurs pour les fils de bonding devrait croître de 11,4 % annuellement car les secteurs automobile et industriel prolongent la vie des packages de fils d'aluminium et d'or éprouvés. Les leadframes persistent dans les applications de puissance qui valorisent les performances de dissipateur thermique en cuivre. Les résines d'encapsulation ont progressé vers des grades à conductivité thermique élevée, soutenant les modules SiC et GaN de nouvelle génération.

Les substrats en verre pourraient remplacer les constructions organiques après 2027. Les prototypes d'Intel et Samsung montrent une réduction de 40 % du pas de via et un décalage CTE proche de zéro, réduisant le gauchissement dans les empilements 3D. Les matériaux d'interface thermique intègrent maintenant des charges nano-diamant, réduisant la résistance jonction-boîtier de 30 % dans les onduleurs de traction 1 200 V. Les pics de prix de l'or ont compressé les marges pour le emballage des CI pilotes d'affichage en 2025, motivant la migration vers les bumps colonne cuivre

Par taille de wafer : 300 mm stimule l'efficacité tandis que le format panel émerge

Le format wafer 300 mm un capturé 74,0 % de la part du marché du emballage de semiconducteurs en 2024, confirmant son statut de choix préféré pour les flux back-end avancés qui équilibrent efficacité de traitement et compatibilité des outils front-end. Les wafers plus petits de 200 mm ou moins restent viables pour les lignes analogiques héritées, capteurs et puissance où les coûts de conversion dépassent les gains de productivité. Les formats plus grands permettent des économies d'échelle qui sont de plus en plus critiques car les comptes de dispositifs grimpent dans les smartphones, PC et nœuds IoT industriels.

Le traitement au niveau panel sur des substrats de 450 mm ou plus représente le segment à croissance la plus rapide avec un TCAC de 12,5 % jusqu'en 2030 et est positionné pour augmenter la taille du marché du emballage de semiconducteurs en réduisant la consommation de matériaux par unité et les temps de cycle. Le contrôle du gauchissement, la métrologie de rendement en ligne et la standardisation des équipements restent les principaux obstacles, nécessitant des efforts de développement conjoint entre fabricants d'outils et maisons de emballage haut volume.

Par modèle économique : Le leadership OSAT fait face au défi des fonderies

Les OSAT ont conservé 62,0 % de la part du marché du emballage de semiconducteurs en 2024 grâce à de larges listes de clients et empreintes mondiales. Pourtant l'expansion back-end des fonderies à 10,9 % de TCAC signale l'intégration verticale. Le Wafer Manufacturing 2.0 de TSMC fusionne litho, test et CoWoS sous une seule cotation, floutant les frontières OSAT.

En réponse, ASE vise 1,6 milliard USD de revenus de emballage avancé en 2025 via des capex stratégiques et co-conception avec les OEM système reuters.com. Les start-ups telles que Chipletz se concentrent sur les marchés accessibles adressables où la conception d'interposeur sur mesure s'aligne avec les cartes d'inférence IA, illustrant les stratégies de pénétration de niche.

Note: Parts de segment de tous les segments individuels disponibles à l'achat du rapport

Par industrie d'utilisation finale : L'électronique grand public mène tandis que l'automobile accélère

Les smartphones, tablettes et PC ont assuré une part de 43,8 % du marché du emballage de semiconducteurs en 2024 car les OEM ont rafraîchi les facteurs de forme et introduit des capacités d'IA générative sur dispositif. Néanmoins, la verticale automobile affiche le TCAC le plus élevé à 10,3 % sur le dos de la croissance du contenu des onduleurs EV et contrôleurs de domaine ADAS.

Les modules de puissance de grade automobile commandent des ASP cinq fois plus élevés que les SoC mobiles, élargissant la taille du marché du emballage de semiconducteurs de manière disproportionnée par rapport aux volumes unitaires. L'infrastructure de communications contribue à la demande RF-SiP, tandis que le HPC Données-center dirige les architectures les plus avancées, bouclant la boucle entre les feuilles de route d'algorithmes IA et les choix d'intégration physique.

Analyse géographique

L'Asie un capturé 53,0 % du marché du emballage de semiconducteurs en 2024, cimentée par le monopole CoWoS de Taïwan et l'échelle de la Chine dans l'assemblage wire-bond. L'usine automobile de 4,4 milliards RMB de JCET dans le Jiangsu fait progresser la compétence locale dans les packages de puissance SiC. La Corée du Sud bénéficie du SiP centré mémoire, tandis que le Japon contrôle les chimies de substrats essentielles, renforçant un cluster régional étroitement lié.

Le marché du emballage de semiconducteurs d'Amérique du Nord devrait afficher un TCAC de 11,1 % jusqu'en 2030. Les incitations du puces Act amassent 300 millions USD pour les lignes R&D, engendrant des hubs en Arizona, Nouveau-Mexique et Californie. Les partenariats tels que TSMC-Amkor en Arizona construisent des écosystèmes back-end complets proches des fabs wafer de pointe. Le Canada cultive le emballage photonique, et le Mexique offre un test final bas coût pour les ASIC grand public.

L'Europe se positionne autour de la force automobile et industrielle. Les Tier-1 allemands co-développent des modules SiC refroidis double face visant une densité d'onduleur de 9 kW/L, catalysant l'investissement OSAT de niche. Les Pays-Bas poussent le emballage de transcepteur optique haute fréquence qui s'aligne avec l'adoption de laser à émission de surface à cavité verticale (VCSEL). Le Moyen-Orient et l'Afrique restent émergents, externalisant principalement l'assemblage vers les hubs asiatiques mais planifiant des lignes domestiques pour l'IoT sécurisé et l'électronique de défense sous mandats souverains.

Paysage concurrentiel

L'intensité concurrentielle pivote du prix vers la technologie. TSMC tire parti du savoir-faire de fonderie pour dominer les interposeurs 2.5D tandis que Samsung emploie H-cube pour mélanger mémoire et logique pour l'IA mobile. ASE et Amkor répartissent les risques sur 40+ installations, se concentrant sur l'apprentissage de rendement et les services de conception pour la fabricabilité. JCET met à l'échelle les lignes SiP exécutant les flux AEC-Q100 automobile. L'usine Foveros d'Intel incarne un bond stratégique pour regagner le leadership du emballage, offrant un pas die-to-die de 50 µm pour les plateformes client et Données-center.

Les barrières à l'entrée incluent l'intensité capex, la sécurité d'approvisionnement en substrats, et les verrouillages de co-développement client. Par conséquent, la consolidation via M&un-par ex., l'achat d'Xpeedic par Empyrean-reflète une tentative d'agréger EDA et IP emballage sous un même toit

Leaders de l'industrie du emballage de semiconducteurs

-

ASE Technology Holding Co., Ltd.

-

Amkor Technology, Inc.

-

JCET Group Co., Ltd.

-

Siliconware Precision Industries Co., Ltd.

-

Powertech Technology Inc.

- *Avis de non-responsabilité : les principaux acteurs sont triés sans ordre particulier

Développements récents de l'industrie

- Juin 2025 : ASE et AMD s'associent pour augmenter l'efficacité des Données-centers de 50 % tout en réduisant la puissance de 6,5 %, évaluant les GPU Instinct MI300 pour les charges de travail IA

- Juin 2025 : Infineon dévoile des MOSFET super-jonction SiC basés sur tranchée, ciblant les onduleurs de traction avec les premiers dispositifs 1 200 V dans des packages ID-PAK

- Mai 2025 : ROHM lance des modules SiC moulés 4-en-1 et 6-en-1 qui triplent la densité de puissance et réduisent la surface de carte de 52 %

- Avril 2025 : ASE démontre l'optique co-packagée réduisant l'énergie de liaison à <5 pJ/bit au milieu des prévisions TCAC de bande passante Données-center de 24,9 %

Portée du rapport du marché mondial du emballage de semiconducteurs

Le emballage de semiconducteurs se réfère à un boîtier qui contient un ou plusieurs dispositifs semiconducteurs discrets ou circuits intégrés faits de boîtier plastique, céramique, métal, ou verre. Le emballage protège un système électronique de l'émission de bruit radiofréquence, décharge électrostatique, dommage mécanique, et refroidissement. L'essor de l'industrie des semiconducteurs dans le monde est l'un des principaux facteurs stimulant la croissance du marché du emballage de semiconducteurs. Les avancées continues en termes d'intégration, efficacité énergétique, et caractéristiques de produit en raison de la demande croissante à travers diverses verticales d'utilisateurs finaux de l'industrie et l'utilisation du emballage pour améliorer les performances, fiabilité, et rentabilité des systèmes électroniques accélèrent la croissance du marché.

Le rapport suit les ventes de emballage de semiconducteurs mondialement pour évaluer les revenus du marché pour le marché mondial du emballage avancé et traditionnel. Différentes plateformes de emballage avancé sont considérées dans le rapport, incluant basculer-chip, fan-in, embedded die, empilement 3D, et emballage fan-out, qui sont utilisées dans de multiples applications d'utilisateurs finaux comme l'électronique grand public, dispositifs médicaux, communication et télécommunications, et automobile. Le paysage concurrentiel un été pris pour calculer la pénétration du emballage et comment les acteurs s'impliquent dans les stratégies de croissance organiques et inorganiques. Ces entreprises innovent leurs produits pour augmenter leur part de marché et rentabilité. De plus, le rapport se concentre sur l'analyse des facteurs macroéconomiques dans le marché.

Le marché du emballage de semiconducteurs est segmenté par plateforme de emballage (emballage avancé [basculer chip, SIP, 2.5D/3D, embedded die, emballage au niveau wafer fan-in (FI-WLP), et emballage au niveau wafer fan-out (FO-WLP)] et emballage traditionnel), industrie d'utilisateur final (électronique grand public, unérospatiale et défense, dispositifs médicaux, communications et télécommunications, automobile, et énergie et éclairage), et géographie (États-Unis, Chine, Taïwan, Corée, Japon, et Europe). Le rapport offre des tailles de marché et prévisions en termes de valeur (USD) pour tous ces segments.

| Packaging avancé | Flip-Chip |

| Fan-Out WLP | |

| Fan-In WLP | |

| 2.5D / 3D IC | |

| Embedded-Die | |

| SiP / PoP | |

| Packaging au niveau panel | |

| Packaging traditionnel | Wire-Bond |

| Leadframe | |

| QFN / QFP / SOP |

| Substrats organiques |

| Leadframes |

| Fils de bonding |

| Résines d'encapsulation |

| Packages céramiques |

| Billes et bumps de soudure |

| Die-Attach et TIM |

| ≤ 200 mm |

| 300 mm |

| ≥ 450 mm / Panel |

| OSAT |

| Back-End de fonderie |

| IDM interne |

| Électronique grand public | Smartphones et wearables | |

| Computing / Data-Center | ||

| Automobile et mobilité | ADAS / Puissance EV | |

| Communications et télécommunications | Infrastructure 5G | |

| Aérospatiale et défense | ||

| Dispositifs médicaux et de santé | ||

| Industriel et énergie (LED / Puissance) | ||

| Amérique du Nord | États-Unis |

| Canada | |

| Mexique | |

| Amérique du Sud | Brésil |

| Reste de l'Amérique du Sud | |

| Europe | Allemagne |

| France | |

| Royaume-Uni | |

| Italie | |

| Pays-Bas | |

| Nordiques | |

| Reste de l'Europe | |

| Moyen-Orient et Afrique | Israël |

| Turquie | |

| CCG | |

| Afrique du Sud | |

| Reste du Moyen-Orient et Afrique | |

| APAC | Chine |

| Taïwan | |

| Corée du Sud | |

| Japon | |

| Inde | |

| Singapour | |

| Australie | |

| Nouvelle-Zélande | |

| Reste d'APAC |

| Par plateforme de packaging | Packaging avancé | Flip-Chip | |

| Fan-Out WLP | |||

| Fan-In WLP | |||

| 2.5D / 3D IC | |||

| Embedded-Die | |||

| SiP / PoP | |||

| Packaging au niveau panel | |||

| Packaging traditionnel | Wire-Bond | ||

| Leadframe | |||

| QFN / QFP / SOP | |||

| Par matériau de packaging | Substrats organiques | ||

| Leadframes | |||

| Fils de bonding | |||

| Résines d'encapsulation | |||

| Packages céramiques | |||

| Billes et bumps de soudure | |||

| Die-Attach et TIM | |||

| Par taille de wafer | ≤ 200 mm | ||

| 300 mm | |||

| ≥ 450 mm / Panel | |||

| Par modèle économique | OSAT | ||

| Back-End de fonderie | |||

| IDM interne | |||

| Par industrie d'utilisateur final | Électronique grand public | Smartphones et wearables | |

| Computing / Data-Center | |||

| Automobile et mobilité | ADAS / Puissance EV | ||

| Communications et télécommunications | Infrastructure 5G | ||

| Aérospatiale et défense | |||

| Dispositifs médicaux et de santé | |||

| Industriel et énergie (LED / Puissance) | |||

| Par géographie | Amérique du Nord | États-Unis | |

| Canada | |||

| Mexique | |||

| Amérique du Sud | Brésil | ||

| Reste de l'Amérique du Sud | |||

| Europe | Allemagne | ||

| France | |||

| Royaume-Uni | |||

| Italie | |||

| Pays-Bas | |||

| Nordiques | |||

| Reste de l'Europe | |||

| Moyen-Orient et Afrique | Israël | ||

| Turquie | |||

| CCG | |||

| Afrique du Sud | |||

| Reste du Moyen-Orient et Afrique | |||

| APAC | Chine | ||

| Taïwan | |||

| Corée du Sud | |||

| Japon | |||

| Inde | |||

| Singapour | |||

| Australie | |||

| Nouvelle-Zélande | |||

| Reste d'APAC | |||

Questions clés auxquelles répond le rapport

Quelle est la valeur actuelle du marché du emballage de semiconducteurs ?

Le marché du emballage de semiconducteurs est évalué à 49,88 milliards USD en 2025 et devrait atteindre 81,22 milliards USD d'ici 2030.

Quelle technologie de emballage croît le plus rapidement ?

Le emballage au niveau wafer fan-out est la plateforme à croissance la plus rapide, progressant à un TCAC de 12,3 % jusqu'en 2030.

Pourquoi les substrats ABF sont-ils un goulot d'étranglement ?

Les substrats ABF sont produits principalement à Taïwan et au Japon, et les pénuries d'approvisionnement ont entraîné des augmentations de prix de 20 %, limitant l'expansion de capacité basculer-chip.

Comment le puces Act affecte-t-il le emballage ?

Le puces Act alloue 300 millions USD pour la R&D domestique de emballage avancé, favorisant de nouvelles fabs en Arizona, Californie et Nouveau-Mexique et élevant le TCAC de l'Amérique du Nord à 11,1 %.

Quel secteur d'utilisation finale connaîtra la croissance la plus élevée ?

Les applications automobiles afficheront la croissance la plus élevée avec un TCAC de 10,3 %, stimulées par l'électronique de puissance des véhicules électriques et la demande ADAS.

Comment les architectures chiplet influencent-elles la conception du emballage ?

Les standards ouverts comme UCIe 2.0 permettent les chiplets hétérogènes, poussant le emballage vers des interposeurs haute densité et bonding hybride pour une bande passante plus élevée et latence plus faible.

Dernière mise à jour de la page le: