Taille et Part du Marché Domaine Programmable Gate Array (FPGA)

Analyse du Marché Domaine Programmable Gate Array (FPGA) par Mordor Intelligence

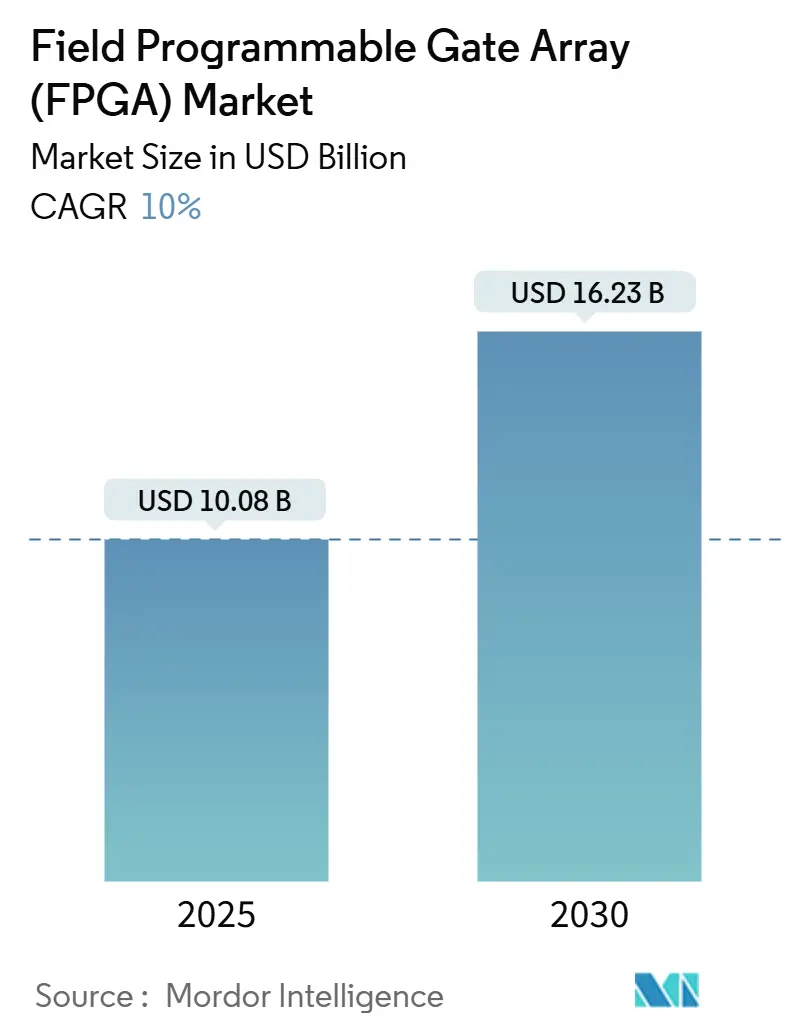

La taille du marché des Domaine programmable gate array un atteint 10,08 milliards USD en 2025 et devrait s'étendre à 16,23 milliards USD d'ici 2030 avec un TCAC de 10,00 %. L'adoption rapide de l'inférence IA edge dans les centres de données hyperscale, la migration vers les architectures radio ouvertes 5G, et le besoin croissant de reconfigurabilité post-déploiement dans l'électronique automobile et unérospatiale ont donné au marché un élan clair.[1]AMD, "From Invention to AI Acceleration," amd.com Les dispositifs haut de gamme ont continué à ancrer les revenus, mais les produits milieu de gamme et bas de gamme ont grimpé rapidement alors que les équipes de conception ont poussé la technologie FPGA dans les systèmes industriels, IoT et grand public sensibles aux coûts. L'Asie-Pacifique un émergé comme la plus grande base de fabrication et le centre de demande à la croissance la plus rapide, bénéficiant des groupes motopropulseurs de véhicules électriques et des constellations du nouveau spatial. L'intensité concurrentielle un augmenté après qu'Intel ait accepté de céder Altera, remodelant la dynamique des fournisseurs tandis que les contrôles à l'exportation ont stimulé le développement domestique parallèle en Chine. La capacité plus serrée des fonderies 300 mm et la transition coûteuse vers les nœuds ≤16 nm ont également forcé les fournisseurs à prioriser les applications à haute marge et les réservations de wafers à long terme avec TSMC et Samsung.

Principaux Points à Retenir du Rapport

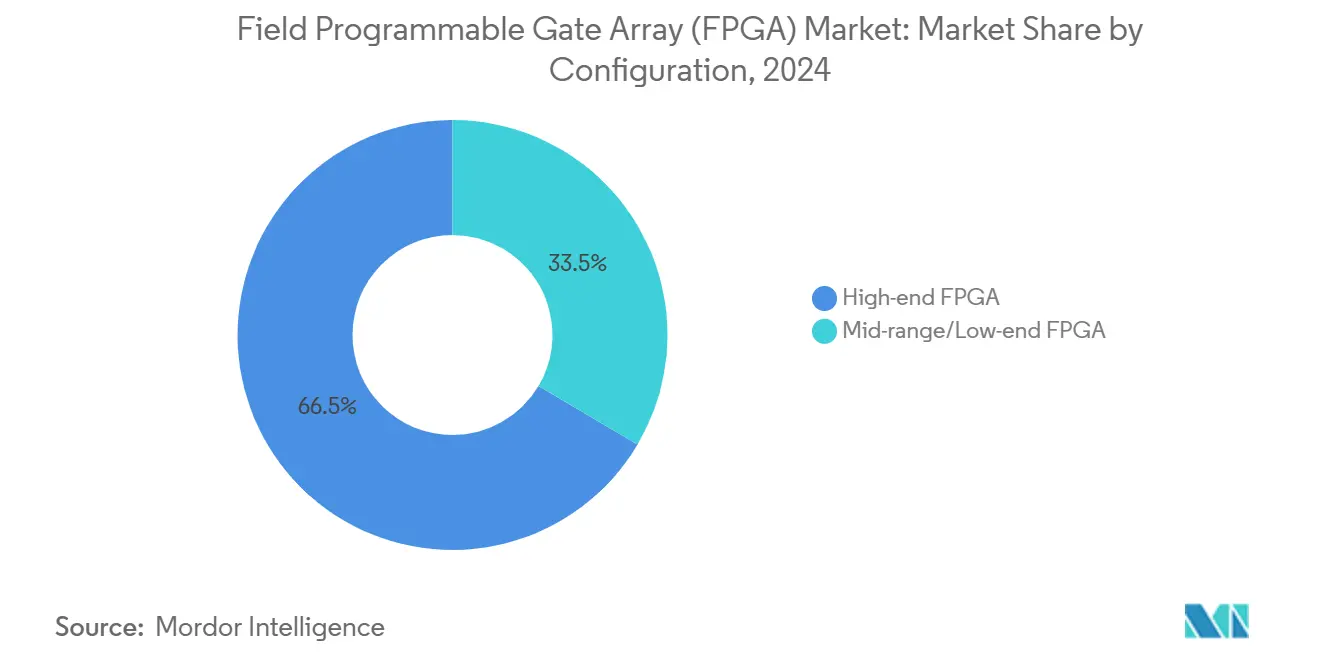

- Par configuration, les dispositifs haut de gamme ont mené avec 66,5 % de la part de marché Domaine programmable gate array en 2024, tandis que les dispositifs milieu et bas de gamme devraient croître à 11,2 % de TCAC jusqu'en 2030.

- Par architecture, les dispositifs basés sur SRAM ont détenu 55,4 % de part de revenus en 2024 ; les offres basées sur flash devraient afficher la croissance la plus rapide compte tenu des budgets de puissance statique plus faibles.

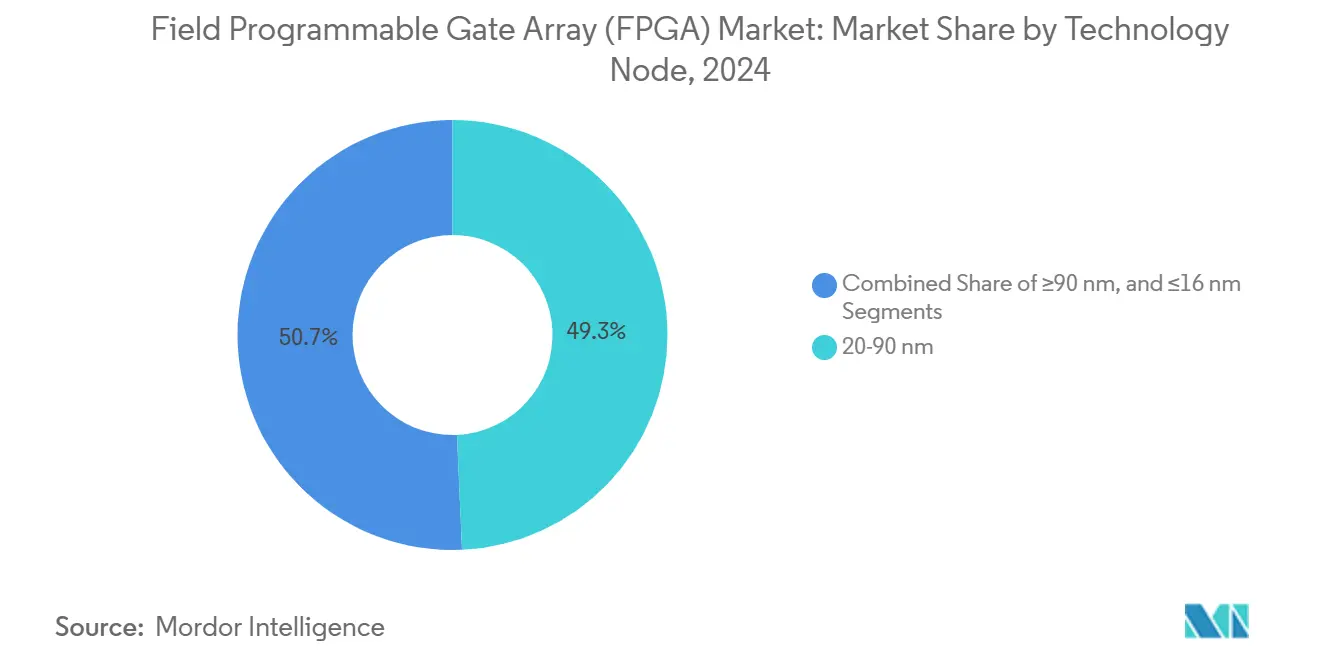

- Par nœud technologique, le segment 20-90 nm un commandé 49,3 % de la taille du marché Domaine programmable gate array en 2024, tandis que le segment ≤16 nm devrait progresser à 15,1 % de TCAC entre 2025-2030.

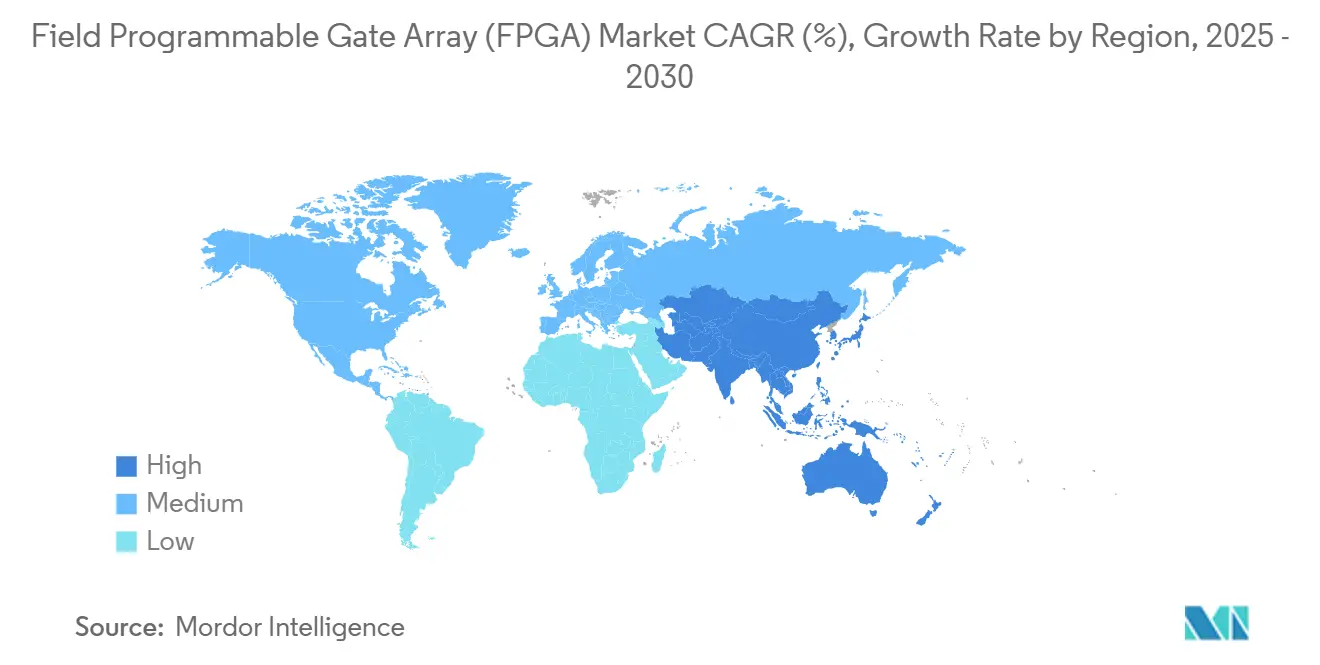

- Par géographie, l'Asie-Pacifique un représenté 39,3 % des revenus en 2024 et devrait s'étendre à 17,1 % de TCAC jusqu'en 2030.

- Par marché final, les applications de centre de données et cloud ont capturé 29,2 % de la taille du marché Domaine programmable gate array en 2024 ; l'ADAS automobile et l'électrification devraient s'étendre à 13,4 % de TCAC jusqu'en 2030.

Tendances et Insights du Marché mondial Domaine Programmable Gate Array (FPGA)

Analyse d'Impact des Moteurs

| Moteur | (~) % Impact sur les Prévisions TCAC | Pertinence Géographique | Calendrier d'Impact |

|---|---|---|---|

| Demande d'Inférence IA Edge dans les Centres de Données Hyperscale | +2.8% | Mondial, concentré en Amérique du Nord et APAC | Moyen terme (2-4 ans) |

| Transition 5G ORAN Nécessitant une Logique Re-programmable dans les Radios | +2.1% | Mondial, mené par l'Amérique du Nord, l'Europe, l'APAC | Moyen terme (2-4 ans) |

| Besoins de Prototypage Rapide pour les Cycles de Réduction ASIC/SoC (≤7 nm) | +1.7% | Mondial, concentré en Amérique du Nord et APAC | Court terme (≤ 2 ans) |

| Conformité Sécurité Fonctionnelle dans l'Automobile (ISO 26262) | +1.4% | Mondial, mené par l'Europe, l'Amérique du Nord, la Chine | Long terme (≥ 4 ans) |

| Conceptions Tolérantes aux Radiations pour les Constellations du Nouveau Spatial | +0.9% | Mondial, mené par l'Amérique du Nord, l'Europe | Long terme (≥ 4 ans) |

| OEM Chinois de Groupes Motopropulseurs VE Adoptant les eFPGA pour le Contrôle Moteur | +0.6% | APAC, principalement la Chine | Moyen terme (2-4 ans) |

| Source: Mordor Intelligence | |||

Demande d'inférence IA edge dans les centres de données hyperscale

Les opérateurs hyperscale ont déployé des FPGA pour accélérer l'inférence IA une fois que les budgets de latence et de puissance ont commencé à l'emporter sur les exigences de débit brut. Les dispositifs Versal AI Edge Gen 2 d'AMD ont livré jusqu'à 3 × plus de TOPS par watt que les pièces de première génération, permettant l'analyse de vision en temps réel tout en contenant les dépenses opérationnelles. Achronix un rapporté 200 % d'avantages en coût et puissance par rapport aux alternatives GPU lors de l'exécution de modèles de langage large, soulignant l'efficacité FPGA dans les charges de travail limitées par la mémoire. Cette transition un débloqué un modèle de calcul distribué où le traitement d'inférence s'est rapproché des sources de données, allégeant les contraintes de bande passante et les risques de souveraineté des données. L'intégration de HBM sur package et de moteurs IA durcis au sein des familles FPGA leaders un renforcé leur position dans les topologies cloud-edge. Par conséquent, le marché Domaine programmable gate array un trouvé un pilier de croissance durable dans les plans de dépenses d'investissement hyperscale.

Transition 5G ORAN nécessitant une logique re-programmable dans les radios

Les initiatives de réseau d'accès radio ouvert ont poussé les opérateurs à adopter des unités radio agnostiques aux fournisseurs qui pourraient évoluer avec les mises à niveau logicielles plutôt que les remplacements complets. Le portefeuille Agilex d'Intel un utilisé la technologie 10 nm SuperFin pour livrer des radios définies par logiciel qui s'adaptent aux nouvelles versions 5G à un coût total de possession plus faible. Lattice Semiconductor un complété ce matériel avec une pile de référence fournissant la sécurité zéro confiance et le chiffrement en temps réel pour les réseaux désagrégés. Le RFSoC DFE Zynq d'AMD un doublé les performances par watt par rapport aux dispositifs précédents, permettant aux opérateurs de supporter l'opération multi-bande à l'intérieur de têtes radio compactes et contraintes en puissance. La logique flexible un raccourci les cycles de déploiement, un facteur critique alors que les opérateurs mélangeaient la 5G privée, l'accès sans fil fixe et les services mmWave. Cette flexibilité un sécurisé une nouvelle opportunité de volume pour le marché Domaine programmable gate array à travers l'infrastructure télécom.

Besoins de prototypage rapide pour les cycles de réduction ASIC/SoC (≤7 nm)

Le temps entre les nouvelles introductions de processus est tombé en dessous de 24 mois, augmentant la pénalité pour les erreurs de conception. Avant de commander des masques qui coûtent plus de 10 millions USD à 3 nm, les équipes de puces ont utilisé de grands FPGA pour valider le timing, la puissance et le comportement d'interface. Achronix un livré des dispositifs Speedster7t sur TSMC 7 nm qui fournissent une bande passante multi-térabit pour l'émulation réaliste des SoC de nouvelle génération. Le nœud gate-all-around A16 à venir de TSMC promet une autre amélioration de performance de 10 % et 20 % de puissance plus faible, mais augmente également la complexité de vérification, consolidant les plateformes FPGA comme outils de réduction des risques pendant le tape-out. La pratique s'est étendue au-delà des accélérateurs classe serveur dans les ASIC automobiles et industriels à signal mixte, élargissant l'empreinte du marché Domaine programmable gate array à l'intérieur des flux de conception de semiconducteurs.

Conformité sécurité fonctionnelle dans l'automobile (ISO 26262)

L'assistance avancée au conducteur et les groupes motopropulseurs de véhicules électriques ont nécessité un contrôle en temps réel et déterministe qui atteignait l'objectif d'intégrité ASIL D. AMD un fourni des flux de conception et IP certifiés TÜV SÜD qui ont réduit le temps de développement tout en respectant les mandats ISO 26262 et IEC 61508. La suite Libero SoC de Microchip portait des certificats TÜV Rheinland analogues à travers les familles PolarFire et SmartFusion 2, donnant aux tier-ones une seconde source pour la logique critique de sécurité. Subaru un sélectionné Versal AI Edge Gen 2 pour alimenter la vision EyeSight de nouvelle génération, renforçant la confiance OEM dans le calcul adaptatif pour la perception critique de mission. Les longs cycles de vie des produits dans l'automobile multiplient les revenus à vie par gain de conception, soutenant l'expansion à long terme du marché Domaine programmable gate array.

Analyse d'Impact des Contraintes

| Contrainte | (~) % Impact sur les Prévisions TCAC | Pertinence Géographique | Calendrier d'Impact |

|---|---|---|---|

| Contrôles à l'Exportation US-UE sur les FPGA Haute Performance vers la Chine | -1.8% | Mondial, impact concentré sur le commerce Chine-US | Court terme (≤ 2 ans) |

| Volatilité dans l'Allocation de Capacité des Fonderies 300 mm | -1.2% | Mondial, concentré dans les centres de fonderie APAC | Moyen terme (2-4 ans) |

| Consommation de Puissance Statique Plus Élevée vs ASIC Dédié | -0.7% | Mondial, à travers tous les marchés finaux | Long terme (≥ 4 ans) |

| Source: Mordor Intelligence | |||

Contrôles à l'exportation US-UE sur les FPGA haute performance vers la Chine

Les nouvelles règles du Bureau de l'Industrie et de la Sécurité ont supprimé les exemptions civiles pour les expéditions FPGA avancées vers la Chine fin 2023, restreignant les dispositifs adaptés à l'usage IA ou militaire.[2]Federal Register, "Additional Export Controls," federalregister.gov Le changement un forcé AMD-Xilinx et Intel-Altera à arrêter ou filtrer par licence de nombreuses commandes, réduisant les volumes unitaires à court terme. Les fournisseurs chinois comme GOWIN et Pango ont cherché à combler l'écart, mais les obstacles dans les outils de conception, la PI et l'accès aux processus avancés ont limité la substitution immédiate. Les clients multinationaux ont déplacé la production sensible loin de la Chine ou reconfiguré les systèmes pour qualifier les dispositifs non-américains, fracturant les chaînes d'approvisionnement auparavant mondiales. L'incertitude résultante un pesé sur le marché Domaine programmable gate array jusqu'à ce que de nouvelles normes commerciales se stabilisent.

Volatilité dans l'allocation de capacité des fonderies 300 mm

La fabrication FPGA avancée est regroupée chez TSMC et Samsung, dont les décisions de capacité favorisaient souvent les AP de smartphones à gros volume ou les accélérateurs GPU. Quand la demande de puces IA un bondi, les créneaux de wafers pour les produits FPGA à volume moyen se sont resserrés, et les délais ont rallongé. Les fournisseurs ont placé des dépôts pluriannuels ou cherché des sources secondaires, augmentant les besoins en fonds de roulement. Les risques d'horaire ont compliqué les feuilles de route de lancement de produits pour les clients automobiles et industriels qui nécessitent une disponibilité à long terme. Bien que les deux fonderies aient annoncé une expansion agressive, l'apprentissage du rendement aux nouveaux nœuds et la sélection de sites géopolitiques ont maintenu l'approvisionnement fragile, créant une contrainte persistante sur le marché Domaine programmable gate array.

Analyse des Segments

Par Configuration : la dominance haut de gamme fait face aux pressions de coût

Les dispositifs haut de gamme ont détenu 66,5 % de la part de marché Domaine programmable gate array en 2024, reflétant leur rôle central dans l'accélération de centres de données et l'infrastructure 5G. Ces plateformes, dépassant souvent 1 million de cellules logiques, portaient des ASP premium mais livraient une latence déterministe indisponible dans les GPU, préservant leur attrait pour les charges de travail critiques de sécurité unérospatiales et fintech. Les dispositifs milieu et bas de gamme ont exhibé un TCAC de 11,2 % jusqu'en 2030 alors que les fabricants comme Lattice ont livré des pièces optimisées en coût avec des moteurs IA durcis qui répondaient aux budgets de calcul edge. Les outils de conception sont devenus plus intuitifs, permettant aux ingénieurs embarqués d'adopter la logique configurable sans arrière-plan matériel.

La proposition de valeur un évolué alors qu'AMD introduisait Spartan UltraScale+ avec 30 % de puissance plus faible et un compte I/O inégalé, attaquant le milieu de gamme par le haut. Simultanément, les fournisseurs de modules ont fourni des cartes pré-validées qui ont abstrait la planification des broches et la disposition PCB, raccourcissant les cycles de conception. Ces changements devraient comprimer l'écart de prix entre les niveaux, bien que les dispositifs haut de gamme commandent toujours une majorité de la taille du marché Domaine programmable gate array quand de nouvelles normes IA ou réseau émergent que seul le silicium de nœud supérieur peut satisfaire.

Par Architecture : la suprématie SRAM défiée par l'efficacité énergétique

Les solutions basées sur SRAM ont possédé 55,4 % des revenus en 2024 et affiché une perspective de TCAC de 11,8 % grâce aux cycles de reprogrammation illimités et un écosystème logiciel profond. Pourtant, les variantes basées sur flash ont gagné en notoriété dans les wearables et la télématique automobile, où le comportement instant-on est vital. Le RT PolarFire de Microchip un atteint MIL-STD-883 Classe B, offrant 50 % de puissance plus faible que les pièces SRAM équivalentes tout en tolérant 100 krad de radiation. Les plateformes anti-fusible ont soutenu une niche dans l'avionique de défense où la programmabilité unique élimine le risque de falsification.

La portabilité logicielle réduit les barrières historiques, donc les concepteurs peuvent maintenant choisir basé sur la puissance et la sécurité plutôt que la familiarité des outils. Les architectures hétérogènes émergentes intègrent le tissu SRAM avec des domaines non-volatils sur puce, fournissant les meilleures options des deux. Tandis que les dispositifs SRAM continueront à mener les revenus du marché Domaine programmable gate array, les offres flash et anti-fusible devraient découper des parts plus importantes dans les déploiements basse puissance et environnement sévère.

Par Nœud Technologique : les nœuds avancés stimulent l'innovation

La classe 20-90 nm un détenu 49,3 % de la part de marché Domaine programmable gate array en 2024, équilibrant la maturité du rendement et le coût. Cependant, la catégorie ≤16 nm est sur la voie d'un TCAC de 15,1 % alors que l'inférence IA, les interconnexions cohérentes et les 112 G SerDes demandent une densité logique que seuls les nœuds avancés peuvent offrir. AMD un migré certaines lignes Spartan et Versal vers 16 nm pour mélanger l'efficacité coût avec les transceivers modernes. La feuille de route gate-all-around A16 de TSMC promet une autre amélioration de performance par watt que les fournisseurs prévoient d'exploiter pour les produits compatibles PCIe 6.0 et CXL 3.1.

À ≥90 nm, les contrôles industriels hérités et les adaptations militaires favorisent les chaînes d'approvisionnement stables plutôt que la vitesse brute, maintenant ce nœud vivant bien que rétrécissant. Descendre en dessous de 10 nm ajoute des fardeaux de coût de masque et EDA que seuls les plus grands fournisseurs peuvent supporter, élevant les seuils concurrentiels. Cette dynamique pourrait consolider le marché Domaine programmable gate array autour des acteurs avec l'échelle pour sécuriser des wafers coûteux et développer des piles logicielles re-ciblables.

Par Marché Final : l'électrification automobile accélère l'adoption

Les opérateurs de centres de données et cloud ont capturé 29,2 % de la taille du marché Domaine programmable gate array en 2024 en exploitant les accélérateurs reconfigurables pour l'inférence IA et la virtualisation réseau. Les applications automobiles, incluant la vision ADAS et le contrôle d'onduleur, devraient grimper de 13,4 % de TCAC jusqu'en 2030 alors que les OEM intègrent la logique configurable pour satisfaire les algorithmes de sécurité et contrôle moteur en évolution rapide. L'IP FPGA embarquée d'Achronix permet aux constructeurs automobiles d'ajouter des fonctionnalités de dernière étape aux SoC personnalisés, une flexibilité très valorisée dans les longues plateformes véhicule.

Les télécommunications sont restées dynamiques à cause des radios Open RAN recherchant l'agilité multi-bande. L'automatisation industrielle et la robotique se sont appuyées sur les boucles de contrôle moteur déterministes où les FPGA ont remplacé les DSP hérités. La croissance unérospatiale et défense s'est centrée sur la logique tolérante aux radiations pour les satellites en orbite terrestre basse. Les wearables, l'instrumentation de test et l'imagerie médicale ont représenté des verticales plus jeunes qui bénéficient du calcul personnalisé basse puissance. L'étendue des usages souligne que le marché Domaine programmable gate array continue de s'étendre à travers les environnements macro cycliques.

Analyse Géographique

L'Asie-Pacifique un dominé le marché Domaine programmable gate array avec 39,3 % des revenus en 2024 et un montré une perspective de TCAC de 17,1 % jusqu'en 2030. La poussée de la Chine vers l'auto-suffisance en semiconducteurs, mise en évidence par les innovateurs domestiques dans les entraînements de véhicules électriques et les charges utiles satellitaires, un tiré des volumes FPGA significatifs. Taïwan et la Corée du Sud ont fourni la fabrication avancée, tandis que le Japon s'est spécialisé dans les modules automobiles et les sous-systèmes d'automatisation d'usine. Le secteur des services de conception de l'Inde un progressé après que Lattice ait ouvert un centre R&D à Pune, élargissant les pools de talents d'ingénierie.[3]Lattice Semiconductor, "Full Year 2024 Results," latticesemi.com

L'Amérique du Nord un maintenu le leadership dans l'infrastructure de centres de données, l'unérospatiale haute fiabilité et les logiciels EDA. Les hyperscalers ont dirigé de gros budgets d'investissement vers les accélérateurs adaptatifs pour gérer les coûts de services IA, assurant la forte part d'achat de la région. Les révisions de licences d'exportation ont façonné les modèles d'expédition mais ont aussi incité l'investissement domestique dans le emballage avancé et la capacité OSAT qui soutient le marché Domaine programmable gate array.

L'Europe s'est appuyée sur la chaîne d'approvisionnement automobile de l'Allemagne et les fournisseurs d'équipements télécom nordiques. La conformité ISO 26262 un stimulé l'usage dans les véhicules, tandis que les projets de transition énergétique ont créé une demande pour les convertisseurs de puissance à faibles pertes. Les politiques EU Numérique Decade ont encouragé les plateformes de calcul edge souveraines qui favorisent la reconfigurabilité. Bien que l'Amérique du Sud et le Moyen-Orient et l'Afrique détiennent des parts plus petites aujourd'hui, le potentiel de croissance dans l'infrastructure 5G et la modernisation industrielle devrait augmenter leur contribution sur la période de prévision.

Paysage Concurrentiel

Le marché Domaine programmable gate array est resté concentré, avec AMD-Xilinx et Intel-Altera générant toujours la majorité des revenus en 2024. La décision d'Intel en avril 2025 de vendre 51 % d'Altera à Silver Lake pour 8,75 milliards USD visait à accélérer les investissements autonomes et affûter le focus sur les segments d'accélération haut de gamme. AMD un célébré 40 ans d'expéditions FPGA et souligné plus de 3 milliards d'unités cumulatives, exploitant ses familles Versal et Spartan pour répondre aux besoins IA edge et critiques de sécurité.

Lattice Semiconductor un gagné de la traction avec les plateformes Nexus et Avant basse puissance, sécurisant des gains de conception records en IA générative et robotique. Achronix un capturé des parts dans l'IP FPGA embarquée et le réseau multi-térabit, tandis que Microchip un renforcé sa présence en acquérant Neuronix AI Labs pour optimiser les réseaux de neurones conscients de la sparsité sur les dispositifs PolarFire.[4]Microchip Technology, "Acquires Neuronix AI Labs," microchip.com Rapid Silicon et d'autres start-ups ont introduit des chaînes d'outils open-source, mettant la pression des prix sur les suites de conception héritées.

Les alliances stratégiques sont devenues plus importantes que le nombre de transistors seul. Lattice un collaboré avec NVIDIA sur les piles de référence pour l'inférence IA au edge, et AMD un maintenu le rythme grâce aux flux de programmation unifiés Vitis. Les fournisseurs ont aussi investi dans le emballage prêt pour chiplet et les standards d'interconnexion UCIe pour permettre aux clients d'assembler des systèmes hétérogènes sur des substrats communs. De tels mouvements écosystémiques devraient définir le succès futur dans le marché Domaine programmable gate array autant que la densité logique brute.

Leaders de l'Industrie Domaine Programmable Gate Array (FPGA)

-

Advanced Micro Devices, Inc.

-

Lattice Semiconductor Corporation

-

QuickLogic Corporation

-

Intel Corporation

-

Achronix Semiconductor Corporation

- *Avis de non-responsabilité : les principaux acteurs sont triés sans ordre particulier

Développements Récents de l'Industrie

- Juin 2025 : AMD un célébré 40 ans d'innovation FPGA, citant plus de 3 milliards d'expéditions cumulatives à travers les plateformes IA edge automobiles et unérospatiales AMD.

- Mai 2025 : Lattice Semiconductor un rapporté un chiffre d'affaires Q1 2025 de 120,1 millions USD avec des gains de conception records en IA générative, robotique, ADAS automobile et IA edge.

- Avril 2025 : Intel un accepté de vendre 51 % d'Altera à Silver Lake pour 8,75 milliards USD, créant le plus grand fournisseur FPGA autonome.

- Mars 2025 : AMD un introduit la famille Spartan UltraScale+ pour l'usage edge sensible aux coûts, citant 30 % de puissance plus faible et I/O de premier plan.

Portée du Rapport du Marché mondial Domaine Programmable Gate Array (FPGA)

Les FPGA sont des instruments de silicium préfabriqués qui peuvent être programmés électriquement sur le terrain pour devenir presque tout type de circuit ou système numérique. Ils sont un ensemble de blocs logiques configurables (CLB) liés ensemble par des interconnexions programmables. Après fabrication, ils peuvent être reprogrammés pour répondre aux besoins de l'application ou fonctionnalité désirée.

Le marché Domaine programmable gate array (FPGA) est segmenté par configuration (FPGA haut de gamme, FPGA milieu de gamme/FPGA bas de gamme), par architecture (FPGA basé sur SRAM, FPGA basé sur anti-fusible, FPGA basé sur flash), par industrie d'utilisateur final (IT et télécommunication, électronique grand public, automobile, industriel, militaire et unérospatial, autres industries d'utilisateur final), par géographie (Amérique du Nord [États-Unis, Canada], Europe [Allemagne, Royaume-Uni, France, reste de l'Europe], Asie Pacifique [Chine, Japon, Inde, Corée du Sud, reste de l'Asie Pacifique], Amérique Latine [Brésil, Argentine, Mexique, reste de l'Amérique Latine], Moyen-Orient et Afrique [Émirats Arabes Unis, Arabie Saoudite, Afrique du Sud, reste du Moyen-Orient et Afrique]). Les tailles et prévisions de marché sont fournies en termes de valeur en USD pour tous les segments ci-dessus.

| FPGA Haut de Gamme |

| FPGA Milieu de Gamme/Bas de Gamme |

| FPGA basé sur SRAM |

| FPGA basé sur Flash |

| FPGA Anti-fusible |

| ≥90 nm |

| 20-90 nm |

| ≤16 nm |

| Centre de Données et Cloud Computing |

| Télécommunications et Infrastructure 5G |

| Automobile (ADAS, Électrification) |

| Automatisation Industrielle et Robotique |

| Aérospatial et Défense (Avionique, SATCOM) |

| Électronique Grand Public et Wearables |

| Dispositifs de Test, Mesure et Médicaux |

| Amérique du Nord | États-Unis | |

| Canada | ||

| Europe | Allemagne | |

| Royaume-Uni | ||

| France | ||

| Italie | ||

| Pays Nordiques (Suède, Norvège, Finlande, Danemark) | ||

| Reste de l'Europe | ||

| Asie-Pacifique | Chine | |

| Taïwan | ||

| Japon | ||

| Corée du Sud | ||

| Inde | ||

| ASEAN | ||

| Reste de l'Asie-Pacifique | ||

| Amérique du Sud | Mexique | |

| Brésil | ||

| Argentine | ||

| Reste de l'Amérique du Sud | ||

| Moyen-Orient et Afrique | Moyen-Orient | Arabie Saoudite |

| Émirats Arabes Unis | ||

| Turquie | ||

| Reste du Moyen-Orient | ||

| Afrique | Afrique du Sud | |

| Reste de l'Afrique | ||

| Par Configuration | FPGA Haut de Gamme | ||

| FPGA Milieu de Gamme/Bas de Gamme | |||

| Par Architecture | FPGA basé sur SRAM | ||

| FPGA basé sur Flash | |||

| FPGA Anti-fusible | |||

| Par Nœud Technologique | ≥90 nm | ||

| 20-90 nm | |||

| ≤16 nm | |||

| Par Marché Final | Centre de Données et Cloud Computing | ||

| Télécommunications et Infrastructure 5G | |||

| Automobile (ADAS, Électrification) | |||

| Automatisation Industrielle et Robotique | |||

| Aérospatial et Défense (Avionique, SATCOM) | |||

| Électronique Grand Public et Wearables | |||

| Dispositifs de Test, Mesure et Médicaux | |||

| Par Géographie | Amérique du Nord | États-Unis | |

| Canada | |||

| Europe | Allemagne | ||

| Royaume-Uni | |||

| France | |||

| Italie | |||

| Pays Nordiques (Suède, Norvège, Finlande, Danemark) | |||

| Reste de l'Europe | |||

| Asie-Pacifique | Chine | ||

| Taïwan | |||

| Japon | |||

| Corée du Sud | |||

| Inde | |||

| ASEAN | |||

| Reste de l'Asie-Pacifique | |||

| Amérique du Sud | Mexique | ||

| Brésil | |||

| Argentine | |||

| Reste de l'Amérique du Sud | |||

| Moyen-Orient et Afrique | Moyen-Orient | Arabie Saoudite | |

| Émirats Arabes Unis | |||

| Turquie | |||

| Reste du Moyen-Orient | |||

| Afrique | Afrique du Sud | ||

| Reste de l'Afrique | |||

Questions Clés Répondues dans le Rapport

Quelle est la valeur actuelle du marché Domaine programmable gate array ?

Le marché était évalué à 10,08 milliards USD en 2025 et devrait atteindre 16,23 milliards USD d'ici 2030.

Quelle région croît le plus rapidement ?

L'Asie-Pacifique devrait s'étendre à 17,1 % de TCAC jusqu'en 2030 en raison de la demande de groupes motopropulseurs de véhicules électriques et de satellites du nouveau spatial.

Pourquoi les FPGA sont-ils préférés pour l'inférence IA edge ?

Ils livrent des performances par watt plus élevées et une latence déterministe par rapport aux GPU, ce qui améliore le coût total de possession pour les opérateurs hyperscale.

Comment les contrôles à l'exportation affecteront-ils le marché ?

Les restrictions US-UE sur les dispositifs haute performance vers la Chine peuvent réduire les expéditions à court terme, incitant les entreprises chinoises à accélérer les alternatives domestiques.

Quel segment de configuration progresse le plus rapidement ?

Les dispositifs milieu et bas de gamme devraient croître à 11,2 % de TCAC alors que les plateformes optimisées en coût atteignent les applications industrielles et IoT.

Quelle est la signification des nœuds de processus ≤16 nm pour les FPGA ?

Ils permettent une densité logique plus élevée et des interfaces avancées comme PCIe 6.0, qui sont critiques pour l'inférence IA et le traitement bande de base 5G.

Dernière mise à jour de la page le:

-Market-logo.webp)