Marktgröße und Marktanteil für Automatisierte Testausrüstung

Marktanalyse für Automatisierte Testausrüstung von Mordor Intelligence

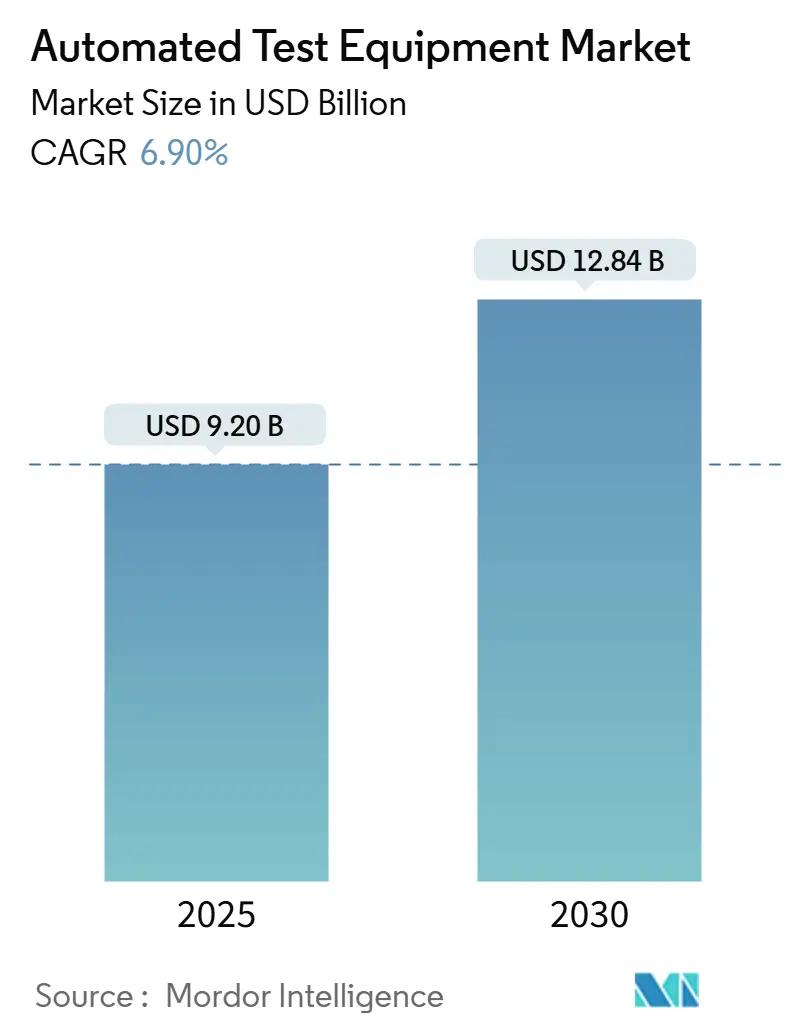

Die Marktgröße für Automatisierte Testausrüstung wurde 2025 auf 9,20 Milliarden USD bewertet und wird voraussichtlich bis 2030 auf 12,84 Milliarden USD ansteigen, mit einer CAGR von 6,9%. Die Nachfrage wird durch die Migration zu Sub-5-nm-Knoten, die Elektrifizierung von Fahrzeugen und die steigende Komplexität von System-in-Package-Designs angetrieben. Hersteller investieren Kapital in ultraleise Plattformen, die unter 10 nV/√Hz messen können, während Leistungsbauelemente-Spezialisten Tester spezifizieren, die sicher über 1.200 V Belastungen anlegen. Ausrüstungsanbieter integrieren gleichzeitig Echtzeitdatenanalyse, um Debug-Zyklen zu verkürzen und das Ausbeute-Lernen zu verbessern. Die Konsolidierung unter führenden Anbietern setzt sich fort, doch innovative Mittelklasse-Unternehmen zielen auf Nischenwachstumsbereiche wie Wafer-Level-Burn-in für KI-Beschleuniger und Validierung der Photonik-Gerätezuverlässigkeit.

Markt für Automatisierte Testausrüstung

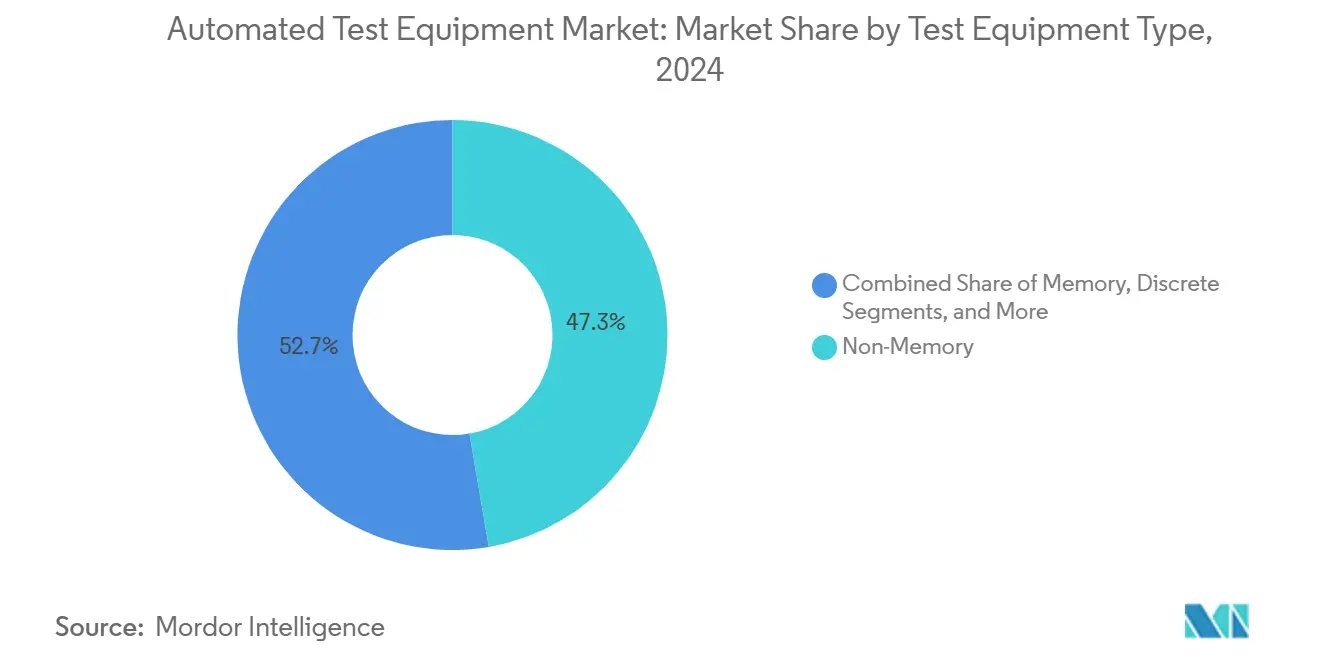

- Nach Testausrüstungstyp führten Nicht-Speicher-Plattformen mit 47,3% des Marktanteils für Automatisierte Testausrüstung im Jahr 2024; System-Level-Tester werden voraussichtlich mit 13,7% CAGR bis 2030 expandieren.

- Nach Komponente eroberten Tester-Mainframes 56,4% Umsatz im Jahr 2024, während System-Level-/Burn-in-Racks für die schnellste 12,9% CAGR bis 2030 positioniert sind.

- Nach Teststufe machten Package-/Finaltests 61,4% Anteil der Marktgröße für Automatisierte Testausrüstung im Jahr 2024 aus; System-Level-Tests werden voraussichtlich mit 13,7% CAGR bis 2030 ansteigen.

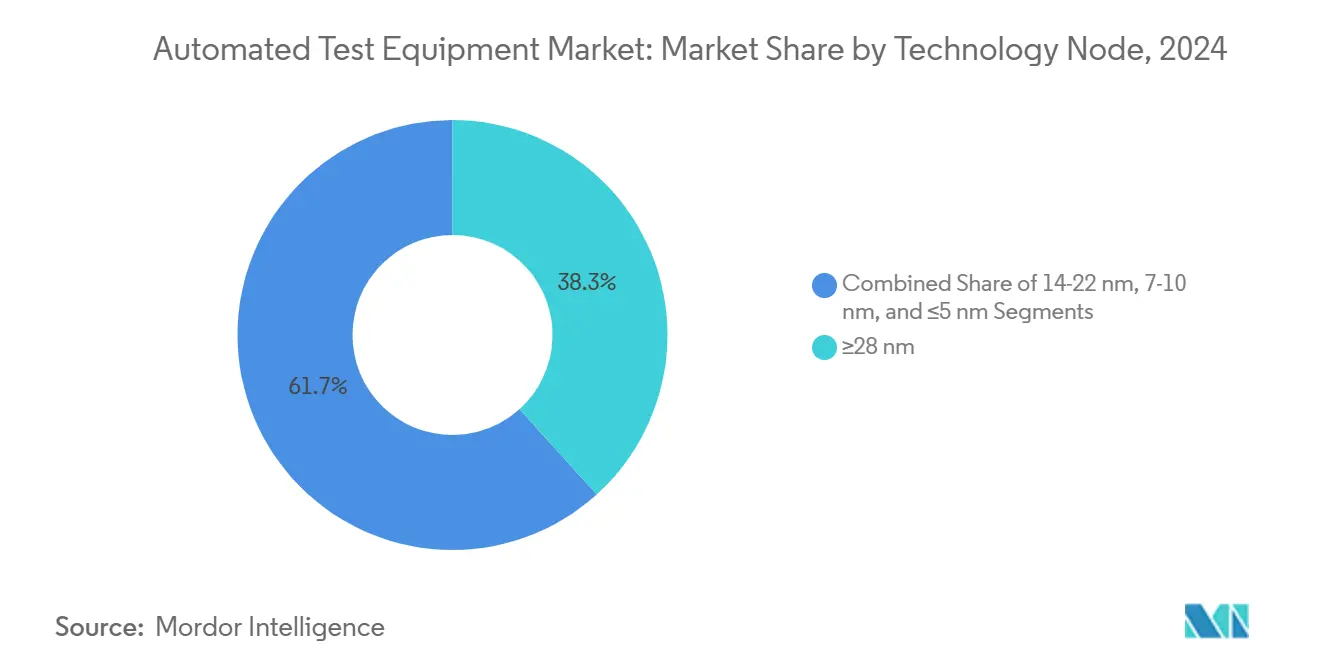

- Nach Technologie-Knoten behielt die ≥28 nm Stufe 38,3% des Umsatzes im Jahr 2024; ≤5 nm Plattformen werden voraussichtlich mit 15,8% CAGR von 2025 bis 2030 ansteigen.

- Nach Endverbraucherindustrie hielt Verbraucherelektronik 39,3% Anteil im Jahr 2024, während Automotive- und EV-Anwendungen mit 12,2% CAGR bis 2030 voranschreiten.

- Nach Geographie kommandierte Asien-Pazifik 62,4% des Umsatzes im Jahr 2024; die Region Naher Osten und Afrika wird voraussichtlich eine 9,1% CAGR zwischen 2025 und 2030 verzeichnen.

Globale Trends und Einblicke des Marktes für Automatisierte Testausrüstung

Treiber-Impact-Analyse

| Treiber | (~) % Impact auf CAGR-Prognose | Geografische Relevanz | Impact-Zeitrahmen |

|---|---|---|---|

| Schrumpfende <7 nm Knoten Erfordern Ultra-Leise ATE | +2.1% | Asien-Pazifik, Nordamerika | Mittelfristig (2-4 Jahre) |

| Automotive Funktionssicherheits-IC-Tests (ISO 26262) Anstieg in EU | +1.8% | Europa, Nordamerika | Langfristig (≥ 4 Jahre) |

| SiC / GaN Leistungsbauelemente Treiben Hochspannungs-Diskret-ATE | +1.5% | Global, mit Schwerpunkt auf Asien-Pazifik | Mittelfristig (2-4 Jahre) |

| Wachstum von System-in-Package (SiP) Befeuert System-Level-Tester | +1.3% | Asien-Pazifik, Nordamerika | Mittelfristig (2-4 Jahre) |

| 5G / 6G RF-Frontend-Komplexität in Asien | +1.0% | Asien-Pazifik, Nordamerika | Kurzfristig (≤ 2 Jahre) |

| Reshoring-Anreize (US CHIPS, EU Chips Acts) Erweitern Testkapazität | +0.8% | Nordamerika, Europa | Langfristig (≥ 4 Jahre) |

| Quelle: Mordor Intelligence | |||

| Quelle: Mordor Intelligence | |||

Schrumpfende <7 nm Knoten Erfordern Ultra-Leise ATE

Sub-7 nm Produktionsanläufe in Taiwan und Südkorea haben Messgenauigkeit unter 10 nV/√Hz und Pikosekunden-Level-Timing erforderlich gemacht. Führende Foundries haben mit der Qualifikation neuer vektor-paralleler Architekturen reagiert, die Übersprechen durch verbesserte Abschirmung und optimierte Erdungsreferenzierung unterdrücken. Tool-Anbieter paaren diese Designs mit maschinellem-Lernen-gesteuerten Mustergenerierung, um Charakterisierungsschleifen zu komprimieren, ein Feature, das jetzt Standard auf Flaggschiff-SoC-Plattformen ist.[1]Nanomaterials Editorial Board, "Advanced CMOS Technology," MDPI, mdpi.com

Automotive Funktionssicherheits-IC-Tests Anstieg (ISO 26262)

Europäische Tier-1-Halbleiteranbieter erhöhten Deployments von fehlerinjektionsfähigen Testern um 34% zwischen 2024 und 2025. Die Ausrüstung führt Hunderte von Sicherheitsziel-Permutationen aus und bildet Ergebnisse zurück auf Anforderungs-Rückverfolgbarkeits-Matrizen ab. Integration mit Hardware-in-the-Loop-Bänken ermöglicht simultane Verifikation von Antriebsstrang-Invertern, Radarsensoren und MCU-Subsystemen und gewährleistet ASIL-D-Compliance im Maßstab.

SiC / GaN Leistungsbauelemente Treiben Hochspannungs-Diskret-ATE

Wide-Bandgap-Komponenten für Traktions-Inverter und Solar-Inverter erfordern Charakterisierung bei bis zu 1.200 V und 150 °C. Neue diskrete Tester integrieren isolierte Kelvin-Verbindungen, automatisiertes Hot-Switch-Cycling und kalorimetrische Thermal-Impedanz-Extraktion. Zuverlässigkeitsprotokolle, die aus GaN-Lebensdauerstudien abgeleitet wurden, bilden jetzt Standard-Burn-in-Rezepte für Automotive-Qualifikation.

Wachstum von System-in-Package Befeuert System-Level-Tester

Heterogene Packages, die RF-Transceiver, SRAM-Stacks und PMICs mischen, erfordern gleichzeitige Mixed-Domain-Evaluierung. System-Level-Racks integrieren daher Multi-Site-RF-Shield-Boxen, High-Speed-Digital-Interfaces und Thermal-Stream-Air-Hooks innerhalb eines einzigen Rahmens. Smartphone- und IoT-OEMs haben über 40% des Final-Test-Volumens auf solche Racks seit Ende 2024 migriert, um latente Montagefehler zu erfassen, die parametrische Screens verpassen.

Hemmnisse-Impact-Analyse

| Hemmnis | (~) % Impact auf CAGR-Prognose | Geografische Relevanz | Impact-Zeitrahmen |

|---|---|---|---|

| Hohe Kapitalintensität und Lange Amortisation für Sub-5 nm Tester | -1.2% | Global | Mittelfristig (2-4 Jahre) |

| On-Chip BIST Reduziert Externe Digital-ATE-Nachfrage | -0.9% | Global | Langfristig (≥ 4 Jahre) |

| Begrenzte Inter-Vendor Interface-Interoperabilität | -0.7% | Global | Mittelfristig (2-4 Jahre) |

| Zyklische Halbleiter-CAPEX-Kürzungen | -0.8% | Global, mit Schwerpunkt auf Asien-Pazifik | Kurzfristig (≤ 2 Jahre) |

| Quelle: Mordor Intelligence | |||

| Quelle: Mordor Intelligence | |||

Hohe Kapitalintensität und Lange Amortisation für Sub-5 nm Tester

Plattformpreise stiegen um 35% gegenüber der 7 nm Generation und streckten ROI über fünf Jahre hinaus für Mittelklasse-Fabs. Der Bedarf für ultrastabile Low-k-Dielektrikum-Sondierung, erweiterte thermische Regulierung und Multi-Terabit-Musterspeicher erhöht sowohl Akquisitions- als auch Servicekosten und dämpft Adoptionsraten unter kleineren Foundries.

On-Chip BIST Reduziert Externe Digital-ATE-Nachfrage

Moderne SoCs beinhalten routinemäßig Logik- und Speicher-Selbsttest-Engines, die 98% Fehlerabdeckung während Wafer-Sort liefern. Folglich fielen wafer-level externe Vektorzahlen für digitale Muster 2024 zweistellig, was Capex zu RF-, Mixed-Signal- und Leistungsbauelemente-Bänken umleitete, die außerhalb des Bereichs eingebetteter Testlogik bleiben.

Segmentanalyse

Nach Testausrüstungstyp: Nicht-Speicher-Plattformen Verankern Umsatz

Nicht-Speicher-Tester, die Logik-, SoC- und RF-Geräte abdecken, eroberten 47,3% des Marktanteils für Automatisierte Testausrüstung im Jahr 2024.[2]Advantest Communications, "Advantest Forms Strategic Partnerships with FormFactor and Technoprobe," Advantest, advantest.com Ihre Dominanz entstand durch Nachfrage zur Screenung von KI-Prozessoren, 5G-Transceivern und Automotive-Domain-Controllern. Anbieter hoben Vektorgeschwindigkeiten über 5 Gbps pro Pin und fügten Sub-Terahertz-RF-Optionen hinzu, um gemischte Workloads zu bedienen. Maschinelles-Lernen-Mustergenerierung verkürzte Zykluszeiten, passend für Smartphone- und Rechenzentrum-Volumenläufe. Integrierte Analytik verknüpfte Ausfallsignaturen mit Layout-Blöcken, reduzierte Respins und zementierte die Umsatzführung des Segments.

Test-Handler bilden die am schnellsten wachsende Kategorie mit einer prognostizierten 11,4% CAGR von 2025 bis 2030, da Automotive- und Leistungslinien höheren Durchsatz und engere thermische Kontrolle suchen. Die Marktgröße für Automatisierte Testausrüstung für Handler erweitert sich, da Fabs Multi-Zonen-Platten und aktive Vibrationsdämpfung spezifizieren, um Wide-Bandgap-Geräte bei 175 °C zu qualifizieren. Erweiterte Robotik bewegt jetzt fragile 3D-gestapelte Packages ohne Mikro-Rissbildung und erhöht die Erstpass-Ausbeute in SiP-Montage. Predictive-Maintenance-Software kürzt ferner Ausfallzeiten und stützt die zweistellige Trajektorie des Segments.

Notiz: Segmentanteile aller individuellen Segmente verfügbar beim Berichtskauf

Nach Komponente: System-Level-Racks Gewinnen Momentum

Tester-Mainframes hielten 56,4% Umsatz im Jahr 2024, gestützt durch Upgrades, die Mustergenerierungs-Acceleratoren und Cloud-verbundene Analytik-Module integrieren. Interface-Boards verwenden jetzt verlustfreie Laminate zur Unterstützung von 70 Gbps differenziellen Lanes, während aktive Thermal-Control-Sockets Sperrschichttemperaturen innerhalb ±0,5 °C stabilisieren.

Die Marktgröße für Automatisierte Testausrüstung für System-Level-/Burn-in-Racks wird voraussichtlich mit 12,9% CAGR steigen, angetrieben durch KI-Beschleuniger-Wafer-Level-Stress-Tests und Photonik-Montage-Validierung. Prober-Innovationen adressieren schrumpfende Pad-Pitches durch MEMS-Feder-Sonden-Karten mit 3 μm Positionsgenauigkeit. Handler-Designs fügen Multi-Zonen-Kühlplatten hinzu, um erweiterte Temperatur-Test-Matrizen zu entsprechen, die von sicherheitskritischen Automotive-ICs gefordert werden.

Nach Teststufe: System-Level-Validierung Redefiniert Qualitätsgates

Package-/Final-Bänke repräsentierten 61,4% des Umsatzes im Jahr 2024 und verifizierten Power-On-Funktionalität, Standby-Leckage und RF-Linearität vor Versand. Smart-Load-Boxen koppeln jetzt mit automatisierter optischer Inspektion zur Kennzeichnung von Package-Koplanarität-Anomalien.

System-Level-Linien liefern die schnellste 13,7% CAGR, da OEMs auf Board-Level-Power-Cycling, Boot-Zeit-Checks und Artificial-Traffic-Stress-Suiten bestehen. Der Marktgrößengewinn für Automatisierte Testausrüstung ist am sichtbarsten in Smartphone- und EV-Inverter-Kontrollmodulen. Wafer-Sonden-Stationen setzen sich als frühe Ausbeutemonitor fort, ausgestattet mit aktiven vibrationsdämpfenden Stufen zum Schutz fragiler Mikro-Bump-Arrays. Burn-in-Öfen erweitern Verweiltemperaturen zu 175 °C für GaN-HEMT-Ausdauerstudien.

Nach Technologie-Knoten: Sub-5 nm Treibt Präzision

Die ≥28 nm Kohorte produzierte 2024 noch 38,3% des Umsatzes, favorisiert für kostensensitive industrielle IoT-Teile. Der Marktanteil für Automatisierte Testausrüstung für ≤5 nm Geräte steigt schnell; diese Knotengruppe wird eine 15,8% CAGR sehen und erfordert Pikosekunden-Jitter-Messung und Sub-10 nV/√Hz Rauschböden.

Zwischen 7 nm und 10 nm müssen Tester höhere Power-Integrity-Margen gegen schrumpfende Kontaktfenster versöhnen. Pattern-Burst-Kompression und intelligente Ausrichtungsalgorithmen reduzieren Testzeit-Overheads und machen wirtschaftlichen Sinn für Mid-Range-CPUs und GPUs. Fabless-Kunden fordern Upgrade-Pfad-Garantien für zukünftige 3 nm Kompatibilität und drängen Anbieter zu modularen Timing-Engines und feldaustauschbaren analogen Front-Ends.

Notiz: Segmentanteile aller individuellen Segmente verfügbar beim Berichtskauf

Nach Endverbraucherindustrie: Automotive Führt CAGR An

Verbraucherelektronik blieb 2024 die größte Umsatzquelle mit 39,3%, wobei Smartphones allein Multi-Site-Test-Concurrency-Upgrades antrieben. Die Marktgröße für Automatisierte Testausrüstung, die an Automotive- und EV-Elektronik gebunden ist, wird mit 12,2% CAGR wachsen, da ADAS-, Traktions-Inverter- und Batteriemanagementsystem-IC-Inhalte skalieren. ISO 26262 Arbeitsprodukte beinhalten Strukturabdeckungsberichte, die direkt von Tester-Datenbanken abgeleitet werden und Design-for-Test-Kooperation zwischen IDM- und EMS-Partnern verstärken.

Telekommunikationsinfrastruktur-Tester integrieren jetzt Beamforming-Kalibrierungsschleifen zur Validierung von Massive-MIMO-Front-Ends, während Luft- und Raumfahrtkunden strahlungsgehärtete Testabläufe spezifizieren, die nach JESD57 zertifiziert sind. Medizingerätehersteller verlassen sich auf erweiterte Burn-ins bei niedrigen Leckströmen, um Implantat-Langlebigkeit zu garantieren und drängen Tester-Anbieter zur Lieferung von Femtoamp-Level-Messmodulen.

Geografieanalyse

Asien-Pazifik führte den Markt für Automatisierte Testausrüstung mit 62,4% Umsatz im Jahr 2024 an, unterstützt durch dichte Cluster von 300 mm Fabs in Taiwan, Südkorea, Festlandchina und Japan. Foundry-Erweiterungen bei 3 nm und 2 nm Knoten lösten entsprechende Investitionen in ultra-leise Final-Test-Linien in den Provinzen Hsinchu und Gyeonggi aus, während chinesische IDMs die inländische Prober- und Handler-Beschaffung beschleunigten, um Exportbeschränkungen auszugleichen.[3]SEMI Industry Research, "Eighteen New Semiconductor Fabs to Start Construction in 2025," SEMI, semi.org

Nordamerika rangierte an zweiter Stelle, da CHIPS Act-Anreize mehrere Green-Field-Fabs in Arizona, Texas und New York vorantrieben und frische Nachfrage für Package-/Final- und System-Level-Stationen schufen, die Ambient-minus-40 °C Stressprofile bewältigen können; Mexikos Automotive-Elektronik-Korridor rüstete ebenfalls Handler-Flotten auf, um nahegelegene Fahrzeugwerke zu bedienen.

Europas Anteil stieg aufgrund der Funktionssicherheits-IC-Produktion, wobei Deutschland und Frankreich Testkapazität für ADAS-Prozessoren und Leistungsmodule erweiterten, während der 43 Milliarden Euro European Chips Act darauf abzielte, die regionale Fertigungsleistung bis 2030 zu verdoppeln und parallele Tester-Bestellungen anzuspornen.

Der Nahe Osten und Afrika werden voraussichtlich von 2025 bis 2030 eine 9,1% CAGR verzeichnen, da die VAE und Saudi-Arabien Diversifikationsfonds in lokale RF-Frontend-Ventures lenken; afrikanische Hubs in Südafrika und Nigeria haben begonnen, Mixed-Signal-Bänke für regionale Fabless-Start-ups zu qualifizieren.

Wettbewerbslandschaft

Advantest und Teradyne hielten gemeinsam einen signifikanten Umsatzanteil von über 50% des globalen Umsatzes im Jahr 2024 und nutzten tiefe Forschungs- und Entwicklungspipelines, große installierte Basen und breite Service-Fußabdrücke. Advantest erweiterte seine V93000 EXA Scale-Architektur mit maschinellem-Lernen-aktivierter Ausfallsignatur-Analytik, während Teradyne neue parallele Stromressourcen zu seinem UltraFLEX Plus für hochstrom-KI-Beschleuniger hinzufügte.

Cohu konzentrierte sich auf wiederkehrende Umsätze und wuchs Services und Verbrauchsmaterialien auf 65% des 2024er Umsatzes, da seine Diamondx-Plattform Mid-Range-MCU-Konten penetrierte. FormFactor und Technoprobe bildeten Sondenkarten-Allianzen mit Advantest zur Beschleunigung von Wafer-Level-Lösungen für 3D-gestapelte DRAM. Nischen-Anbieter wie Chroma und AccelRF eroberten Positionen in Photonik-Burn-in bzw. RF-Zuverlässigkeit und gewannen Auszeichnungen und Kundenempfehlungen.[4]Chroma Product Marketing, "Chroma Photonic IC Burn-in and Reliability Test System Wins 2024 TOSIA Award," Chroma, chromaate.com

Aufkommende Marktteilnehmer adressieren Lücken in Silizium-Photonik, CMOS-Bildsensor-HDR-Tests und kryogene Qubit-Validierung. Strategische Konsolidierung wird voraussichtlich fortgesetzt, da etablierte Unternehmen spezialisierte IP akquirieren, insbesondere um KI-getriebene Testprogramm-Optimierung und cyber-sichere Datenpipelines.

Branchenführer für Automatisierte Testausrüstung

-

Advantest Corporation

-

Teradyne Inc.

-

Cohu Inc.

-

Chroma ATE Inc.

-

National Instruments (NI)

- *Haftungsausschluss: Hauptakteure in keiner bestimmten Reihenfolge sortiert

Aktuelle Branchenentwicklungen

- Mai 2025: Advantest enthüllte SiConic™ SoC-Validierung, V93000 EXA Scale-Upgrades und ACS-Echtzeitdaten-Tools auf der SEMICON Southeast Asia 2025.

- April 2025: Technoprobes Capital Market Day skizzierte Einstieg in High Bandwidth Memory-Sondenkarten und Final-Test-Erweiterung zur Bedienung von KI-Workloads.

- März 2025: Keysight Technologies und Analog Devices demonstrierten 6G FR3-Frontend-Charakterisierung mit PNA-X-Analysatoren und einem vollständigen Signalketten-Referenzdesign.

- März 2025: Chromas 58604 Photonic IC Burn-in and Reliability Test System gewann den 2024 TOSIA Award für herausragende Produktinnovation.

Globaler Marktberichtsumfang für Automatisierte Testausrüstung

Automatisierte Testausrüstung (ATE) wird hauptsächlich zur Überprüfung von Gerätefehlern und zur Gewährleistung ihrer Qualität eingesetzt. Alle Hersteller elektronischer Geräte müssen die jeweiligen Systeme narrensicher machen, und zu diesem Zweck benötigen sie Testmechanismen vor dem Einsatz.

Der Umfang der Studie umfasst Marktgrößenschätzung unter Berücksichtigung der Umsätze aus verschiedenen Arten von automatisierter Testausrüstung. Der Markt ist nach Endverbraucherindustrien segmentiert, wie Luft- und Raumfahrt und Verteidigung, Verbraucherelektronik, IT und Telekommunikation, Automotive, Gesundheitswesen und andere Industrien. Darüber hinaus ist der Studienumfang nach Arten von Testausrüstung und geografischen Segmenten unterteilt. Die Bewertung der Auswirkungen von COVID-19 wurde ebenfalls in der Studie abgedeckt.

Für jedes Segment wurden Marktdimensionierung und Prognosen auf Basis von Wert (in Millionen USD) und Volumen (in metrischen Tonnen) bereitgestellt.

| Speicher | DRAM |

| Flash | |

| Nicht-Speicher | Logik / SoC |

| Mixed-Signal und Analog | |

| RF | |

| Diskret | |

| Test-Handler |

| Tester (Kernsystem) |

| Handler |

| Prober |

| Last-/Interface-Boards und Sockets |

| Wafer-Sonden-Test |

| Package- / Final-Test |

| System-Level- / Burn-in-Test |

| ≥28 nm |

| 14-22 nm |

| 7-10 nm |

| ≤5 nm |

| Verbraucherelektronik |

| IT und Telekommunikation |

| Automotive und EV |

| Luft- und Raumfahrt und Verteidigung |

| Gesundheitsgeräte |

| Industrie und Energie |

| Nordamerika | Vereinigte Staaten | |

| Kanada | ||

| Mexiko | ||

| Südamerika | Brasilien | |

| Argentinien | ||

| Rest von Südamerika | ||

| Europa | Deutschland | |

| Vereinigtes Königreich | ||

| Frankreich | ||

| Italien | ||

| Nordics (Schweden, Finnland, Norwegen, Dänemark) | ||

| Rest von Europa | ||

| Asien-Pazifik | China | |

| Japan | ||

| Südkorea | ||

| Taiwan | ||

| Rest von Asien-Pazifik | ||

| Naher Osten und Afrika | Naher Osten | Saudi-Arabien |

| Vereinigte Arabische Emirate | ||

| Türkei | ||

| Rest des Nahen Ostens | ||

| Afrika | Südafrika | |

| Nigeria | ||

| Rest von Afrika | ||

| Nach Testausrüstungstyp | Speicher | DRAM | |

| Flash | |||

| Nicht-Speicher | Logik / SoC | ||

| Mixed-Signal und Analog | |||

| RF | |||

| Diskret | |||

| Test-Handler | |||

| Nach Komponente | Tester (Kernsystem) | ||

| Handler | |||

| Prober | |||

| Last-/Interface-Boards und Sockets | |||

| Nach Teststufe | Wafer-Sonden-Test | ||

| Package- / Final-Test | |||

| System-Level- / Burn-in-Test | |||

| Nach Technologie-Knoten | ≥28 nm | ||

| 14-22 nm | |||

| 7-10 nm | |||

| ≤5 nm | |||

| Nach Endverbraucherindustrie | Verbraucherelektronik | ||

| IT und Telekommunikation | |||

| Automotive und EV | |||

| Luft- und Raumfahrt und Verteidigung | |||

| Gesundheitsgeräte | |||

| Industrie und Energie | |||

| Nach Geographie | Nordamerika | Vereinigte Staaten | |

| Kanada | |||

| Mexiko | |||

| Südamerika | Brasilien | ||

| Argentinien | |||

| Rest von Südamerika | |||

| Europa | Deutschland | ||

| Vereinigtes Königreich | |||

| Frankreich | |||

| Italien | |||

| Nordics (Schweden, Finnland, Norwegen, Dänemark) | |||

| Rest von Europa | |||

| Asien-Pazifik | China | ||

| Japan | |||

| Südkorea | |||

| Taiwan | |||

| Rest von Asien-Pazifik | |||

| Naher Osten und Afrika | Naher Osten | Saudi-Arabien | |

| Vereinigte Arabische Emirate | |||

| Türkei | |||

| Rest des Nahen Ostens | |||

| Afrika | Südafrika | ||

| Nigeria | |||

| Rest von Afrika | |||

Schlüsselfragen, die im Bericht beantwortet werden

Was treibt den starken Anstieg bei System-Level-Testern?

System-in-Package-Adoption und Automotive-Funktionssicherheits-Mandate erfordern vollständige Gerätvalidierung unter realen Betriebsbedingungen und treiben System-Level-Tester-Nachfrage zu einer 13,7% CAGR bis 2030.

Wie bedeutsam ist Asien-Pazifik für den Markt für Automatisierte Testausrüstung?

Asien-Pazifik hielt 62,4% des globalen Umsatzes im Jahr 2024, verankert durch führende Fabs in Taiwan, Südkorea, China und Japan.

Welches Technologie-Knoten-Segment expandiert am schnellsten?

≤5 nm Geräte führen mit einer 15,8% CAGR-Prognose von 2025 bis 2030, was schnelle Adoption für KI- und Hochleistungscomputing-Chips widerspiegelt.

Warum beeinflussen SiC- und GaN-Geräte ATE-Spezifikationen?

Diese Wide-Bandgap-Halbleiter erfordern Testspannungen bis zu 1.200 V und erhöhte Temperaturen und machen spezialisierte Hochspannungs-Diskret-Tester mit erweiterten Sicherheitsmerkmalen erforderlich.

Welches Hemmnis könnte das Wachstum des Marktes für Automatisierte Testausrüstung verlangsamen?

Hohe Kapitalintensität für Sub-5 nm-fähige Plattformen verlängert ROI über fünf Jahre hinaus und begrenzt Kaufkraft für kleinere Fabs.

Seite zuletzt aktualisiert am: